ZHCSFG2C May 2016 – December 2016 ADC32RF45

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Analog Inputs

- 8.3.2 Clock Input

- 8.3.3 SYSREF Input

- 8.3.4 DDC Block

- 8.3.5 NCO Switching

- 8.3.6 SerDes Transmitter Interface

- 8.3.7 Eye Diagrams

- 8.3.8 Alarm Outputs: Power Detectors for AGC Support

- 8.3.9 Power-Down Mode

- 8.3.10 ADC Test Pattern

- 8.4

Device Functional Modes

- 8.4.1 Device Configuration

- 8.4.2

JESD204B Interface

- 8.4.2.1 JESD204B Initial Lane Alignment (ILA)

- 8.4.2.2 JESD204B Frame Assembly

- 8.4.2.3 JESD204B Frame Assembly in Bypass Mode

- 8.4.2.4 JESD204B Frame Assembly with Decimation (Single-Band DDC): Complex Output

- 8.4.2.5 JESD204B Frame Assembly with Decimation (Single-Band DDC): Real Output

- 8.4.2.6 JESD204B Frame Assembly with Decimation (Single-Band DDC): Real Output

- 8.4.2.7 JESD204B Frame Assembly with Decimation (Dual-Band DDC): Complex Output

- 8.4.2.8 JESD204B Frame Assembly with Decimation (Dual-Band DDC): Real Output

- 8.4.3 Serial Interface

- 8.5

Register Maps

- 8.5.1 Example Register Writes

- 8.5.2

Register Descriptions

- 8.5.2.1

General Registers

- 8.5.2.1.1 Register 000h (address = 000h), General Registers

- 8.5.2.1.2 Register 002h (address = 002h), General Registers

- 8.5.2.1.3 Register 003h (address = 003h), General Registers

- 8.5.2.1.4 Register 004h (address = 004h), General Registers

- 8.5.2.1.5 Register 010h (address = 010h), General Registers

- 8.5.2.1.6 Register 011h (address = 011h), General Registers

- 8.5.2.1.7 Register 012h (address = 012h), General Registers

- 8.5.2.1

General Registers

- 8.5.3

Master Page (M = 0)

- 8.5.3.1 Register 020h (address = 020h), Master Page

- 8.5.3.2 Register 032h (address = 032h), Master Page

- 8.5.3.3 Register 039h (address = 039h), Master Page

- 8.5.3.4 Register 03Ch (address = 03Ch), Master Page

- 8.5.3.5 Register 05Ah (address = 05Ah), Master Page

- 8.5.3.6 Register 03Dh (address = 3Dh), Master Page

- 8.5.3.7 Register 057h (address = 057h), Master Page

- 8.5.3.8 Register 058h (address = 058h), Master Page

- 8.5.4 ADC Page (FFh, M = 0)

- 8.5.5 Digital Function Page (610000h, M = 1 for Channel A and 610100h, M = 1 for Channel B)

- 8.5.6 Offset Corr Page Channel A (610000h, M = 1)

- 8.5.7 Offset Corr Page Channel B (610000h, M = 1)

- 8.5.8 Digital Gain Page (610005h, M = 1 for Channel A and 610105h, M = 1 for Channel B)

- 8.5.9 Main Digital Page Channel A (680000h, M = 1)

- 8.5.10 Main Digital Page Channel B (680001h, M = 1)

- 8.5.11

JESD Digital Page (6900h, M = 1)

- 8.5.11.1 Register 001h (address = 001h), JESD Digital Page

- 8.5.11.2 Register 002h (address = 002h ), JESD Digital Page

- 8.5.11.3 Register 003h (address = 003h), JESD Digital Page

- 8.5.11.4 Register 004h (address = 004h), JESD Digital Page

- 8.5.11.5 Register 006h (address = 006h), JESD Digital Page

- 8.5.11.6 Register 007h (address = 007h), JESD Digital Page

- 8.5.11.7 Register 016h (address = 016h), JESD Digital Page

- 8.5.11.8 Register 017h (address = 017h), JESD Digital Page

- 8.5.11.9 Register 032h-035h (address = 032h-035h), JESD Digital Page

- 8.5.11.10 Register 036h (address = 036h), JESD Digital Page

- 8.5.11.11 Register 037h (address = 037h), JESD Digital Page

- 8.5.11.12 Register 03Eh (address = 03Eh), JESD Digital Page

- 8.5.12

Decimation Filter Page

- 8.5.12.1 Register 000h (address = 000h), Decimation Filter Page

- 8.5.12.2 Register 001h (address = 001h), Decimation Filter Page

- 8.5.12.3 Register 002h (address = 2h), Decimation Filter Page

- 8.5.12.4 Register 005h (address = 005h), Decimation Filter Page

- 8.5.12.5 Register 006h (address = 006h), Decimation Filter Page

- 8.5.12.6 Register 007h (address = 007h), Decimation Filter Page

- 8.5.12.7 Register 008h (address = 008h), Decimation Filter Page

- 8.5.12.8 Register 009h (address = 009h), Decimation Filter Page

- 8.5.12.9 Register 00Ah (address = 00Ah), Decimation Filter Page

- 8.5.12.10 Register 00Bh (address = 00Bh), Decimation Filter Page

- 8.5.12.11 Register 00Ch (address = 00Ch), Decimation Filter Page

- 8.5.12.12 Register 00Dh (address = 00Dh), Decimation Filter Page

- 8.5.12.13 Register 00Eh (address = 00Eh), Decimation Filter Page

- 8.5.12.14 Register 00Fh (address = 00Fh), Decimation Filter Page

- 8.5.12.15 Register 010h (address = 010h), Decimation Filter Page

- 8.5.12.16 Register 011h (address = 011h), Decimation Filter Page

- 8.5.12.17 Register 014h (address = 014h), Decimation Filter Page

- 8.5.12.18 Register 016h (address = 016h), Decimation Filter Page

- 8.5.12.19 Register 01Eh (address = 01Eh), Decimation Filter Page

- 8.5.12.20 Register 01Fh (address = 01Fh), Decimation Filter Page

- 8.5.12.21 Register 033h-036h (address = 033h-036h), Decimation Filter Page

- 8.5.12.22 Register 037h (address = 037h), Decimation Filter Page

- 8.5.12.23 Register 03Ah (address = 03Ah), Decimation Filter Page

- 8.5.13

Power Detector Page

- 8.5.13.1 Register 000h (address = 000h), Power Detector Page

- 8.5.13.2 Register 001h-002h (address = 001h-002h), Power Detector Page

- 8.5.13.3 Register 003h (address = 003h), Power Detector Page

- 8.5.13.4 Register 007h-00Ah (address = 007h-00Ah), Power Detector Page

- 8.5.13.5 Register 00Bh-00Ch (address = 00Bh-00Ch), Power Detector Page

- 8.5.13.6 Register 00Dh (address = 00Dh), Power Detector Page

- 8.5.13.7 Register 00Eh (address = 00Eh), Power Detector Page

- 8.5.13.8 Register 00Fh, 010h-012h, and 016h-019h (address = 00Fh, 010h-012h, and 016h-019h), Power Detector Page

- 8.5.13.9 Register 013h-01Ah (address = 013h-01Ah), Power Detector Page

- 8.5.13.10 Register 01Dh-01Eh (address = 01Dh-01Eh), Power Detector Page

- 8.5.13.11 Register 020h (address = 020h), Power Detector Page

- 8.5.13.12 Register 021h (address = 021h), Power Detector Page

- 8.5.13.13 Register 022h-025h (address = 022h-025h), Power Detector Page

- 8.5.13.14 Register 027h (address = 027h), Power Detector Page

- 8.5.13.15 Register 02Bh (address = 02Bh), Power Detector Page

- 8.5.13.16 Register 032h-035h (address = 032h-035h), Power Detector Page

- 8.5.13.17 Register 037h (address = 037h), Power Detector Page

- 8.5.13.18 Register 038h (address = 038h), Power Detector Page

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

8 Detailed Description

8.1 Overview

The ADC32RF45 is a dual, 14-bit, 3-GSPS, analog-to-digital converter (ADC) followed by a multi-band digital down-converter (DDC) that can be bypassed, and a back-end JESD204B digital interface.

The ADCs are preceded by an input buffer and on-chip termination to provide a uniform input impedance over a large input frequency range. Furthermore, an internal differential clamping circuit provides first-level protection against overvoltage conditions. Each ADC channel is internally interleaved four times and equipped with background, analog and digital, and interleaving correction.

The on-chip DDC enables single- or dual-band internal processing to pre-select and filter smaller bands of interest and also reduces the digital output data traffic. Each DDC is equipped with up to three independent,

16-bit numerically-controlled oscillators (NCOs) for phase coherent frequency hopping; the NCOs can be controlled through the SPI or GPIO pins. The ADC32RF45 also provides three different power detectors on-chip with alarm outputs in order to support external automatic gain control (AGC) loops.

The processed data are passed into the JESD204B interface where the data are framed, encoded, serialized, and output on one to four lanes per channel, depending on the ADC sampling rate and decimation. The CLKIN, SYSREF, and SYNCB inputs provide the device clock and the SYSREF and SYNCB signals to the JESD204B interface that are used to derive the internal local frame and local multiframe clocks and establish the serial link. All features of the ADC32RF45 are configurable through the SPI.

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 Analog Inputs

The ADC32RF45 analog signal inputs are designed to be driven differentially. The analog input pins have internal analog buffers that drive the sampling circuit. The ADC32RF45 provides on-chip, differential termination to minimize reflections. The buffer also helps isolate the external driving circuit from the internal switching currents of the sampling circuit, thus resulting in a more constant SFDR performance across input frequencies.

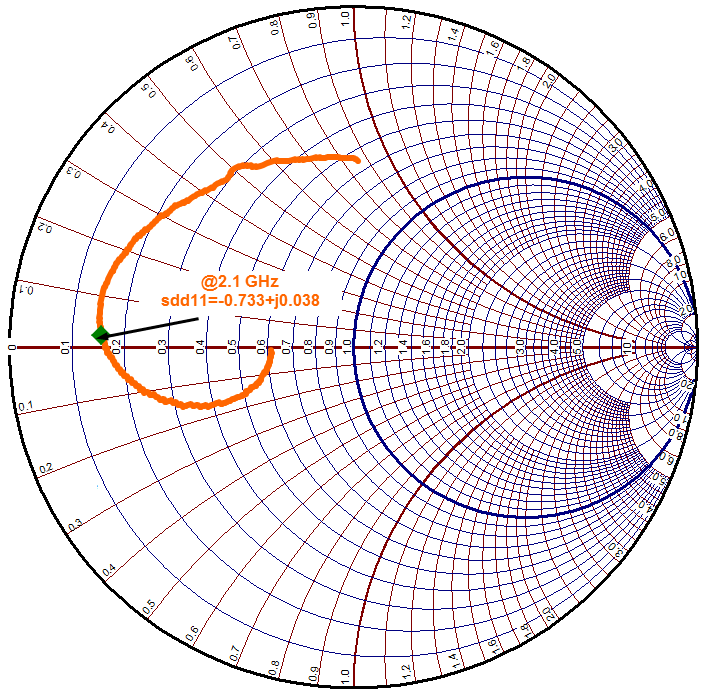

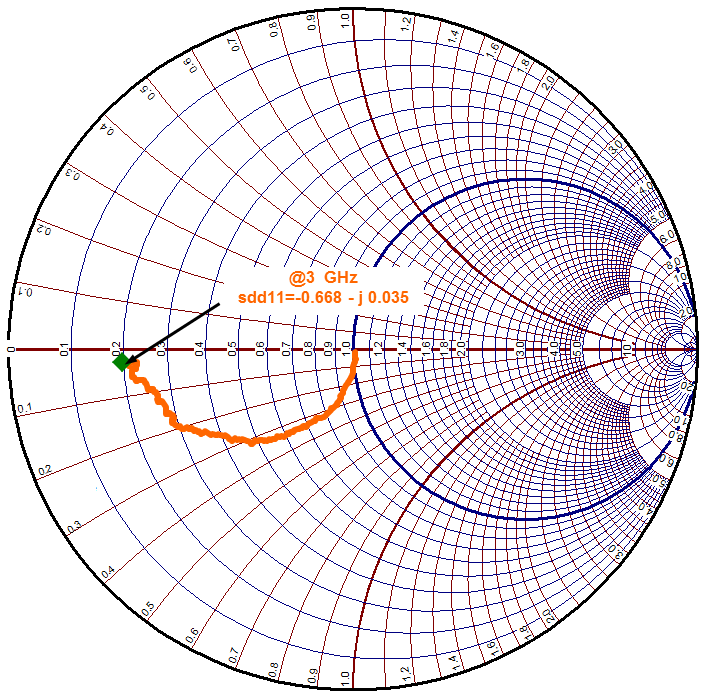

The common-mode voltage of the signal inputs is internally biased to CM using the 32.5-Ω termination resistors that allow for ac-coupling of the input drive network. Figure 60 and Figure 61 show SDD11 at the analog inputs from dc to 5 GHz with a 100-Ω reference impedance.

Figure 61. SDD11 Over the Input Frequency Range

Figure 61. SDD11 Over the Input Frequency Range

The input impedance of analog inputs can also be modelled as parallel combination of equivalent resistance and capacitance. Figure 62 and Figure 63 show how equivalent impedance (CIN and RIN) vary over frequency.

Figure 62. Differential Input Capacitance vs

Figure 62. Differential Input Capacitance vs Input Frequency

Figure 63. Differential Input Resistance vs Input Frquency

Figure 63. Differential Input Resistance vs Input Frquency

Each input pin (INP, INM) must swing symmetrically between (CM + 0.3375 V) and (CM – 0.3375 V), resulting in a 1.35-VPP (default) differential input swing. The input sampling circuit has a 3-dB bandwidth that extends up to approximately 3.2 GHz, as shown in Figure 64.

8.3.1.1 Input Clamp Circuit

The ADC32RF45 analog inputs include an internal, differential clamp for overvoltage protection. The clamp triggers for any input signals at approximately 600 mV above the input common-mode voltage, effectively limiting the maximum input signal to approximately 2.4 VPP, as shown in Figure 65 and Figure 66.

When the clamp circuit conducts, the maximum differential current flowing through the circuit (via input pins) must be limited to 20 mA.

8.3.2 Clock Input

The ADC32RF45 sampling clock input includes internal 100-Ω differential termination along with on-chip biasing. The clock input is recommended to be ac-coupled externally. The input bandwidth of the clock input is approximately 3 GHz; the clock input impedance is shown with a 100-Ω reference impedance in the smith chart of Figure 67.

Figure 67. SDD11 of the Clock Input

Figure 67. SDD11 of the Clock Input

The analog-to-digital converter (ADC) aperture jitter is a function of the clock amplitude applied to the pins. The equivalent aperture jitter for input frequencies at a 1-GHz and a 2-GHz input (fS = 3 GSPS) is shown in Figure 68. Depending on the clock frequency, a matching circuit can be designed in order to maximize the clock amplitude.

Figure 68. Equivalent Aperture Jitter vs Input Clock Amplitude

Figure 68. Equivalent Aperture Jitter vs Input Clock Amplitude

8.3.3 SYSREF Input

The SYSREF signal is a periodic signal that is sampled by the ADC32RF45 device clock and is used to align the boundary of the local multiframe clock inside the data converter. SYSREF is also used to reset critical blocks [such as the clock divider for the interleaved ADCs, numerically-controlled oscillators (NCOs), decimation filters and so forth].

The SYSREF input requires external biasing. Furthermore, SYSREF must be established before the SPI registers are programmed. A programmable delay on the SYSREF input, as shown in Figure 69, is available to help with skew adjustment when the sampling clock and SYSREF are not provided from the same source.

Figure 69. SYSREF Internal Circuit Diagram

Figure 69. SYSREF Internal Circuit Diagram

8.3.3.1 Using SYSREF

The ADC32RF45 uses SYSREF information to reset the clock divider, the NCO phase, and the LMFC counter of the JESD interface. The device provides flexibility to provide SYSREF information either from dedicated pins or through SPI register bits. SYSREF is asserted by a low-to-high transition on the SYSREF pins or a 0-to-1 change in the ASSERT SYSREF REG bit when using SPI registers, as shown in Figure 70.

Figure 70. Using SYSREF to Reset the Clock Divider, the NCO, and the LMFC Counter

Figure 70. Using SYSREF to Reset the Clock Divider, the NCO, and the LMFC Counter

The ADC32RF45 samples the SYSREF signal on the input clock rising edge. Required setup and hold time are listed in the Timing Requirements table. The input clock divider gets reset each time that SYSREF is asserted, whereas the NCO phase and the LMFC counter of the JESD interface are reset on each SYSREF assertion after disregarding the first two assertions, as shown in Table 1.

Table 1. Asserting SYSREF

| SYSREF ASSERTION INDEX | ACTION | ||

|---|---|---|---|

| INPUT CLOCK DIVIDER | NCO PHASE | LMFC COUNTER | |

| 1 | Gets reset | Does not get reset | Does not get reset |

| 2 | Gets reset | Does not get reset | Does not get reset |

| 3 | Gets reset | Gets reset | Gets reset |

| 4 and onwards | Gets reset | Gets reset | Gets reset |

The SESREF use-cases can be classified broadly into two categories:

- SYSREF is applied as aperiodic multi-shot pulses.

- SYSREF is applied as a periodic pulse.

Figure 71 shows a case when only a counted number of pulses are applied as SYSREF to the ADC.

After the first SYSREF pulse is applied, allow the DLL in the clock path to settle by waiting for the tDLL time (> 40 µs) before applying the second pulse. During this time, mask the SYSREF going to the input clock divider by setting the MASK CLKDIV SYSREF bit so that the divider output phase remains stable. The NCO phase and LMFC counter are reset on the third SYSREF pulse. After the third SYSREF pulse, the SYSREF going to the NCO and JESD block can be disabled by setting the MASK NCO SYSREF bit to avoid any unwanted resets.

Figure 72 shows how SYSREF can be applied as a continuous periodic waveform.

After applying the SYSREF signal, DLL must be allowed to lock, and the NCO phase and LMFC counter must be allowed to reset by waiting for at least the tDLL (40 µs) + 2 × tSYSREF time. Then, the SYSREF going to the NCO and JESD can be masked by setting the MASK NCO SYSREF register bit.

8.3.3.2 Frequency of the SYSREF Signal

When SYSREF is a periodic signal, its frequency is required to be a sub-harmonic of the internal local multi-frame clock (LMFC) frequency, as described in Equation 1. The LMFC frequency is determined by the selected decimation, frames per multi-frame setting (K), samples per frame (S), and device input clock frequency.

where

- N is an integer value (1, 2, 3, and so forth)

In order for the interleaving correction engine to synchronize properly, the SYSREF frequency must also be a multiple of fS / 64. Table 2 provides a summary of the valid LMFC clock settings.

Table 2. . SYSREF and LMFC Clock Frequency

| OPERATING MODE | LMFS SETTING | LMFC CLOCK FREQUENCY | SYSREF FRQUENCY |

|---|---|---|---|

| Bypass mode | 82820 | fS(1) / (20 × K) | fS / (N × LCM(2) (64, 20 × K(3))) |

| Bypass mode | 8224 | fS/(4 × K) | fS / (N × LCM (64, 4 × K)) |

| Decimation | Various | fS / (D × S(4) × K) | fS / (N × LCM (64, D(5) × S × K)) |

The SYSREF signal is recommended to be a low-frequency signal less than 5 MHz in order to reduce coupling to the signal path both on the printed circuit board (PCB) as well as internal to the device.

Example 1: fS = 3.0 GSPS, Bypass Mode (LMFS = 82820), K = 16

SYSREF = 3.0 GSPS / LCM (64, 20 × 16) / N = 9.375 MHz / N

Operate SYSREF at 4.6875 MHz (effectively divide-by-640, N = 2)

Example 2: fS = 3.0 GSPS, Divide-by-4 (LMFS = 8411), K = 16

SYSREF = 3.0 GSPS / LCM (4 ,64, 16) = 46.875 MHz / N

Operate SYSREF at 2.929688 MHz (effectively divide-by-1024, N = 16)

For proper device operation, disable the SYSREF signal after the JESD synchronization is established.

8.3.4 DDC Block

The ADC32RF45 provides a sophisticated on-chip, digital down converter (DDC) block that can be controlled through SPI register settings and the general-purpose input/output (GPIO) pins. The DDC block supports two basic operating modes: receiver (RX) mode with single- or dual-band DDC and wide-bandwidth observation receiver mode.

Each ADC channel is followed by two DDC chains consisting of the digital filter along with a complex digital mixer with a 16-bit numerically-controlled oscillator (NCO), as shown in Figure 73. The NCOs allow accurate frequency tuning within the Nyquist zone prior to the digital filtering. One DDC chain is intended for supporting a dual-band DDC configuration in receiver mode and the second DDC chain supports the wide-bandwidth output option for the observation configuration. At any given time, either the single-band DDC, the dual-band DDC, or the wideband DDC can be enabled. Furthermore, three different NCO frequencies can be selected on that path and are quickly switched using the SPI or the GPIO pins to enable wide-bandwidth observation in a multi-band application.

NOTE:

Red traces show SYSREF going to the NCO blocks.Additionally, the decimation filter block provides the option to convert the complex output back to real format at twice the decimated, complex output rate. The filter response with a real output is identical to a complex output. The band is centered in the middle of the Nyquist zone (mixed with fOUT / 4) based on a final output data rate of fOUT.

8.3.4.1 Operating Mode: Receiver

In receiver mode, the DDC block can be configured to single- or dual-band operation, as shown in Figure 74. Both DDC chains use the same decimation filter setting and the available options are discussed in the Decimation Filters section. The decimation filter setting also directly affects the interface rate and number of lanes of the JESD204B interface.

NOTE:

Red traces show SYSREF going to the NCO blocks.8.3.4.2 Operating Mode: Wide-Bandwidth Observation Receiver

This mode is intended for using a DDC with a wide bandwidth output, but for multiple bands. This mode uses a single DDC chain where up to three NCOs can be used to perform wide-bandwidth observation in a multi-band environment, as shown in Figure 75. The three NCOs can be switched dynamically using either the GPIO pins or an SPI command. All three NCOs operate continuously to ensure phase continuity; however, when the NCO is switched, the output data are invalid until the decimation filters are completely flushed with data from the new band.

NOTE:

Red traces show SYSREF going to the NCO blocks.8.3.4.3 Decimation Filters

The stop-band rejection of the decimation filters is approximately 90 dB with a pass-band bandwidth of approximately 80%. Table 3 gives an overview of the pass-band bandwidth depending on decimation filter setting and ADC sampling rate.

Table 3. Decimation Filter Summary and Maximum Available Output Bandwidth

| DECIMATION SETTING | NO. OF DDCS AVAILABLE PER CHANNEL | NOMINAL PASSBAND GAIN | BANDWIDTH | ADC SAMPLE RATE = N MSPS | ADC SAMPLE RATE = 3 GSPS | |||

|---|---|---|---|---|---|---|---|---|

| 3 dB (%) | 1 dB (%) | OUTPUT RATE (MSPS) PER BAND | OUTPUT BANDWIDTH (MHz) PER BAND | COMPLEX OUTPUT RATE (MSPS) PER BAND | OUTPUT BANDWIDTH (MHz) PER BAND | |||

| Divide-by-4 complex | 1 | –0.4 dB | 90.9 | 86.8 | N / 4 complex | 0.4 × N / 2 | 750 | 600 |

| Divide-by-6 complex | 1 | –0.65 dB | 90.6 | 86.1 | N / 6 complex | 0.4 × N / 3 | 500 | 400 |

| Divide-by-8 complex | 2 | –0.27 dB | 91.0 | 86.8 | N / 8 complex | 0.4 × N / 4 | 375 | 300 |

| Divide-by-9 complex | 2 | –0.45 dB | 90.7 | 86.3 | N / 9 complex | 0.4 × N / 4.5 | 333.3 | 266.6 |

| Divide-by-10 complex | 2 | –0.58 dB | 90.7 | 86.3 | N / 10 complex | 0.4 × N / 5 | 300 | 240 |

| Divide-by-12 complex | 2 | –0.55 dB | 90.7 | 86.4 | N / 12 complex | 0.4 × N / 6 | 250 | 200 |

| Divide-by-16 complex | 2 | –0.42 dB | 90.8 | 86.4 | N / 16 complex | 0.4 × N / 8 | 187.5 | 150 |

| Divide-by-18 complex | 2 | –0.83 dB | 91.2 | 87.0 | N / 18 complex | 0.4 × N / 9 | 166.6 | 133 |

| Divide-by-20 complex | 2 | –0.91 dB | 91.2 | 87.0 | N / 20 complex | 0.4 × N / 10 | 150 | 120 |

| Divide-by-24 complex | 2 | –0.95 db | 91.1 | 86.9 | N / 24 complex | 0.4 × N / 12 | 125 | 100 |

| Divide-by-32 complex | 2 | –0.78 dB | 91.1 | 86.8 | N / 32 complex | 0.4 × N / 16 | 93.75 | 75 |

A dual-band example with a divide-by-8 complex is shown in Figure 76.

Figure 76. Dual-Band Example

Figure 76. Dual-Band Example

The decimation filter responses normalized to the ADC sampling clock are illustrated in Figure 76 to Figure 99 and can be interpreted as follows:

Each figure contains the filter pass-band, transition bands, and alias bands, as shown in Figure 77. The x-axis in Figure 77 shows the offset frequency (after the NCO frequency shift) normalized to the ADC sampling clock frequency.

For example, in the divide-by-4 complex, the output data rate is an fS / 4 complex with a Nyquist zone of fS / 8 or 0.125 × fS. The transition band is centered around 0.125 × fS and the alias transition band is centered at 0.375 × fS. The alias bands that alias on top of the wanted signal band are centered at 0.25 × fS and 0.5 × fS (and are colored in red).

The decimation filters of the ADC32RF45 provide greater than 90-dB attenuation for the alias bands.

Figure 77. Interpretation of the Decimation Filter Plots

Figure 77. Interpretation of the Decimation Filter Plots

8.3.4.3.1 Divide-by-4

Peak-to-peak pass-band ripple: approximately 0.22 dB

8.3.4.3.2 Divide-by-6

Peak-to-peak pass-band ripple: approximately 0.38 dB

8.3.4.3.3 Divide-by-8

Peak-to-peak pass-band ripple: approximately 0.25 dB

8.3.4.3.4 Divide-by-9

Peak-to-peak pass-band ripple: approximately 0.39 dB

8.3.4.3.5 Divide-by-10

Peak-to-peak pass-band ripple: approximately 0.39 dB

8.3.4.3.6 Divide-by-12

Peak-to-peak pass-band ripple: approximately 0.36 dB

8.3.4.3.7 Divide-by-16

Peak-to-peak pass-band ripple: approximately 0.29 dB

8.3.4.3.8 Divide-by-18

Peak-to-peak pass-band ripple: approximately 0.33 dB

8.3.4.3.9 Divide-by-20

Peak-to-peak pass-band ripple: approximately 0.32 dB

8.3.4.3.10 Divide-by-24

Peak-to-peak pass-band ripple: approximately 0.30 dB

8.3.4.3.11 Divide-by-32

Peak-to-peak pass-band ripple: approximately 0.24 dB

8.3.4.3.12 Latency with Decimation Options

Device latency in 12-bit bypass mode (with LMFS = 8224) is 424 clock cycles. When the DDC option is used, latency increases as a result of decimation filters, as described in Table 4.

Table 4. Latency with different Decimation options

| DECIMATION OPTION | TOTAL LATENCY, DEVICE CLOCK CYCLES |

|---|---|

| Divide-by-4 | 516 |

| Divide-by-6 | 746 |

| Divide-by-8 | 621 |

| Divide-by-9 | 763.5 |

| Divide-by-10 | 811 |

| Divide-by-12 | 897 |

| Divide-by-16 | 1045 |

| Divide-by-18 | 1164 |

| Divide-by-20 | 1256 |

| Divide-by-24 | 1443 |

| Divide-by-32 | 1773 |

8.3.4.4 Digital Multiplexer (MUX)

The ADC32RF45 supports a mode where the output data of the ADC channel A can be routed internally to the digital blocks of both channel A and channel B. The ADC channel B can be powered down as shown in Figure 100. In this manner, the ADC32RF45 can be configured as a single-channel ADC with up to four independent DDC chains or two wideband DDC chains. All decimation filters and JESD204B format configurations are identical to the two ADC channel operation.

Figure 100. Digital Multiplexer Option

Figure 100. Digital Multiplexer Option

8.3.4.5 Numerically-Controlled Oscillators (NCOs) and Mixers

The ADC32RF45 is equipped with three independent, complex NCOs per ADC channel. The oscillator generates a complex exponential sequence, as shown in Equation 2.

where

- frequency (ω) is specified as a signed number by the 16-bit register setting

The complex exponential sequence is multiplied by the real input from the ADC to mix the desired carrier down to 0 Hz.

Each ADC channel has two DDCs. The first DDC has three NCOs and the second DDC has one NCO. The first DDC can dynamically select one of the three NCOs based on the GPIO pin or SPI selection. In wide-bandwidth mode (lower decimation factors, for example, 4 and 6), there can only be one DDC for each ADC channel. The NCO frequencies can be programmed independently through the DDCx, NCO[4:1], and the MSB and LSB register settings.

The NCO frequency setting is set by the 16-bit register value given by Equation 3:

where

- x = 0, 1

- y = 1 to 4

For example:

If fS = 3 GSPS, then the NCO register setting = 38230 (decimal).

Thus, fNCO is defined by Equation 4:

Any register setting changes that occur after the JESD204B interface is operational results in a non-deterministic NCO phase. If a deterministic phase is required, the JESD204B interface must be reinitialized after changing the register setting.

In bypass mode (when decimation filters are not used), the NCOs are powered down in order to avoid creating unwanted spurs.

8.3.5 NCO Switching

The first DDC (DDC0) on each ADC channel provides three different NCOs that can be used for phase-coherent frequency hopping. This feature is available in both single-band and dual-band mode, but only affects DDC0.

The NCOs can be switched through an SPI control or by using the GPIO pins with the register configurations shown in Table 5 for channel A (50xxh) and channel B (58Xxh). The assignment of which GPIO pin to use for INSEL0 and INSEL1 is done based on Table 6, using registers 5438h and 5C38h. The NCO selection is done based on the logic selection on the GPIO pins; see Table 7 and Figure 101.

Table 5. NCO Register Configurations

| REGISTER | ADDRESS | DESCRIPTION |

|---|---|---|

| NCO CONTROL THROUGH GPIO PINS | ||

| NCO SEL pin | 500Fh, 580Fh | Selects the NCO control through the SPI (default) or a GPIO pin. |

| INSEL0, INSEL1 | 5438h, 5C38h | Selects which two GPIO pins are used to control the NCO. |

| NCO CONTROL THROUGH SPI CONTROL | ||

| NCO SEL pin | 500Fh, 580Fh | Selects the NCO control through the SPI (default) or a GPIO pin. |

| NCO SEL | 5010h, 5810h | Selects which NCO to use for DDC0. |

Table 6. GPIO Pin Assignment

| INSELx[1:0] (Where x = 0 or 1) | GPIO PIN SELECTED |

|---|---|

| 00 | GPIO4 |

| 01 | GPIO1 |

| 10 | GPIO3 |

| 11 | GPIO2 |

Table 7. NCO Selection

| NCO SEL[1] | NCO SEL[0] | NCO SELECTED |

|---|---|---|

| 0 | 0 | NCO1 |

| 0 | 1 | NCO2 |

| 1 | 0 | NCO3 |

| 1 | 1 | n/a |

Figure 101. NCO Switching from GPIO and SPI

Figure 101. NCO Switching from GPIO and SPI

8.3.6 SerDes Transmitter Interface

Each 12.3-Gbps serializer, deserializer (SerDes) LVDS transmitter output requires ac-coupling between the transmitter and receiver. Terminate the differential pair with 100-Ω resistance (that is, two 50-Ω resistors) as close to the receiving device as possible to avoid unwanted reflections and signal degradation, as shown in Figure 102.

Figure 102. External Serial JESD204B Interface Connection

Figure 102. External Serial JESD204B Interface Connection

8.3.7 Eye Diagrams

Figure 103 and Figure 104 show the serial output eye diagrams of the ADC32RF45 at 5.0 Gbps and 12 Gbps against the JESD204B mask.

Figure 103. Data Eye at 5 Gbps

Figure 103. Data Eye at 5 Gbps

Figure 104. Data Eye at 12 Gbps

Figure 104. Data Eye at 12 Gbps

8.3.8 Alarm Outputs: Power Detectors for AGC Support

The GPIO pins can be configured as alarm outputs for channels A and B. The ADC32RF45 supports three different power detectors (an absolute peak power detector, crossing detector, and RMS power detector) as well as fast overrange from the ADC. The power detectors operate off the full-rate ADC output prior to the decimation filters.

8.3.8.1 Absolute Peak Power Detector

In this detector mode, the peak is computed over eight samples of the ADC output. Next, the peak for a block of N samples (N × S`) is computed over a programmable block length and then compared against a threshold to either set or reset the peak detector output (Figure 105 and Figure 106). There are two sets of thresholds and each set has two thresholds for hysteresis. The programmable DWELL-time counter is used for clearing the block detector alarm output.

Figure 105. Peak Power Detector Implementation

Figure 105. Peak Power Detector Implementation

Figure 106. Peak Power Detector Timing Diagram

Figure 106. Peak Power Detector Timing Diagram

Table 8 shows the register configurations required to set up the absolute peak power detector. The detector operates in the fS / 8 clock domain; one peak sample is calculated over eight actual samples.

The automatic gain control (AGC) modes can be configured separately for channel A (54xxh) and channel B (5Cxxh), although some registers are common in 54xxh (such as the GPIO pin selection).

Table 8. Registers Required for the Peak Power Detector

| REGISTER | ADDRESS | DESCRIPTION |

|---|---|---|

| PKDET EN | 5400, 5C00h | Enables peak detector |

| BLKPKDET | 5401h, 5402h, 5403h, 5C01h, 5C02h, 5C03h | Sets the block length N of number of samples (S`). Number of actual ADC samples is 8X this value: N is 17 bits: 1 to 216. |

| BLKTHHH, BLKTHHL, BLKTHLH, BLKTHLL | 5407h, 5408h, 5409h, 540Ah, 5C07h, 5C08h, 5C09h, 5C0Ah | Sets the different thresholds for the hysteresis function values from 0 to 256 (where 256 is equivalent to the peak amplitude). For example: if BLKTHHH is to –2 dBFS from peak, 10(–2 / 20) × 256 = 203, then set 5407h and 5C07h = CBh. |

| DWELL | 540Bh, 540Ch, 5C0Bh, 5C0Ch | When the computed block peak crosses the upper thresholds BLKTHHH or BLKTHLH, the peak detector output flags are set. In order to be reset, the computed block peak must remain continuously lower than the lower threshold (BLKTHHL or BLKTHLL) for the period specified by the DWELL value. This threshold is 16 bits and is specified in terms of fS / 8 clock cycles. |

| OUTSEL GPIO[4:1] | 5432h, 5433h, 5434h, 5435h | Connects the BLKPKDETH, BLKPKDETL alarms to the GPIO pins; common register. |

| IODIR | 5437h | Selects the direction for the four GPIO pins; common register. |

| RESET AGC | 542Bh, 5C2Bh | After configuration, reset the AGC module to start operation. |

8.3.8.2 Crossing Detector

In this detector mode the peak is computed over eight samples of the ADC output. Next, the peak for a block of N samples (N × S`) is computed over a programmable block length and then the peak is compared against two sets of programmable thresholds (with hysteresis). The crossing detector counts how many fS / 8 clock cycles that the block detector outputs are set high over a programmable time period and compares the counter value against the programmable thresholds. The alarm outputs are updated at the end of the time period, routed to the GPIO pins, and held in that state through the next cycle, as shown in Figure 107 and Figure 108. Alternatively, a 2-bit format can be used but (because the ADC32RF45 has four GPIO pins available) this feature uses all four pins for a single channel.

Figure 107. Crossing Detector Implementation

Figure 107. Crossing Detector Implementation

Figure 108. Crossing Detector Timing Diagram

Figure 108. Crossing Detector Timing Diagram

Table 9 shows the register configurations required to set up the crossing detector. The detector operates in the

fS / 8 clock domain. The AGC modes can be configured separately for channel A (54xxh) and channel B (5Cxxh), although some registers are common in 54xxh (such as the GPIO pin selection).

Table 9. Registers Required for the Crossing Detector Operation

| REGISTER | ADDRESS | DESCRIPTION |

|---|---|---|

| PKDET EN | 5400h, 5C00h | Enables peak detector |

| BLKPKDET | 5401h, 5402h, 5403h, 5C01h, 5C02h, 5C03h | Sets the block length N of number of samples (S`). Number of actual ADC samples is 8X this value: N is 17 bits: 1 to 216. |

| BLKTHHH, BLKTHHL, BLKTHLH, BLKTHLL | 5407h, 5408h, 5409h, 540Ah, 5C07h, 5C08h, 5C09h, 5C0Ah | Sets the different thresholds for the hysteresis function values from 0 to 256 (where 256 is equivalent to the peak amplitude). For example: if BLKTHHH is to –2 dBFS from peak, 10(–2 / 20) × 256 = 203, then set 5407h and 5C07h = CBh. |

| FILT0LPSEL | 540Dh, 5C0Dh | Select block detector output or 2-bit output mode as the input to the interrupt identification register (IIR) filter. |

| TIMECONST | 540Eh, 540Fh, 5C0Eh, 5C0Fh |

Sets the crossing detector time period for N = 0 to 15 as 2N × fS / 8 clock cycles. The maximum time period is 32768 × fS / 8 clock cycles (approximately 87 µs at 3 GSPS). |

| FIL0THH, FIL0THL, FIL1THH, FIL1THL | 540Fh-5412h, 5C0Fh-5C12h, 5416h-5419h, 5C16h-5C19h | Comparison thresholds for the crossing detector counter. These thresholds are 16-bit thresholds in 2.14-signed notation. A value of 1 (4000h) corresponds to 100% crossings, a value of 0.125 (0800h) corresponds to 12.5% crossings. |

| DWELLIIR | 541Dh, 541Eh, 5C1Dh, 5C1Eh | DWELL counter for the IIR filter hysteresis. |

| IIR0 2BIT EN, IIR1 2BIT EN |

5413h, 54114h, 5C13h, 5C114h |

Enables 2-bit output format for the crossing detector. |

| OUTSEL GPIO[4:1] | 5432h, 5433h, 5434h, 5435h |

Connects the IIRPKDET0, IIRPKDET1 alarms to the GPIO pins; common register. |

| IODIR | 5437h | Selects the direction for the four GPIO pins; common register. |

| RESET AGC | 542Bh, 5C2Bh | After configuration, reset the AGC module to start operation. |

8.3.8.3 RMS Power Detector

In this detector mode the peak power is computed for a block of N samples over a programmable block length and then compared against two sets of programmable thresholds (with hysteresis).

The RMS power detector circuit provides configuration options, as shown in Figure 109. The RMS power value (1 or 2 bit) can be output onto the GPIO pins. In 2-bit output mode, two different thresholds are used whereas the 1-bit output provides one threshold together with hysteresis.

Figure 109. RMS Power Detector Implementation

Figure 109. RMS Power Detector Implementation

Table 10 shows the register configurations required to set up the RMS power detector. The detector operates in the fS / 8 clock domain. The AGC modes can be configured separately for channel A (54xxh) and channel B (5Cxxh), although some registers are common in 54xxh (such as the GPIO pin selection).

Table 10. Registers Required for Using the RMS Power Detector Feature

| REGISTER | ADDRESS | DESCRIPTION |

|---|---|---|

| RMSDET EN | 5420h, 5C20h | Enables RMS detector |

| PWRDETACCU | 5421h, 5C21h | Programs the block length to be used for RMS power computation. The block length is defined in terms of fS / 8 clocks. The block length can be programmed as 2M with M = 0 to 16. |

| PWRDETH, PWRDETL | 5422h, 5423h, 5424h, 5425h, 5C22h, 5C23h, 5C24h, 5C25h | The computed average power is compared against these high and low thresholds. One LSB of the thresholds represents 1 / 216. For example: is PWRDETH is set to –14 dBFS from peak, [10(–14 / 20)]2 × 216 = 2609, then set 5422h, 5423h, 5C22h, 5C23h = 0A31h. |

| RMS2BIT EN | 5427h, 5C27h | Enables 2-bit output format for the RMS detector output. |

| OUTSEL GPIO[4:1] | 5432h, 5433h, 5434h, 5435h |

Connects the PWRDET alarms to the GPIO pins; common register. |

| IODIR | 5437h | Selects the direction for the four GPIO pins; common register. |

| RESET AGC | 542Bh, 5C2Bh | After configuration, reset the AGC module to start operation. |

8.3.8.4 GPIO AGC MUX

The GPIO pins can be used to control the NCO in wideband DDC mode or as alarm outputs for channel A and B. The GPIO pins can be configured through the SPI control to output the alarm from the peak power (1 bit), crossing detector (1 or 2 bit), faster overrange, or the RMS power output, as shown in Figure 110.

The programmable output MUX allows connecting any signal (including the NCO control) to any of the four GPIO pins. These pins can be configured as outputs (AGC alarm) or inputs (NCO control) through SPI programming.

Figure 110. GPIO Output MUX Implementation

Figure 110. GPIO Output MUX Implementation

8.3.9 Power-Down Mode

The ADC32RF45 provides a lot of configurability for the power-down mode. Power-down can be enabled using the PDN pin or the SPI register writes.

8.3.10 ADC Test Pattern

The ADC32RF45 provides several different options to output test patterns instead of the actual output data of the ADC in order to simplify the serial interface and system debug of the JESD204B digital interface link. The output data path is shown in Figure 111.

Figure 111. Test Pattern Generator Implementation

Figure 111. Test Pattern Generator Implementation

8.3.10.1 Digital Block

The ADC test pattern replaces the actual output data of the ADC. The test patterns listed in Table 11 are available when the DDC is enabled and located in register 37h of the decimation filter page. When programmed, the test patterns are output for each converter (M) stream. The number of converter streams per channel increases by 2 when complex (I, Q) output or dual-band DDC is selected. The test patterns can be synchronized for both ADC channels using the SYSREF signal.

Additionally, a 12-bit ramp test pattern is available in DDC bypass mode.

NOTE

The number of converters increases in dual-band DDC mode and with a complex output.

Table 11. Test Pattern Options (Register 37h)

| BIT | NAME | DEFAULT | DESCRIPTION |

|---|---|---|---|

| 7-4 | TEST PATTERN | 0000 | Test pattern outputs on channel A and B. 0000 = Normal operation using ADC output data 0001 = Outputs all 0s 0010 = Outputs all 1s 0011 = Outputs toggle pattern: output data are an alternating sequence of 10101010101010 and 01010101010101 0100 = Output digital ramp: output data increment by one LSB every clock cycle from code 0 to 65535 0110 = Single pattern: output data are a custom pattern 1 (75h and 76h) 0111 Double pattern: output data alternate between custom pattern 1 and custom pattern 2 1000 = Deskew pattern: output data are AAAAh 1001 = SYNC pattern: output data are FFFFh |

8.3.10.2 Transport Layer

The transport layer maps the ADC output data into 8-bit octets and constructs the JESD204B frames using the LMFS parameters. Tail bits or 0's are added when needed. Alternatively, the JESD204B long transport layer test pattern can be substituted instead of the ADC data with the JESD frame, as shown in Table 12.

Table 12. Transport Layer Test Mode EN (Register 01h)

| BIT | NAME | DEFAULT | DESCRIPTION |

|---|---|---|---|

| 4 | TESTMODE EN | 0 | Generates long transport layer test pattern mode according to section 5.1.6.3 of the JESD204B specification. 0 = Test mode disabled 1 = Test mode disabled |

8.3.10.3 Link Layer

The link layer contains the scrambler and the 8b, 10b encoding of any data passed on from the transport layer. Additionally, the link layer also handles the initial lane alignment sequence that can be manually restarted.

The link layer test patterns are intended for testing the quality of the link (jitter testing and so forth). The test patterns do not pass through the 8b, 10b encoder and contain the options listed in Table 13.

Table 13. Link Layer Test Mode (Register 03h)

| BIT | NAME | DEFAULT | DESCRIPTION |

|---|---|---|---|

| 7-5 | LINK LAYER TESTMODE | 000 | Generates a pattern according to section 5.3.3.8.2 of the JESD204B document. 000 = Normal ADC data 001 = D21.5 (high-frequency jitter pattern) 010 = K28.5 (mixed-frequency jitter pattern) 011 = Repeat the initial lane alignment (generates a K28.5 character and repeats lane alignment sequences continuously) 100 = 12-octet random pattern (RPAT) jitter pattern |

Furthermore, a 215 pseudo-random binary sequence (PRBS) can be enabled by setting up a custom test pattern (AAAAh) in the ADC section and running AAAAh through the 8b, 10b encoder with scrambling enabled.

8.4 Device Functional Modes

8.4.1 Device Configuration

The ADC32RF45 can be configured using a serial programming interface, as described in the Serial Interface section. In addition, the device has one dedicated parallel pin (PDN) for controlling the power-down modes.

8.4.2 JESD204B Interface

The ADC32RF45 supports device subclass 1 with a maximum output data rate of 12.5 Gbps for each serial transmitter.

An external SYSREF signal is used to align all internal clock phases and the local multiframe clock to a specific sampling clock edge. This alignment allows synchronization of multiple devices in a system and minimizes timing and alignment uncertainty. The SYNCB input is used to control the JESD204B SerDes blocks, as shown in Figure 112.

Depending on the ADC sampling rate, the JESD204B output interface can be operated with one, two, or four lanes per ADC channel. The JESD204B setup and configuration of the frame assembly parameters is controlled through the SPI interface.

Figure 112. JESD Signal Overview

Figure 112. JESD Signal Overview

The JESD204B transmitter block consists of the transport layer, the data scrambler, and the link layer, as shown in Figure 113. The transport layer maps the ADC output data into the selected JESD204B frame data format and manages if the ADC output data or test patterns are transmitted. The link layer performs the 8b, 10b data encoding as well as the synchronization and initial lane alignment using the SYNC input signal. Optionally, data from the transport layer can be scrambled.

Figure 113. JESD Digital Block Implementation

Figure 113. JESD Digital Block Implementation

8.4.2.1 JESD204B Initial Lane Alignment (ILA)

The receiving device starts the initial lane alignment process by deasserting the SYNCB signal. The SYNCB signal can be issued using the SYNCB input pins or by setting the proper SPI bits. When a logic low is detected on the SYNCB input, the ADC32RF45 starts transmitting comma (K28.5) characters to establish the code group synchronization, as shown in Figure 114.

When synchronization completes, the receiving device reasserts the SYNCB signal and the ADC32RF45 starts the initial lane alignment sequence with the next local multiframe clock boundary. The ADC32RF45 transmits four multiframes, each containing K frames (K is SPI programmable). Each of the multiframes contains the frame start and end symbols. The second multiframe also contains the JESD204 link configuration data.

Figure 114. JESD Internal Timing Information

Figure 114. JESD Internal Timing Information

8.4.2.2 JESD204B Frame Assembly

The JESD204B standard defines the following parameters:

- F is the number of octets per frame clock period

- L is the number of lanes per link

- M is the number of converters for the device

- S is the number of samples per frame

8.4.2.3 JESD204B Frame Assembly in Bypass Mode

Table 14 lists the available JESD204B formats and valid ranges for the ADC32RF45. The ranges are limited by the SerDes line rate and the maximum ADC sample frequency. The sample alignment for the bypass modes on the different lanes is shown in Table 15.

Table 14. JESD Mode Options: Bypass Mode

| DECIMATION SETTING (Complex) | OUTPUT RESOLUTION (Bits) | L | M | F | S | 12-BIT MODE | PLL MODE | JESD MODE0 | JESD MODE1 | JESD MODE2 | MAX fCLK

(Gsps) |

RATIO [fSerDes / fCLK (Gbps / GSPS)] |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Bypass | 12(1) | 8 | 2 | 8 | 20 | 3 | 16X | 3 | 0 | 0 | 3 | 4 |

| 14 | 8 | 2 | 2 | 4 | 0 | 20X | 1 | 0 | 0 | 2.5 | 5 |

Table 15. JESD Sample Lane Alignments: Bypass Mode(1)

| OUTPUT LANE | LMFS = 8224 | LMFS = 82820 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| DA0 | A0[13:6] | A0[5:0], 00 | A0[11:4] | A0[3:0], A1[11:8] |

A1[7:0] | A2[11:4] | A2[3:0], A3[11:8] |

A3[7:0] | A4[11:4] | A4[3:0], 0000 |

| DA1 | A1[13:6] | A1[5:0], 00 | A5[11:4] | A5[3:0], A6[11:8] |

A6[7:0] | A7[11:4] | A7[3:0], A8[11:8] |

A8[7:0] | A9[11:4] | A9[3:0], 0000 |

| DA2 | A2[13:6] | A2[5:0], 00 | A10[11:4] | A10[3:0], A11[11:8] |

A11[7:0] | A12[11:4] | A12[3:0], A13[11:8] |

A13[7:0] | A14[11:4] | A14[3:0], 0000 |

| DA3 | A3[13:6] | A3[5:0], 00 | A15[11:4] | A15[3:0], A16[11:8] |

A16[7:0] | A17[11:4] | A17[3:0], A18[11:8] |

A18[7:0] | A19[11:4] | A19[3:0], 0000 |

| DB0 | B0[13:6] | B0[5:0], 00 | B0[11:4] | B0[3:0], B1[11:8] |

B1[7:0] | B2[11:4] | B2[3:0], B3[11:8] |

B3[7:0] | B4[11:4] | B4[3:0], 0000 |

| DB1 | B1[13:6] | B1[5:0], 00 | B5[11:4] | B5[3:0], B6[11:8] |

B6[7:0] | B7[11:4] | B7[3:0], B8[11:8] |

B8[7:0] | B9[11:4] | B9[3:0], 0000 |

| DB2 | B2[13:6] | B2[5:0], 00 | B10[11:4] | B10[3:0], B11[11:8] |

B11[7:0] | B12[11:4] | B12[3:0], B13[11:8] |

B13[7:0] | B14[11:4] | B14[3:0], 0000 |

| DB3 | B3[13:6] | B3[5:0], 00 | B15[11:4] | B15[3:0], B16[11:8] |

B16[7:0] | B17[11:4] | B17[3:0], B18[11:8] |

B18[7:0] | B19[11:4] | B19[3:0], 0000 |

8.4.2.4 JESD204B Frame Assembly with Decimation (Single-Band DDC): Complex Output

Table 16 lists the available JESD204B interface formats and valid ranges for the ADC32RF45 with decimation (single-band DDC) when using a complex output format. The ranges are limited by the SerDes line rate and the maximum ADC sample frequency. The sample alignment on the different lanes is shown in Table 17.

Table 16. JESD Mode Options: Single-Band Complex Output

| DECIMATION SETTING (Complex) | NUMBER OF ACTIVE DDCS | L | M | F | S | PLL MODE | JESD MODE0 | JESD MODE1 | JESD MODE2 | RATIO [fSerDes / fCLK (Gbps / GSPS)] |

|---|---|---|---|---|---|---|---|---|---|---|

| Divide-by-4 | 1 per channel | 8 | 4 | 1 | 1 | 20X | 1 | 1 | 0 | 2.5 |

| 8 | 4 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 5 | ||

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-6 | 1 per channel | 8 | 4 | 1 | 1 | 20X | 1 | 1 | 0 | 1.67 |

| 8 | 4 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 3.33 | ||

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-8 | 1 per channel | 4 | 4 | 2 | 1 | 20X | 1 | 0 | 0 | 2.5 |

| 2 | 4 | 4 | 1 | 40X | 2 | 0 | 0 | 5 | ||

| Divide-by-9 | 1 per channel | 4 | 4 | 2 | 1 | 20X | 1 | 0 | 0 | 2.22 |

| 2 | 4 | 4 | 1 | 40X | 2 | 0 | 0 | 4.44 | ||

| Divide-by-10 | 1 per channel | 4 | 4 | 2 | 1 | 20X | 1 | 0 | 0 | 2 |

| 2 | 4 | 4 | 1 | 40X | 2 | 0 | 0 | 4 | ||

| Divide-by-12 | 1 per channel | 4 | 4 | 2 | 1 | 20X | 1 | 0 | 0 | 1.67 |

| 2 | 4 | 4 | 1 | 40X | 2 | 0 | 0 | 3.33 | ||

| Divide-by-16 | 1 per channel | 4 | 4 | 2 | 1 | 20X | 1 | 0 | 0 | 1.25 |

| 2 | 4 | 4 | 1 | 40X | 2 | 0 | 0 | 2.5 | ||

| Divide-by-18 | 1 per channel | 4 | 4 | 2 | 1 | 20X | 1 | 0 | 0 | 1.11 |

| 2 | 4 | 4 | 1 | 40X | 2 | 0 | 0 | 2.22 | ||

| Divide-by-20 | 1 per channel | 4 | 4 | 2 | 1 | 20X | 1 | 0 | 0 | 1 |

| 2 | 4 | 4 | 1 | 40X | 2 | 0 | 0 | 2 | ||

| Divide-by-24 | 1 per channel | 4 | 4 | 2 | 1 | 20X | 1 | 0 | 0 | 1.67 |

| Divide-by-32 | 1 per channel | 2 | 4 | 4 | 1 | 40X | 2 | 0 | 0 | 1.25 |

Table 17. JESD Sample Lane Alignments: Single-Band Complex Output(1)

| OUTPUT LANE | LMFS = 8411 | LMFS = 8422 | LMFS = 4421 20X | LMFS = 4421 40X | LMFS = 4442 | LMFS = 2441 | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| DA0 | AI0

[15:8] |

AI0

[15:8] |

AI0

[7:0] |

AI0

[15:8] |

AI0

[7:0] |

||||||||||

| DA1 | AI0

[7:0] |

AI1

[15:8] |

AI1

[7:0] |

AQ0

[15:8] |

AQ0

[7:0] |

AI0

[15:8] |

AI0

[7:0] |

AI0

[15:8] |

AI0

[7:0] |

AI1

[15:8] |

AI1

[7:0] |

AI0

[15:8] |

AI0

[7:0] |

AQ0

[15:8] |

AQ0

[7:0] |

| DA2 | AQ0

[15:8] |

AQ0

[15:8] |

AQ0

[7:0] |

AQ0

[15:8] |

AQ0

[7:0] |

AQ0

[15:8] |

AQ0

[7:0] |

AQ1

[15:8] |

AQ1

[7:0] |

||||||

| DA3 | AQ0

[7:0] |

AQ1

[15:8] |

AQ1

[7:0] |

||||||||||||

| DB0 | BI0

[15:8] |

BI0

[15:8] |

BI0

[7:0] |

BI0

[15:8] |

BI0

[7:0] |

||||||||||

| DB1 | BI0

[7:0] |

BI1

[15:8] |

BI1

[7:0] |

BQ0

[15:8] |

BQ0

[7:0] |

BI0

[15:8] |

BI0

[7:0] |

BI0

[15:8] |

BI0

[7:0] |

BI1

[15:8] |

BI1

[7:0] |

BI0

[15:8] |

BI0

[7:0] |

BQ0

[15:8] |

BQ0

[7:0] |

| DB2 | BQ0

[15:8] |

BQ0

[15:8 |

BQ0

[7:0] |

BQ0

[15:8] |

BQ0

[7:0] |

BQ0

[15:8] |

BQ0

[7:0] |

BQ1

[15:8] |

BQ1

[7:0] |

||||||

| DB3 | BQ0

[7:0] |

BQ1

[15:8] |

BQ1

[7:0] |

||||||||||||

8.4.2.5 JESD204B Frame Assembly with Decimation (Single-Band DDC): Real Output

Table 18 lists the available JESD204B formats and valid ranges for the ADC32RF45 with decimation (single-band DDC) when using real output format. The ranges are limited by the SerDes line rate and the maximum ADC sample frequency. The sample alignment on the different lanes is shown in Table 19.

Table 18. JESD Mode Options: Single-Band Real Output (Wide Bandwidth)

| DECIMATION SETTING (Complex) | NUMBER OF ACTIVE DDCS | L | M | F | S | PLL MODE | JESD MODE0 | JESD MODE1 | JESD MODE2 | RATIO [fSerDes / fCLK (Gbps / GSPS)] |

|---|---|---|---|---|---|---|---|---|---|---|

| Divide-by-4 (Divide-by-2 real) |

1 per channel | 8 | 2 | 2 | 4 | 20X | 1 | 0 | 0 | 2.5 |

| 4 | 2 | 4 | 4 | 40X | 2 | 0 | 0 | 5 | ||

| 4 | 2 | 1 | 1 | 40X | 0 | 0 | 1 | |||

| Divide-by-6 (Divide-by-3 real) |

1 per channel | 8 | 2 | 2 | 4 | 20X | 1 | 0 | 0 | 1.67 |

| 4 | 2 | 4 | 4 | 40X | 2 | 0 | 0 | 3.33 | ||

| 4 | 2 | 1 | 1 | 40X | 0 | 0 | 1 |

Table 19. JESD Sample Lane Alignment: Single-Band Real Output (Wide Bandwidth)(1)

| OUTPUT LANE | LMFS = 8224 | LMFS = 4244 | LMFS = 4211 | ||||

|---|---|---|---|---|---|---|---|

| DA0 | A0[15:8] | A0[7:0] | |||||

| DA1 | A1[15:8] | A1[7:0] | A0[15:8] | A0[7:0] | A1[15:8] | A1[7:0] | A0[15:8] |

| DA2 | A2[15:8] | A2[7:0] | A2[15:8] | A2[7:0] | A3[15:8] | A3[7:0] | A0[7:0] |

| DA3 | A3[15:8] | A3[7:0] | |||||

| DB0 | B0[15:8] | B0[7:0] | |||||

| DB1 | B1[15:8] | B1[7:0] | B0[15:8] | B0[7:0] | B1[15:8] | B1[7:0] | B0[15:8] |

| DB2 | B2[15:8] | B2[7:0] | B0[15:8] | B2[7:0] | B3[15:8] | B3[7:0] | B0[7:0] |

| DB3 | B3[15:8] | B3[7:0] | |||||

8.4.2.6 JESD204B Frame Assembly with Decimation (Single-Band DDC): Real Output

Table 20 lists the available JESD204B formats and valid ranges for the ADC32RF45 with decimation (dual-band DDC) when using a complex output format. The sample alignment on the different lanes is shown in Table 21.

Table 20. JESD Mode Options: Single-Band Real Output

| DECIMATION SETTING (Complex) | NUMBER OF ACTIVE DDCS | L | M | F | S | PLL MODE | JESD MODE0 | JESD MODE1 | JESD MODE2 | RATIO [fSerDes / fCLK (Gbps / GSPS)] |

|---|---|---|---|---|---|---|---|---|---|---|

| Divide-by-8 (Divide-by-4 real) |

1 per channel | 4 | 2 | 1 | 1 | 20X | 1 | 1 | 0 | 2.5 |

| 4 | 2 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 2 | 2 | 2 | 1 | 40X | 0 | 0 | 1 | 5 | ||

| 2 | 2 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-9 (Divide-by-4.5 real) |

1 per channel | 4 | 2 | 1 | 1 | 20X | 1 | 1 | 0 | 2.22 |

| 4 | 2 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 2 | 2 | 2 | 1 | 40X | 0 | 0 | 1 | 4.44 | ||

| 2 | 2 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-10 (Divide-by-5 real) |

1 per channel | 4 | 2 | 1 | 1 | 20X | 1 | 1 | 0 | 2 |

| 4 | 2 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 2 | 2 | 2 | 1 | 40X | 0 | 0 | 1 | 4 | ||

| 2 | 2 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-12 (Divide-by-6 real) |

1 per channel | 4 | 2 | 1 | 1 | 20X | 1 | 1 | 0 | 1.67 |

| 4 | 2 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 2 | 2 | 2 | 1 | 40X | 0 | 0 | 1 | 3.33 | ||

| 2 | 2 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-16 (Divide-by-8 real) |

1 per channel | 4 | 2 | 1 | 1 | 20X | 1 | 1 | 0 | 1.25 |

| 4 | 2 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 2 | 2 | 2 | 1 | 40X | 0 | 0 | 1 | 2.5 | ||

| 2 | 2 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-18 (Divide-by-9 real) |

1 per channel | 4 | 2 | 1 | 1 | 20X | 1 | 1 | 0 | 1.11 |

| 4 | 2 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 2 | 2 | 2 | 1 | 40X | 0 | 0 | 1 | 2.22 | ||

| 2 | 2 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-20 (Divide-by-10 real) |

1 per channel | 4 | 2 | 1 | 1 | 20X | 1 | 1 | 0 | 1 |

| 4 | 2 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 2 | 2 | 2 | 1 | 40X | 0 | 0 | 1 | 2 | ||

| 2 | 2 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-24 (Divide-by-12 real) |

1 per channel | 2 | 2 | 2 | 1 | 40X | 0 | 0 | 1 | 1.67 |

| 2 | 2 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-32 (Divide-by-16 real) |

1 per channel | 2 | 2 | 2 | 1 | 40X | 0 | 0 | 1 | 1.25 |

| 2 | 2 | 4 | 2 | 40X | 2 | 0 | 0 |

Table 21. JESD Sample Lane Assignment: Single-Band Real Output(1)

| OUTPUT LANE | LMFS = 4211 | LMFS = 4222 | LMFS = 2221 | LMFS = 2242 | |||||

|---|---|---|---|---|---|---|---|---|---|

| DA0 | A0[15:8] | A0[15:8] | A0[7:0] | ||||||

| DA1 | A0[7:0] | A1[15:8] | A1[7:0] | A0 [15:8] | A0[7:0] | A0[15:8] | A0[7:0] | A1[15:8] | A1[7:0] |

| DB0 | B0[15:8] | B0[15:8] | B0[7:0] | ||||||

| DB1 | B0[7:0] | B1[15:8] | B1[7:0] | B0[15:8] | B0[7:0] | B0[15:8] | B0[7:0] | B1[15:8] | B1[7:0] |

8.4.2.7 JESD204B Frame Assembly with Decimation (Dual-Band DDC): Complex Output

Table 22 lists the available JESD204B formats and valid ranges for the ADC32RF45 with decimation (dual-band DDC) when using a complex output format. The ranges are limited by the SerDes line rate and the maximum ADC sample frequency. The sample alignment on the different lanes is shown in Table 23.

Table 22. JESD Mode Options: Dual-Band Complex Output

| DECIMATION SETTING (Complex) | NUMBER OF ACTIVE DDCS | L | M | F | S | PLL MODE | JESD MODE0 | JESD MODE1 | JESD MODE2 | RATIO [fSerDes / fCLK (Gbps / GSPS)] |

|---|---|---|---|---|---|---|---|---|---|---|

| Divide-by-8 | 2 per channel | 8 | 8 | 2 | 1 | 20X | 1 | 0 | 0 | 2.5 |

| 4 | 8 | 4 | 1 | 40X | 2 | 0 | 0 | 5 | ||

| Divide-by-9 | 2 per channel | 8 | 8 | 2 | 1 | 20X | 1 | 0 | 0 | 2.22 |

| 4 | 8 | 4 | 1 | 40X | 2 | 0 | 0 | 4.44 | ||

| Divide-by-10 | 2 per channel | 8 | 8 | 2 | 1 | 20X | 1 | 0 | 0 | 2 |

| 4 | 8 | 4 | 1 | 40X | 2 | 0 | 0 | 4 | ||

| Divide-by-12 | 2 per channel | 8 | 8 | 2 | 1 | 20X | 1 | 0 | 0 | 1.67 |

| 4 | 8 | 4 | 1 | 40X | 2 | 0 | 0 | 3.33 | ||

| Divide-by-16 | 2 per channel | 8 | 8 | 2 | 1 | 20X | 1 | 0 | 0 | 1.25 |

| 4 | 8 | 4 | 1 | 40X | 2 | 0 | 0 | 2.5 | ||

| Divide-by-18 | 2 per channel | 8 | 8 | 2 | 1 | 20X | 1 | 0 | 0 | 1.11 |

| 4 | 8 | 4 | 1 | 40X | 2 | 0 | 0 | 2.22 | ||

| Divide-by-20 | 2 per channel | 8 | 8 | 2 | 1 | 20X | 1 | 0 | 0 | 1 |

| 4 | 8 | 4 | 1 | 40X | 2 | 0 | 0 | 2 | ||

| Divide-by-24 | 2 per channel | 4 | 8 | 4 | 1 | 40X | 2 | 0 | 0 | 1.67 |

| Divide-by-32 | 2 per channel | 4 | 8 | 4 | 1 | 40X | 2 | 0 | 0 | 1.25 |

Table 23. JESD Sample Lane Assignment: Dual-Band Complex Output(1)

| OUTPUT LANE | LMFS = 8821 | LMFS = 4841 | ||||

|---|---|---|---|---|---|---|

| DA0 | A10[15:8] | A10[7:0] | ||||

| DA1 | A1Q0[15:8] | A1Q0[7:0] | A1I0[15:8] | A1I0[7:0] | A1Q0[15:8] | A1Q0[7:0] |

| DA2 | A2I0[15:8] | A2I0[7:0] | A2I0[15:8] | A2I0[7:0] | A2Q0[15:8] | A2Q0[7:0] |

| DA3 | A2Q0[15:8] | A2Q0[7:0] | ||||

| DB0 | B1I0[15:8] | B1I0[7:0] | ||||

| DB1 | B1Q0[15:8] | B1Q0[7:0] | B1I0[15:8] | B1I0[7:0] | B1Q0[15:8] | B1Q0[7:0] |

| DB2 | B2I0[15:8] | B2I0[7:0] | B2I0[15:8] | B2I0[7:0] | B2Q0[15:8] | B2Q0[7:0] |

| DB3 | B2Q0[15:8] | B2Q0[7:0] | ||||

8.4.2.8 JESD204B Frame Assembly with Decimation (Dual-Band DDC): Real Output

Table 24 lists the available JESD204B formats and valid ranges for the ADC32RF45 with decimation (dual-band DDC) when using real output format. The ranges are limited by the SerDes line rate and the maximum ADC sample frequency. The sample alignment on the different lanes is shown in Table 25.

Table 24. JESD Mode Options: Dual-Band Real Output

| DECIMATION SETTING (Complex) | NUMBER OF ACTIVE DDCS | L | M | F | S | PLL MODE | JESD MODE0 | JESD MODE1 | JESD MODE2 | RATIO [fSerDes / fCLK (Gbps / GSPS)] |

|---|---|---|---|---|---|---|---|---|---|---|

| Divide-by-8 (Divide-by-4 real) |

2 per channel | 8 | 4 | 1 | 1 | 20X | 1 | 1 | 0 | 2.5 |

| 8 | 4 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 5 | ||

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-9 (Divide-by-4.5 real) |

2 per channel | 8 | 4 | 1 | 1 | 20X | 1 | 1 | 0 | 2.22 |

| 8 | 4 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 4.44 | ||

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-10 (Divide-by-5 real) |

2 per channel | 8 | 4 | 1 | 1 | 20X | 1 | 1 | 0 | 2 |

| 8 | 4 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 4 | ||

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-12 (Divide-by-6 real) |

2 per channel | 8 | 4 | 1 | 1 | 20X | 1 | 1 | 0 | 1.67 |

| 8 | 4 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 3.33 | ||

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-16 (Divide-by-8 real) |

2 per channel | 8 | 4 | 1 | 1 | 20X | 1 | 1 | 0 | 1.25 |

| 8 | 4 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 2.5 | ||

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-18 (Divide-by-9 real) |

2 per channel | 8 | 4 | 1 | 1 | 20X | 1 | 1 | 0 | 1.11 |

| 8 | 4 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 2.22 | ||

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-20 (Divide-by-10 real) |

2 per channel | 8 | 4 | 1 | 1 | 20X | 1 | 1 | 0 | 1 |

| 8 | 4 | 2 | 2 | 20X | 1 | 0 | 0 | |||

| 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 2 | ||

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-24 (Divide-by-12 real) |

2 per channel | 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 1.67 |

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 | |||

| Divide-by-32 (Divide-by-16 real) |

2 per channel | 4 | 4 | 2 | 1 | 40X | 0 | 0 | 1 | 1.25 |

| 4 | 4 | 4 | 2 | 40X | 2 | 0 | 0 |

Table 25. JESD Sample Lane Assignment: Dual-Band Complex Output(1)

| OUTPUT LANE | LMFS = 8411 | LMFS = 8422 | LMFS = 4421 | LMFS = 4442 | |||||

|---|---|---|---|---|---|---|---|---|---|

| DA0 | A10[15:8] | A10[15:8] | A10[7:0] | ||||||

| DA1 | A10[7:0] | A11[15:8] | A11[7:0] | A10[15:8] | A10[7:0] | A10[15:8] | A10[7:0] | A11[15:8] | A11[7:0] |

| DA2 | A20[15:8] | A20[15:8] | A20[7:0] | A20[15:8] | A20[7:0] | A20[15:8] | A20[7:0] | A21[15:8] | A21[7:0] |

| DA3 | A20[7:0] | A21[15:8] | A21[7:0] | ||||||

| DB0 | B10[15:8] | B10[15:8] | B10[7:0] | ||||||

| DB1 | B10[7:0] | B11[15:8] | B11[7:0] | B10[15:8] | B10[7:0] | B10[15:8] | B10[7:0] | B11[15:8] | B11[7:0] |

| DB2 | B20[15:8] | B20[15:8] | B20[7:0] | B20[15:8] | B20[7:0] | B20[15:8] | B20[7:0] | B21[15:8] | B21[7:0] |

| DB3 | B20[7:0] | B21[15:8] | B21[7:0] | ||||||

8.4.3 Serial Interface

The ADC has a set of internal registers that can be accessed by the serial interface formed by the SEN (serial interface enable), SCLK (serial interface clock), and SDIN (serial interface data) pins. Serially shifting bits into the device is enabled when SEN is low. SDIN serial data are latched at every SCLK rising edge when SEN is active (low), as shown in Figure 115. The interface can function with SCLK frequencies from 20 MHz down to low speeds (of a few hertz) and also with a non-50% SCLK duty cycle, as shown in Table 26.

The SPI access uses 24 bits consisting of eight register data bits, 12 register address bits, and four special bits to distinguish between read/write, page and register, and individual channel access, as described in Table 27.

Figure 115. SPI Timing Diagram

Figure 115. SPI Timing Diagram

Table 26. SPI Timing Information

| MIN | TYP | MAX | UNIT | ||

|---|---|---|---|---|---|

| fSCLK | SCLK frequency (equal to 1 / tSCLK) | 1 | 20 | MHz | |

| tSLOADS | SEN to SCLK setup time | 50 | ns | ||

| tSLOADH | SCLK to SEN hold time | 50 | ns | ||

| tDSU | SDIN setup time | 10 | ns | ||

| tDH | SDIN hold time | 10 | ns | ||

| tSDOUT | Delay between SCLK falling edge to SDOUT | 10 | ns | ||

Table 27. SPI Input Description

| SPI BIT | DESCRIPTION | OPTIONS |

|---|---|---|

| R/W bit | Read/write bit | 0 = SPI write 1 = SPI read back |

| M bit | SPI bank access | 0 = Analog SPI bank (master) 1 = All digital SPI banks (main digital, interleaving, decimation filter, JESD digital, and so forth) |

| P bit | JESD page selection bit | 0 = Page access 1 = Register access |

| CH bit | SPI access for a specific channel of the JESD SPI bank | 0 = Channel A 1 = Channel B |

| ADDR[11:0] | SPI address bits | — |

| DATA[7:0] | SPI data bits | — |

Figure 116 shows the SDOUT timing when data are read back from a register. Data are placed on the SDOUT bus at the SCLK falling edge so that the data can be latched at the SCLK rising edge by the external receiver.

Figure 116. SDOUT Timing

Figure 116. SDOUT Timing

8.4.3.1 Serial Register Write: Analog Bank

The internal register of the ADC32RF45 analog bank (Figure 117) can be programmed by:

- Driving the SEN pin low.

- Initiating a serial interface cycle selecting the page address of the register whose content must be written. To select the master page: write address 0012h with 04h. To select the ADC page: write address 0011h with FFh.

- Writing the register content. When a page is selected, multiple registers located in the same page can be programmed.

Figure 117. SPI Write Timing Diagram for the Analog Bank

Figure 117. SPI Write Timing Diagram for the Analog Bank

8.4.3.2 Serial Register Readout: Analog Bank

Contents of the registers located in the two pages of the analog bank (Figure 118) can be readback by:

- Driving the SEN pin low.

- Selecting the page address of the register whose content must be read. Master page: write address 0012h with 04h. ADC page: write address 0011h with FFh.

- Setting the R/W bit to 1 and writing the address to be read back.

- Reading back the register content on the SDOUT pin. When a page is selected, the contents of multiple registers located in same page can be readback.

Figure 118. SPI Read Timing Diagram for the Analog Bank

Figure 118. SPI Read Timing Diagram for the Analog Bank

8.4.3.3 Serial Register Write: Digital Bank

The digital bank contains seven pages (Offset Corrector Page for channel A and B; Digital Gain Page for channel A and B; Main digital Page for channel A and B; and JESD Digital Page). The timing for the individual page selection is shown in Figure 119. The registers located in the pages of the digital bank can be programmed by:

- Driving the SEN pin low.

- Setting the M bit to 1 and specifying the page with with the desired register. There are seven pages in Digital Bank. These pages can be selected by appropriately programming register bits DIGITAL BANK PAGE SEL, located in addresses 002h, 003h, and 004h, using three consecutive SPI cycles. Addressing in a SPI cycle begins with 4xxx when selecting a page from digital bank because the M bit must be set to 1.

- To select the offset corrector page channel A: write address 4004h with 61h, 4003h with 00h, and 4002h with 00h.

- To select the offset corrector page channel B: write address 4004h with 61h, 4003h with 01h, and 4002h with 00h.

- To select the digital gain page channel A: write address 4004h with 61h, 4003h with 00h, and 4002h with 05h.

- To select the digital gain page channel B: write address 4004h with 61h, 4003h with 01h, and 4002h with 05h.

- To select the main digital page channel A: write address 4004h with 68h, 4003h with 00h, and 4002h with 00h.

- To select the main digital page channel B: write address 4004h with 68h, 4003h with 01h, and 4002h with 00h.

- To select the JESD digital page: write address 4004h with 69h, 4003h with 00h, and 4002h with 00h.

- Writing into the desired register by setting both the M bit and P bit to 1. Write register content. When a page is selected, multiple writes into the same page can be done. Addressing in an SPI cycle begins with 6xxx when selecting a page from the digital bank because the M bit must be set to 1, as shown in Figure 120.

Figure 119. SPI Write Timing Diagram for Digital Bank Page Selection

Figure 119. SPI Write Timing Diagram for Digital Bank Page Selection

Note that the JESD digital page is common for both channels. The CH bit can be used to distinguish between two channels when programming registers in the JESD digital page. When CH = 0, registers are programmed for channel B; when CH = 1, registers are programmed for channel A. Thus, an SPI cycle to program registers for channel B begins with 6xxx and channel A begins with 7xxx.

Figure 120. SPI Write Timing Diagram for Digital Bank Register Write

Figure 120. SPI Write Timing Diagram for Digital Bank Register Write

8.4.3.4 Serial Register Readout: Digital Bank

Readback of the register in one of the digital banks (as shown in Figure 121) can be accomplished by:

- Driving the SEN pin low.

- Selecting the page in the digital page: follow step 2 in the Serial Register Write: Digital Bank section.

- Set the R/W, M, and P bits to 1, select channel A or channel B, and write the address to be read back.

- JESD digital page: use the CH bit to select channel B (CH = 0) or channel A (CH = 1).

- Read back the register content on the SDOUT pin. When a page is selected, multiple read backs from the same page can be done.

Figure 121. SPI Read Timing Diagram for the Digital Bank

Figure 121. SPI Read Timing Diagram for the Digital Bank

8.4.3.5 Serial Register Write: Decimation Filter and Power Detector Pages

The decimation filter and power detector pages are special pages that accept direct addressing. The sampling clock and SYSREF signal are required to properly configure the decimation settings. Registers located in these pages can be programmed in one SPI cycle (Figure 122).

- Drive the SEN pin low.

- Directly write to the decimation filter or power detector pages. To program registers in these pages, set M = 1 and CH = 1. Additionally, address bit A[10] selects the decimation filter page (A[10] = 0) or the power detector page (A[10] = 1). Address bit A[11] selects channel A (A[11] = 0) or channel B (A[11] = 1).

- Decimation filter page: write address 50xxh for channel A or 58xxh for channel B.

- Power detector page: write address 54xxh for channel A or 5Cxxh for channel B.

Figure 122. SPI Write Timing Diagram for the Decimation and Power Detector Pages

Figure 122. SPI Write Timing Diagram for the Decimation and Power Detector Pages

8.5 Register Maps

The ADC32RF45 contains two main SPI banks. The analog SPI bank provides access to the ADC core and the digital SPI bank controls the digital blocks (including the serial JESD interface). Figure 123 and Figure 124 provide a conceptual view of the SPI registers inside the ADC32RF45. The analog SPI bank contains the master and ADC pages. The digital SPI bank is divided into multiple pages (the main digital, digital gain, decimation filter, JESD digital, and power detector pages).

Table 28 lists the register map for the ADC32RF45.

Table 28. Register Map

| REGISTER ADDRESS A[11:0] (Hex) |

REGISTER DATA | |||||||

|---|---|---|---|---|---|---|---|---|

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| GENERAL REGISTERS | ||||||||

| 000 | RESET | 0 | 0 | 0 | 0 | 0 | 0 | RESET |

| 002 | DIGITAL BANK PAGE SEL[7:0] | |||||||

| 003 | DIGITAL BANK PAGE SEL[15:8] | |||||||

| 004 | DIGITAL BANK PAGE SEL[23:16] | |||||||

| 010 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 3 or 4 WIRE |

| 011 | ADC PAGE SEL | |||||||

| 012 | 0 | 0 | 0 | 0 | 0 | MASTER PAGE SEL | 0 | 0 |

| MASTER PAGE (M = 0) | ||||||||

| 020 | 0 | 0 | 0 | PDN SYSREF | 0 | 0 | 0 | GLOBAL PDN |

| 032 | 0 | 0 | INCR CM IMPEDANCE | 0 | 0 | 0 | 0 | 0 |

| 039 | 0 | ALWAYS WRITE 1 | 0 | ALWAYS WRITE 1 | 0 | 0 | 0 | SYNC TERM DIS |

| 03C | 0 | SYSREF DEL EN | 0 | 0 | 0 | 0 | SYSREF DEL[4:3] | |

| 03D | 0 | 0 | 0 | 0 | 0 | JESD OUTPUT SWING | ||

| 05A | SYSREF DEL[2:0] | 0 | 0 | 0 | 0 | 0 | ||

| 057 | 0 | 0 | 0 | SEL SYSREF REG | ASSERT SYSREF REG | 0 | 0 | 0 |

| 058 | 0 | 0 | SYNCB POL | 0 | 0 | 0 | 0 | 0 |

| ADC PAGE (FFh, M = 0) | ||||||||

| 03F | 0 | 0 | 0 | 0 | 0 | SLOW SP EN1 | 0 | 0 |

| 042 | 0 | 0 | 0 | SLOW SP EN2 | 0 | 0 | 0 | 0 |

| Offset Corr Page Channel A (610000h, M = 1) | ||||||||

| 68 | FREEZE OFFSET CORR | 0 | ALWAYS WRITE 1 | 0 | 0 | DIS OFFSET CORR | ALWAYS WRITE 1 | 0 |

| Offset Corr Page Channel B (610100h, M = 1) | ||||||||

| 68 | FREEZE OFFSET CORR | 0 | ALWAYS WRITE 1 | 0 | 0 | DIS OFFSET CORR | ALWAYS WRITE 1 | 0 |

| Digital Gain Page Channel A (610005, M = 1) | ||||||||

| 0A6 | 0 | 0 | 0 | 0 | DIGITAL GAIN | |||

| Digital Gain Page Channel B (610105, M = 1) | ||||||||

| 0A6 | 0 | 0 | 0 | 0 | DIGITAL GAIN | |||

| Main Digital Page Channel A (680000h, M = 1) | ||||||||

| 000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DIG CORE RESET GBL |

| 0A2 | 0 | 0 | 0 | 0 | NQ ZONE EN | NYQUIST ZONE | ||

| Main Digital Page Channel B (680001h, M = 1) | ||||||||

| 000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0A2 | 0 | 0 | 0 | 0 | NQ ZONE EN | NYQUIST ZONE | ||

| JESD DIGITAL PAGE (690000h, M = 1) | ||||||||

| 001 | CTRL K | 0 | 0 | TESTMODE EN | 0 | LANE ALIGN | FRAME ALIGN | TX LINK DIS |

| 002 | SYNC REG | SYNC REG EN | 0 | 0 | 12BIT MODE | JESD MODE0 | ||

| 003 | LINK LAYER TESTMODE | LINK LAY RPAT | LMFC MASK RESET | JESD MODE1 | JESD MODE2 | RAMP 12BIT | ||

| 004 | 0 | 0 | 0 | 0 | 0 | 0 | REL ILA SEQ | |

| 006 | SCRAMBLE EN | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 007 | 0 | 0 | 0 | FRAMES PER MULTIFRAME (K) | ||||

| 016 | 0 | 40X MODE | 0 | 0 | 0 | 0 | ||

| 017 | 0 | 0 | 0 | 0 | LANE0 POL |

LANE1 POL |

LANE2 POL |

LANE3 POL |

| 032 | SEL EMP LANE 0 | 0 | 0 | |||||

| 033 | SEL EMP LANE 1 | 0 | 0 | |||||

| 034 | SEL EMP LANE 2 | 0 | 0 | |||||

| 035 | SEL EMP LANE 3 | 0 | 0 | |||||

| 036 | 0 | CMOS SYNCB | 0 | 0 | 0 | 0 | 0 | 0 |

| 037 | 0 | 0 | 0 | 0 | 0 | 0 | PLL MODE | |

| 03E | 0 | MASK CLKDIV SYSREF | MASK NCO SYSREF | 0 | 0 | 0 | 0 | 0 |

| DECIMATION FILTER PAGE (Direct Addressing, 16-Bit Address, 5000h for Channel A and 5800h for Channel B) | ||||||||

| 000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DDC EN |

| 001 | 0 | 0 | 0 | 0 | DECIM FACTOR | |||

| 002 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DUAL BAND EN |

| 005 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | REAL OUT EN |

| 006 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DDC MUX |

| 007 | DDC0 NCO1 LSB | |||||||

| 008 | DDC0 NCO1 MSB | |||||||

| 009 | DDC0 NCO2 LSB | |||||||

| 00A | DDC0 NCO2 MSB | |||||||

| 00B | DDC0 NCO3 LSB | |||||||

| 00C | DDC0 NCO3 MSB | |||||||

| 00D | DDC1 NCO4 LSB | |||||||

| 00E | DDC1 NCO4 MSB | |||||||

| 00F | 0 | 0 | 0 | 0 | 0 | 0 | 0 | NCO SEL PIN |

| 010 | 0 | 0 | 0 | 0 | 0 | 0 | NCO SEL | |

| 011 | 0 | 0 | 0 | 0 | 0 | 0 | LMFC RESET MODE | |

| 014 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DDC0 6DB GAIN |

| 016 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | DDC1 6DB GAIN |

| 01E | 0 | DDC DET LAT | 0 | 0 | 0 | 0 | ||

| 01F | 0 | 0 | 0 | 0 | 0 | 0 | 0 | WBF 6DB GAIN |

| 033 | CUSTOM PATTERN1[7:0] | |||||||

| 034 | CUSTOM PATTERN1[15:8] | |||||||

| 035 | CUSTOM PATTERN2[7:0] | |||||||

| 036 | CUSTOM PATTERN2[15:8] | |||||||

| 037 | 0 | 0 | 0 | 0 | TEST PATTERN SEL | |||

| 03A | 0 | 0 | 0 | 0 | 0 | 0 | TEST PAT RES | TP RES EN |

| POWER DETECTOR PAGE (Direct Addressing, 16-Bit Address, 5400h for Channel A and 5C00h for Channel B) | ||||||||

| 000 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | PKDET EN |

| 001 | BLKPKDET [7:0] | |||||||

| 002 | BLKPKDET [15:8] | |||||||

| 003 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | BLKPKDET [16] |

| 007 | BLKTHHH | |||||||

| 008 | BLKTHHL | |||||||

| 009 | BLKTHLH | |||||||

| 00A | BLKTHLL | |||||||

| 00B | DWELL[7:0] | |||||||

| 00C | DWELL[15:8] | |||||||

| 00D | 0 | 0 | 0 | 0 | 0 | 0 | 0 | FILT0LPSEL |

| 00E | 0 | 0 | 0 | 0 | TIMECONST | |||

| 00F | FIL0THH[7:0] | |||||||

| 010 | FIL0THH[15:8] | |||||||

| 011 | FIL0THL[7:0] | |||||||

| 012 | FIL0THL[15:8] | |||||||

| 013 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | IIR0 2BIT EN |

| 016 | FIL1THH[7:0] | |||||||

| 017 | FIL1THH[15:8] | |||||||

| 018 | FIL1THL[7:0] | |||||||

| 019 | FIL1THL[15:8] | |||||||

| 01A | 0 | 0 | 0 | 0 | 0 | 0 | 0 | IIR1 2BIT EN |

| 01D | DWELLIIR[7:0] | |||||||

| 01E | DWELLIIR[15:8] | |||||||

| 020 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | IIR0 2BIT EN |

| 021 | 0 | 0 | 0 | PWRDETACCU | ||||

| 022 | PWRDETH[7:0] | |||||||

| 023 | PWRDETH[15:8] | |||||||

| 024 | PWRDETL[7:0] | |||||||

| 025 | PWRDETL[15:8] | |||||||

| POWER DETECTOR PAGE (continued) | ||||||||

| 027 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | RMS 2BIT EN |

| 02B | 0 | 0 | 0 | RESET AGC | 0 | 0 | 0 | 0 |

| 032 | OUTSEL GPIO1 | |||||||

| 033 | OUTSEL GPIO2 | |||||||

| 034 | OUTSEL GPIO3 | |||||||

| 035 | OUTSEL GPIO4 | |||||||

| 037 | 0 | 0 | 0 | 0 | IODIR GPIO4 | IODIR GPIO3 | IODIR GPIO2 | IODIR GPIO1 |

| 038 | 0 | 0 | INSEL1 | 0 | 0 | INSEL0 | ||

8.5.1 Example Register Writes

This section provides three different example register writes. Table 29 describes a global power-down register write, Table 30 describes the register writes when the scrambler is enabled, and Table 31 describes the register writes for 8X decimation for channels A and B (complex output, 1 DDC mode) with the NCO set to 1.8 GHz (fS = 3 GSPS) and the JESD format configured to LMFS = 4421.

Table 29. Global Power-Down

| ADDRESS | DATA | COMMENT |

|---|---|---|

| 12h | 04h | Set the master page |

| 20h | 01h | Set the global power-down |

Table 30. Scrambler Enable

| ADDRESS | DATA | COMMENT |

|---|---|---|

| 4004h | 69h | Select the digital JESD page |

| 4003h | 00h | |

| 6006h | 80h | Scrambler enable, channel A |

| 7006h | 80h | Scrambler enable, channel B |

Table 31. 8X Decimation for Channel A and B

| ADDRESS | DATA | COMMENT |

|---|---|---|

| 4004h | 68h | Select the main digital page for channel A |

| 4003h | 00h | |

| 6000h | 01h | Issue a digital reset for channel A |

| 6000h | 00h | Clear the digital for reset channel A |

| 4003h | 01h | Select the main digital page for channel B |

| 6000h | 01h | Issue a digital reset for channel B |

| 6000h | 00h | Clear the digital reset for channel B |

| 4004h | 69h | Select the digital JESD page |

| 4003h | 00h | |

| 6002h | 01h | Set JESD MODE0 = 1, channel A |

| 7002h | 01h | Set JESD MODE0 = 1, channel B |

| 5000h | 01h | Enable the DDC, channel A |

| 5001h | 02h | Set decimation to 8X complex |

| 5007h | 9Ah | Set the LSB of DDC0, NCO1 to 9Ah (fNCO = 1.8 GHz, fS = 3 GSPS) |

| 5008h | 99h | Set the MSB of DDC0, NCO1 to 99h (fNCO = 1.8 GHz, fS = 3 GSPS) |

| 5014h | 01h | Enable the 6-dB digital gain of DDC0 |

| 5801h | 02h | Set decimation to 8X complex |

| 5807h | 9Ah | Set the LSB of DDC0, NCO1 to 9Ah (fNCO = 1.8 GHz, fS = 3 GSPS) |

| 5808h | 99h | Set the MSB of DDC0, NCO1 to 99h (fNCO = 1.8 GHz, fS = 3 GSPS) |

| 5814h | 01h | Enable the 6-dB digital gain of DDC0 |

8.5.2 Register Descriptions

8.5.2.1 General Registers

8.5.2.1.1 Register 000h (address = 000h), General Registers

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| RESET | 0 | 0 | 0 | 0 | 0 | 0 | RESET |

| R/W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | W-0h | R/W-0h |