ZHCSBH5C May 2013 – August 2016 ADS1220

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 引脚配置和功能

- 6 技术规格

- 7 参数测量信息

- 8 详细 说明

- 9 应用和实施

- 10电源相关建议

- 11布局布线

- 12器件和文档支持

- 13机械、封装和可订购信息

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

- RVA|16

订购信息

6 技术规格

6.1 绝对最大额定值(1)

(1) 超出绝对最大额定值下列出的应力值可能会对器件造成永久损坏。这些仅为在应力额定值下的工作情况,对于额定值下的器件的功能性操作以及在超出推荐的操作条件下的任何其它操作,在此并未说明。在绝对最大额定值条件下长时间运行会影响器件可靠性。

6.2 ESD 额定值

| 值 | 单位 | |||

|---|---|---|---|---|

| V(ESD) | 静电放电 | 人体放电模式 (HBM),符合 ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| 组件充电模式 (CDM),符合 JEDEC 规范 JESD22-C101(2) | ±500 | |||

(1) JEDEC 文档 JEP155 规定:500V HBM 能够在标准 ESD 控制流程下安全生产。

(2) JEDEC 文档 JEP157 规定:250V CDM 能够在标准 ESD 控制流程下安全生产。

6.3 建议的工作条件

在工作环境温度范围内(除非另外注明)| 最小值 | 标称值 | 最大值 | 单位 | |||

|---|---|---|---|---|---|---|

| 电源 | ||||||

| 单极模拟电源 | AVDD 至 AVSS | 2.3 | 5.5 | V | ||

| AVSS 至 DGND | -0.1 | 0 | 0.1 | |||

| 双极模拟电源 | AVDD 至 DGND | 2.3 | 2.5 | 2.75 | V | |

| AVSS 至 DGND | –2.75 | -2.5 | -2.3 | |||

| 数字电源 | DVDD 至 DGND | 2.3 | 5.5 | V | ||

| 模拟输入(1) | ||||||

| VIN | 差分输入电压 | VIN = V(AINP) – V(AINN)(2) | –Vref / 增益 | Vref / 增益 | V | |

| V(AINx) | 绝对输入电压 | PGA 禁用,增益 = 1 至 4 | AVSS – 0.1 | AVDD + 0.1 | V | |

| PGA 启用,增益 = 1 至 128 | 请参见低噪声 PGA 部分 | |||||

| VCM | 共模输入电压 | PGA 禁用,增益 = 1 至 4 | AVSS – 0.1 | AVDD + 0.1 | V | |

| PGA 启用,增益 = 1 至 128 | 请参见低噪声 PGA 部分 | |||||

| 基准电压输入(3) | ||||||

| Vref | 差分基准输入电压 | Vref = V(REFPx) – V(REFNx) | 0.75 | 2.5 | AVDD | V |

| V(REFNx) | 绝对负基准电压 | AVSS – 0.1 | V(REFPx) – 0.75 | V | ||

| V(REFPx) | 绝对正基准电压 | V(REFNx) + 0.75 | AVDD + 0.1 | V | ||

| 外部时钟源 | ||||||

| f(CLK) | 外部时钟频率 | 0.5 | 4.096 | 4.5 | MHz | |

| 占空比 | 40% | 60% | ||||

| 数字输入 | ||||||

| 输入电压 | DGND | DVDD | V | |||

| 温度范围 | ||||||

| TA | 运行环境温度 | –40 | 125 | °C | ||

(1) AINP 和 AINN 表示 PGA 的正负输入。AINx 表示提供的四个模拟输入之一。

PGA 禁用表示关闭并旁路低噪声 PGA。在这种情况下,仍支持增益值 1、2 和 4。

更多相关信息,请参见章节。

PGA 禁用表示关闭并旁路低噪声 PGA。在这种情况下,仍支持增益值 1、2 和 4。

更多相关信息,请参见章节。

(2) 排除偏移和增益误差的影响。

当启用 PGA 时,限制为 ±[(AVDD – AVSS) – 0.4V] / 增益。

当启用 PGA 时,限制为 ±[(AVDD – AVSS) – 0.4V] / 增益。

(3) REFPx 和 REFNx 表示提供的两个差分基准输入对之一。

6.4 热性能信息

| 热指标(1) | ADS1220 | 单位 | ||

|---|---|---|---|---|

| VQFN (RVA) | TSSOP (PW) | |||

| 16 引脚 | 16 引脚 | |||

| RθJA | 结至环境热阻 | 43.4 | 99.5 | °C/W |

| RθJC(top) | 结至外壳(顶部)热阻 | 47.3 | 35.2 | °C/W |

| RθJB | 结至电路板热阻 | 18.4 | 44.3 | °C/W |

| ψJT | 管结至顶部的特征参数 | 0.6 | 2.4 | °C/W |

| ψJB | 管结至电路板的特征参数 | 18.4 | 43.8 | °C/W |

| RθJC(bot) | 结至外壳(底部)热阻 | 2.0 | 不适用 | °C/W |

(1) 有关传统和新热指标的详细信息,请参见应用报告《IC 封装热指标》(文献编号:SPRA953)。

6.5 电气特性

最小和最大规范值适用于 TA = –40°C 至 +125°C 的温度范围。典型规范值在 TA = 25°C 下测定。所有规范值均在 AVDD = 3.3V、AVSS = 0V、DVDD = 3.3V、PGA 启用、DR = 20SPS 以及外部 Vref = 2.5V 的情况下测定(除非另外注明)。(1)

| 参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 | ||

|---|---|---|---|---|---|---|---|

| 模拟输入 | |||||||

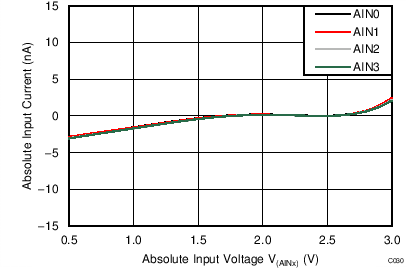

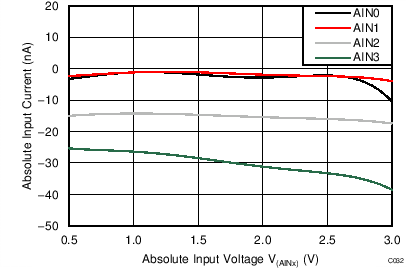

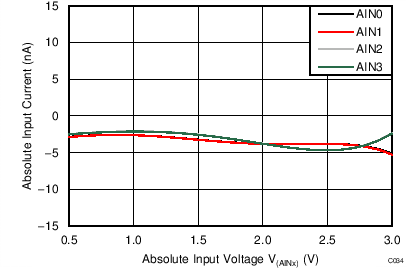

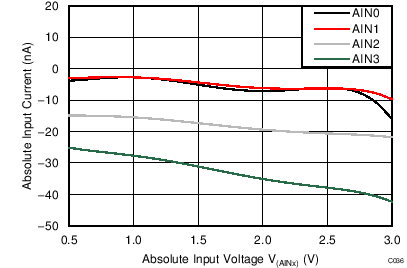

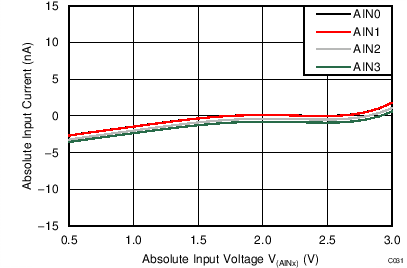

| 绝对输入电流 | 请参见 典型特性 | ||||||

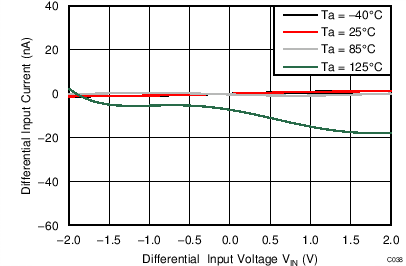

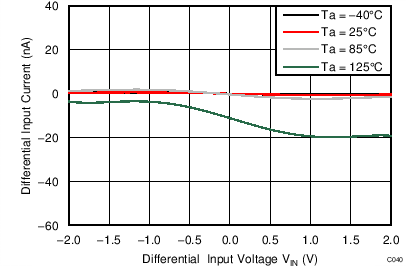

| 差分输入电流 | 请参见 典型特性 | ||||||

| 系统性能 | |||||||

| 分辨率(无代码丢失) | 24 | 位 | |||||

| DR | 数据传输速率 | 正常模式 | 20、45、90、175、330、600、1000 | SPS | |||

| 占空比模式 | 5、11.25、22.5、44、82.5、150、250 | ||||||

| Turbo 模式 | 40、90、180、350、660、1200、2000 | ||||||

| 输入参考噪声 | 请参见噪声性能部分 | ||||||

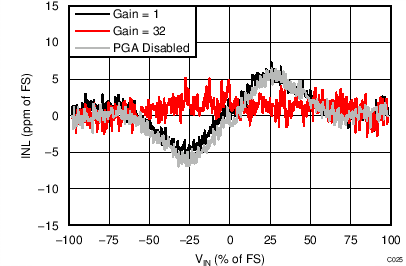

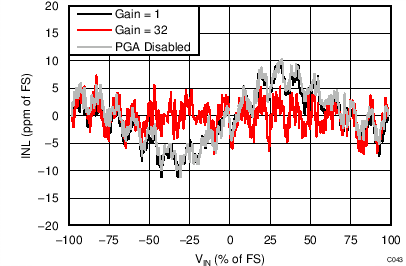

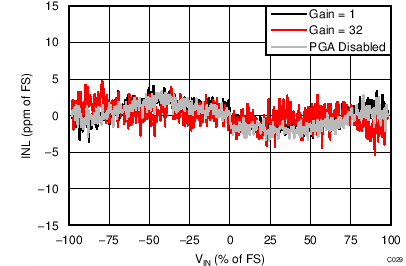

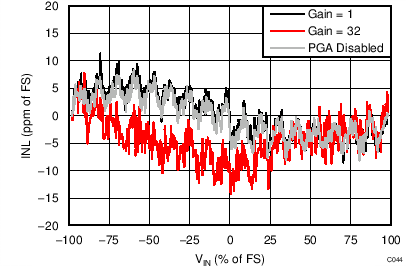

| INL | 积分非线性 | 增益 = 1 至 128,VCM = 0.5 AVDD,最适条件(2) | -15 | ±6 | 15 | ppmFSR | |

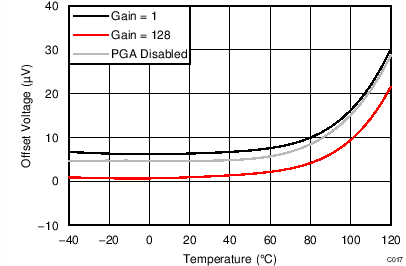

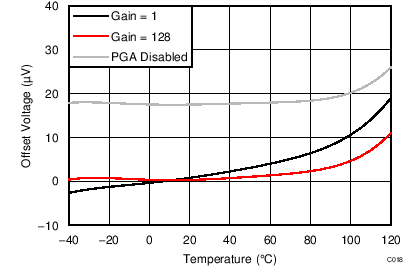

| VIO | 输入偏移电压) | PGA 禁用,增益 = 1 至 4,差分输入 | ±4 | µV | |||

| 增益 = 1,差分输入,TA = 25°C | -30 | ±4 | 30 | ||||

| 增益 = 2 至 128,差分输入 | ±4 | ||||||

| 偏移漂移 | PGA 禁用,增益 = 1 至 4 | 0.25 | µV/°C | ||||

| 增益 = 1 至 128,TA = –40°C 至 +85°C(2) | 0.08 | 0.3 | |||||

| 增益 = 1 至 128 | 0.25 | ||||||

| 偏移匹配 | 在任意两输入间匹配 | ±20 | µV | ||||

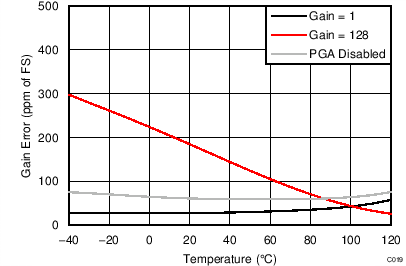

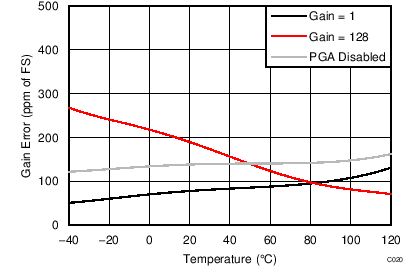

| 增益误差 | PGA 禁用,增益 = 1 至 4 | ±0.015% | |||||

| 增益 = 1 至 128,TA = 25°C | –0.1% | ±0.015% | 0.1% | ||||

| 增益漂移 | PGA 禁用,增益 = 1 至 4 | 1 | ppm/ °C | ||||

| 增益 = 1 至 128(2) | 1 | 4 | |||||

| NMRR | 常模抑制比(2) | 50Hz ±3%,DR = 20SPS,外部 CLK,50/60 位 = 10 | 105 | dB | |||

| 60Hz ±3%,DR = 20SPS,外部 CLK,50/60 位 = 11 | 105 | ||||||

| 50Hz 或 60Hz ±3%,DR = 20SPS, 外部 CLK,50/60 位 = 01 |

90 | ||||||

| CMRR | 共模抑制比 | 直流条件下的增益 = 1 | 90 | 105 | dB | ||

| f(CM) = 50Hz,DR = 2000SPS(2) | 95 | 115 | |||||

| f(CM) = 60Hz,DR = 2000SPS(2) | 95 | 115 | |||||

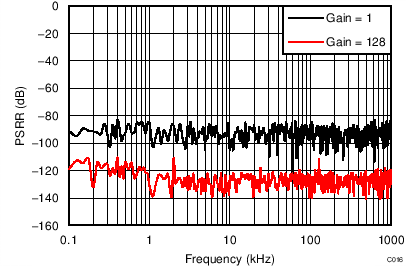

| PSRR | 电源抑制比 | 直流条件下的 AVDD,VCM = 0.5 AVDD,增益 = 1 | 80 | 105 | dB | ||

| 直流条件下的 DVDD,VCM = 0.5 AVDD,增益 = 1(2) | 100 | 115 | |||||

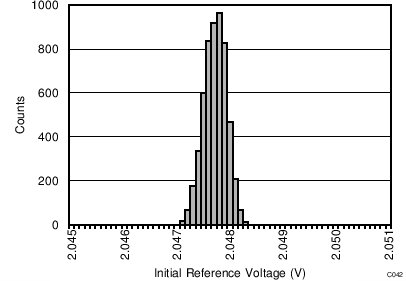

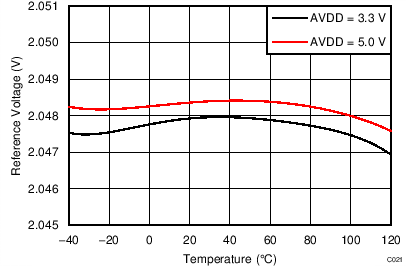

| 内部参考基准 | |||||||

| 初始精度 | TA = 25°C | 2.045 | 2.048 | 2.051 | V | ||

| 基准漂移(2) | ) | 5 | 30 | ppm/°C | |||

| 长期漂移 | 1000 小时 | 110 | ppm | ||||

| 电压基准输入 | |||||||

| 基准输入电流 | REFP0 = Vref,REFN0 = AVSS | ±10 | nA | ||||

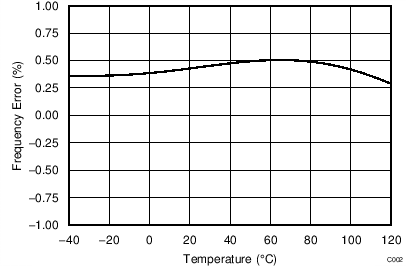

| 内部振荡器 | |||||||

| 内部振荡器精度 | 正常模式 | -2% | ±1% | 2% | |||

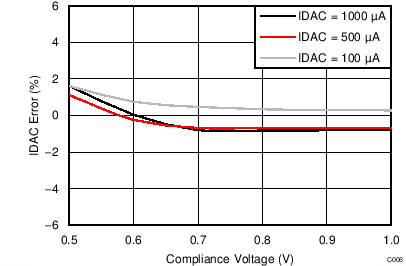

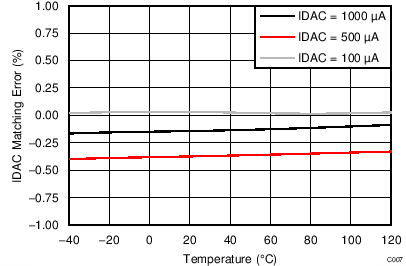

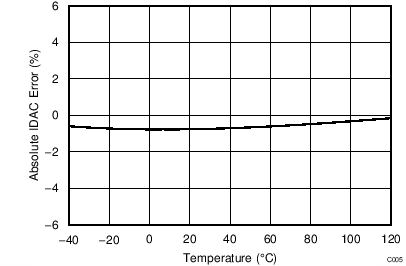

| 激励电流源 (IDAC) | |||||||

| 电流设置 | 10、50、100、250、500、1000、1500 | µA | |||||

| 合规电压 | 所有电流设置 | AVDD – 0.9 | V | ||||

| 精度 | 所有电流设置,每个 IDAC | –6% | ±1% | 6% | |||

| 电流匹配 | IDAC 之间(对于 10µA 设置无效) | ±0.3% | |||||

| 温度漂移 | 每个 IDAC(对于 10µA 设置无效) | 50 | ppm/ °C | ||||

| 温度漂移匹配) | IDAC 之间(对于 10µA 设置无效) | 10 | ppm/ °C | ||||

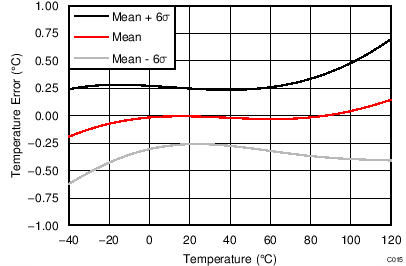

| 温度传感器 | |||||||

| 转换分辨率 | 14 | 位数 (Bit) | |||||

| 温度分辨率 | 0.03125 | °C | |||||

| 精度 | TA = 0°C 至 +75°C | -0.5 | ±0.25 | 0.5 | °C | ||

| TA = -40°C 至 +125°C | -1 | ±0.5 | 1 | ||||

| 精度与模拟电源电压间的关系 | 0.0625 | 0.25 | °C/V | ||||

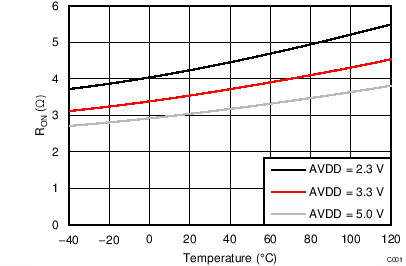

| 低侧电源开关 | |||||||

| RON | 导通电阻 | 3.5 | 5.5 | Ω | |||

| 流经开关的电流 | 30 | mA | |||||

| 数字输入/输出 | |||||||

| VIH | 高电平输入电压 | 0.7 DVDD | DVDD | V | |||

| VIL | 低电平输入电压 | ) | DGND | 0.3 DVDD | V | ||

| VOH | 高电平输出电压 | IOH = 3mA | 0.8 DVDD | V | |||

| VOL | 低电平输出电压 | IOL = 3mA | 0.2 DVDD | V | |||

| IH | 输入漏电流,高电平 | VIH = 5.5V | –10 | 10 | µA | ||

| IL | 输入漏电流,低电平 | VIL = DGND | –10 | 10 | µA | ||

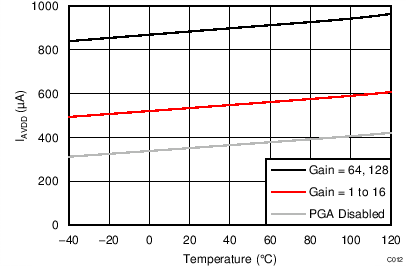

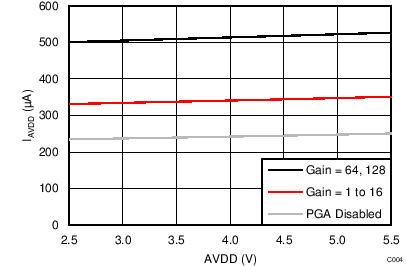

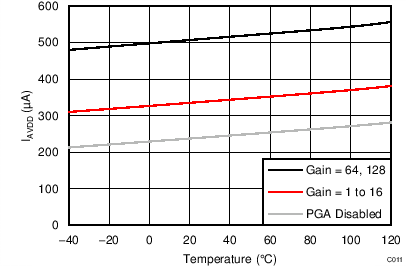

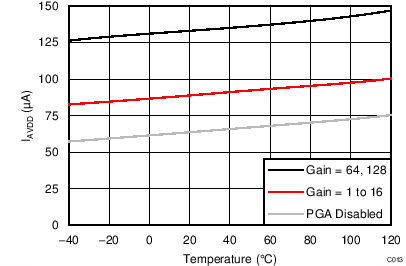

| 电源 | |||||||

| IAVDD | 模拟电源电流(3) | 掉电模式 | 0.1 | 3 | µA | ||

| 占空比模式,PGA 禁用 | 65 | ||||||

| 占空比模式,增益 = 1 至 16 | 95 | ||||||

| 占空比模式,增益 = 32 | 115 | ||||||

| 占空比模式,增益 = 64、128 | 135 | ||||||

| 正常模式,PGA 禁用 | 240 | ||||||

| 正常模式,增益 = 1 至 16 | 340 | 490 | |||||

| 正常模式,增益 = 32 | 425 | ||||||

| 正常模式,增益 = 64、128 | 510 | ||||||

| Turbo 模式,PGA 禁用 | 360 | ||||||

| Turbo 模式,增益 = 1 至 16 | 540 | ||||||

| Turbo 模式,增益 = 32 | 715 | ||||||

| Turbo 模式,增益 = 64、128 | 890 | ||||||

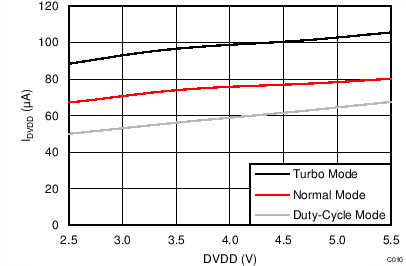

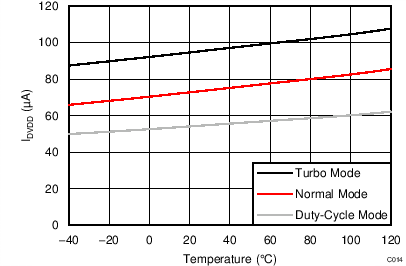

| IDVDD | 数字电源电流(3) | 掉电模式 | 0.3 | 5 | µA | ||

| 占空比模式 | 55 | ||||||

| 正常模式 | 75 | 110 | |||||

| Turbo 模式 | 95 | ||||||

| PD | 功耗(3) | 占空比模式,PGA 禁用 | 0.4 | mW | |||

| 正常模式,增益 = 1 至 16 | 1.4 | ||||||

| Turbo 模式,增益 = 1 至 16 | 2.1 | ||||||

(2) 通过设计和特性分析数据确保最小值和最大值。

(3) 已选择内部电压基准,启用内部振荡器,IDAC 关闭,同时处于持续转换模式。

选择外部基准时,模拟电源电流通常增加 70µA(正常模式,Turbo 模式)。

启用 IDAC 时,模拟电源电流通常增加 190µA(排除实际 IDAC 电流)。

选择外部基准时,模拟电源电流通常增加 70µA(正常模式,Turbo 模式)。

启用 IDAC 时,模拟电源电流通常增加 190µA(排除实际 IDAC 电流)。

6.6 SPI 时序要求

在工作环境温度范围内,DVDD = 2.3V 至 5.5V(除非另外注明)| 最小值 | 最大值 | 单位 | |||

|---|---|---|---|---|---|

| td(CSSC) | 延迟时间,CS 下降沿至第一个 SCLK 上升沿(2) | 50 | ns | ||

| td(SCCS) | 延迟时间,最终 SCLK 下降沿至 CS 上升沿 | 25 | ns | ||

| tw(CSH) | 脉冲持续时间,CS 为高电平 | 50 | ns | ||

| tc(SC) | SCLK 周期 | 150 | ns | ||

| tw(SCH) | 脉冲持续时间,SCLK 为高电平 | 60 | ns | ||

| tw(SCL) | 脉冲持续时间,SCLK 为低电平 | 60 | ns | ||

| tsu(DI) | 建立时间,DIN 在 SCLK 下降沿前有效 | 50 | ns | ||

| th(DI) | 保持时间,DIN 在 SCLK 下降沿后有效 | 25 | ns | ||

| SPI 超时(1) | 正常模式,占空比模式 | 13955 | t(MOD) | ||

| Turbo 模式 | 27910 | t(MOD) | |||

(1) 更多相关信息,请参见 SPI 超时部分。

t(MOD) = 1 / f(MOD)。使用内部振荡器或 4.096MHz 外部时钟时,调制器频率 f(MOD) = 256kHz(正常模式,占空比模式)和 512kHz(Turbo 模式)。

t(MOD) = 1 / f(MOD)。使用内部振荡器或 4.096MHz 外部时钟时,调制器频率 f(MOD) = 256kHz(正常模式,占空比模式)和 512kHz(Turbo 模式)。

(2) 当不与其他任何器件共享总线时,CS 可永久连接低电平。

注:图中所示为单字节通信。实际通信可能涉及多个字节。

Figure 1. 串行接口时序要求

6.7 SPI 开关特性

在工作环境温度范围内,DVDD = 2.3V 至 5.5V(除非另外注明)| 参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 | |

|---|---|---|---|---|---|---|

| tp(CSDO) | 传播延迟时间, CS 下降沿至 DOUT 驱动 |

DOUT 负载 = 20pF || 10kΩ,与 DGND 相连 | 50 | ns | ||

| tp(SCDO) | 传播延迟时间, SCLK 上升沿至新的有效 DOUT |

DOUT 负载 = 20pF || 10kΩ,与 DGND 相连 | 0 | 50 | ns | |

| tp(CSDOZ) | 传播延迟时间, CS 上升沿至 DOUT 高阻抗 |

DOUT 负载 = 20pF || 10kΩ,与 DGND 相连 | 50 | ns | ||

注:图中所示为单字节通信。实际通信可能涉及多个字节。

Figure 2. 串行接口开关特性

6.8 典型特性

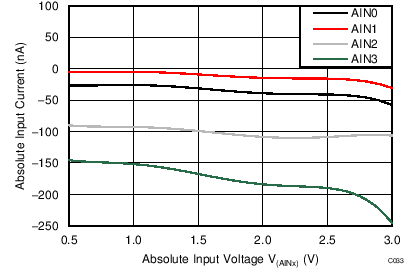

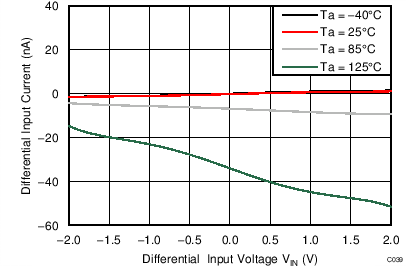

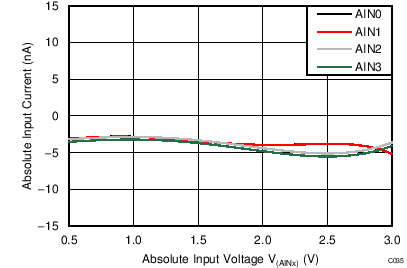

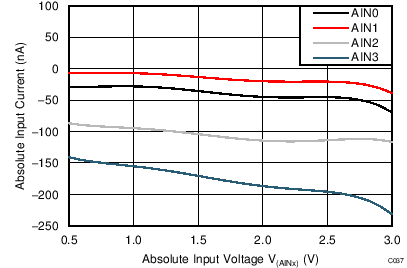

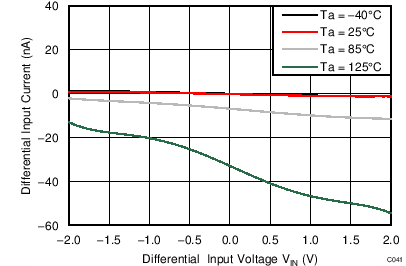

TA = 25°C 时,AVDD = 3.3V,AVSS = 0V,已启用 PGA 并使用外部基准 Vref = 2.5V (除非另外注明)。

| AVDD = 3.3V |

| AVDD = 3.3V,2.5V 外部基准电压,正常模式 |

差分输入信号间的关系

| AVDD = 3.3V,内部基准电压,正常模式 |

差分输入信号间的关系

| TA = 25°C,5490 器件的数据 |

| DVDD = 3.3V,正常模式 |

| AVDD = 3.3V,PGA 启用,TA = –40°C |

绝对输入电压间的关系

| AVDD = 3.3V,PGA 启用,TA = 85°C |

绝对输入电压间的关系

| AVDD = 3.3V,PGA 启用,AINP = AIN0,AINN = AIN1 |

差分输入电压间的关系

| AVDD = 3.3V,PGA 禁用,TA = –40°C |

绝对输入电压间的关系

| AVDD = 3.3V,PGA 禁用,TA = 85°C |

绝对输入电压间的关系

| AVDD = 3.3V,PGA 禁用,AINP = AIN0,AINN = AIN1 |

差分输入电压间的关系

| AVDD = 3.3V,内部基准电压,Turbo 模式 |

| 正常模式,内部基准电压 |

| DVDD = 3.3V |

| AVDD = 5.0V |

| AVDD = 5.0V |

| AVDD = 5.0V,2.5V 外部基准电压,正常模式 |

差分输入信号间的关系

| AVDD = 5.0V,内部基准电压,正常模式 |

差分输入信号间的关系

| AVDD = 3.3V,PGA 启用,TA = 25°C |

绝对输入电压间的关系

| AVDD = 3.3V,PGA 启用,TA = 125°C |

绝对输入电压间的关系

| AVDD = 3.3V,PGA 启用,AINP = AIN3,AINN = AIN2 |

差分输入电压间的关系

| AVDD = 3.3V,PGA 禁用,TA = 25°C |

绝对输入电压间的关系

| AVDD = 3.3V,PGA 禁用,TA = 125°C |

绝对输入电压间的关系

| AVDD = 3.3V,PGA 禁用,AINP = AIN3,AINN = AIN2 |

差分输入电压间的关系

| AVDD = 3.3V,内部基准电压,正常模式 |

| AVDD = 3.3V,内部基准电压,占空比模式 |