-

具有 UART 接口的 ADS122U04 24 位 4 通道 2kSPS Δ-Σ ADC

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Multiplexer

- 8.3.2 Low-Noise Programmable Gain Stage

- 8.3.3 Voltage Reference

- 8.3.4 Modulator and Internal Oscillator

- 8.3.5 Digital Filter

- 8.3.6 Conversion Times

- 8.3.7 Excitation Current Sources

- 8.3.8 Sensor Detection

- 8.3.9 System Monitor

- 8.3.10 Temperature Sensor

- 8.3.11 Offset Calibration

- 8.3.12 Conversion Data Counter

- 8.3.13 Data Integrity

- 8.3.14 General-Purpose Digital Inputs/Outputs

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Map

- 8.6.1 Configuration Registers

- 8.6.2

Register Descriptions

- 8.6.2.1 Configuration Register 0 (address = 00h) [reset = 00h]

- 8.6.2.2 Configuration Register 1 (address = 01h) [reset = 00h]

- 8.6.2.3 Configuration Register 2 (address = 02h) [reset = 00h]

- 8.6.2.4 Configuration Register 3 (address = 03h) [reset = 00h]

- 8.6.2.5 Configuration Register 4 (address = 04h) [reset = 00h]

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

- 重要声明

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

- RTE|16

订购信息

具有 UART 接口的 ADS122U04 24 位 4 通道 2kSPS Δ-Σ ADC

1 特性

- 电流消耗低至 315µA(典型值)

- 宽电源电压范围:2.3V 至 5.5V

- 可编程增益:1 至 128

- 可编程数据速率:高达 2kSPS

- 高达 20 位的有效分辨率

- 采用单周期稳定数字滤波器,在 20SPS 时实现同步 50Hz 和 60Hz 抑制

- 两个差分输入或四个单端输入

- 双匹配可编程电流源:

10μA 至 1.5mA - 集成 2.048V 基准电压:漂移 5ppm/°C(典型值)

- 集成 2% 精准振荡器

- 集成温度传感器:精度 0.5°C(典型值)

- 三个通用输入/输出

- 2 线 UART 兼容接口(8-N-1 格式),具有高达 120kBaud 的波特率和

自动波特率检测功能 - 封装:3.0mm × 3.0mm × 0.75mm WQFN

2 应用

- 传感器和变送器:

温度、压力、应力,流量 - 可编程逻辑控制器 (PLC) 和分布式控制系统 (DCS) 模拟输入模块

- 温度控制器

- 人工气候室,工业烘箱

- 患者监护系统:

体温、血压

3 说明

ADS122U04 是一款 24 位精密模数转换器 (ADC),集成了多种 特性, 能够降低系统成本并减少小型传感器信号测量 应用 中的组件数量。该器件 具有 通过灵活的输入多路复用器 (MUX) 实现的两个差分输入或四个单端输入、一个低噪声可编程增益放大器 (PGA)、两个可编程激励电流源、一个电压基准、一个振荡器以及一个精密温度传感器。

此器件能够以高达 2000 次/秒 (SPS) 采样数据速率执行转换,并且能够在单周期内稳定。针对噪声环境中的工业应用,当采样频率为 20SPS 时,数字滤波器可同时提供 50Hz 和 60Hz 抑制。内部 PGA 提供高达 128 的增益。此 PGA 使得 ADS122U04 非常适合可测量小传感器信号的 应用 ,例如电阻式温度检测器 (RTD)、热电偶、热敏电阻和阻性桥式传感器。

ADS122U04 具有 一个 2 线 UART 兼容接口。在需要电隔离的 应用 中,这种通用异步接收器/发送器 (UART) 接口可最大限度地减少数字隔离通道的数量,从而节省成本、减小布板空间和降低功耗。

ADS122U04 采用无引线的 16 引脚 WQFN 或 16 引脚 TSSOP 封装,额定工作温度范围为 –40°C 至 +125°C。

器件信息(1)

| 器件编号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| ADS122U04 | WQFN (16) | 3.00mm × 3.00mm |

| TSSOP (16) | 5.00mm × 4.40mm |

- 如需了解所有可用封装,请参阅数据表末尾的可订购米6体育平台手机版_好二三四附录。

Device Images

K 型热电偶测量

4 修订历史记录

Changes from A Revision (August 2017) to B Revision

- Changed Internal Voltage Reference, Accuracy parameter: added TSSOP package to test conditions of first row and added second row for the WQFN packageGo

- Added TSSOP package to conditions of Internal Reference Voltage Histogram figureGo

- Changed Digital Supply Current vs Temperature figureGo

- Changed Voltage Reference section locationGo

- Changed –3-dB bandwidth value in turbo mode 40 SPS parameter from 26.2 Hz to 17.1 HzGo

- Changed Offset Calibration section locationGo

- Changed FFh to FFFFh in Data Integrity sectionGo

- Changed description of power-on reset procedure in Power-On Reset sectionGo

- Added note to Data Format sectionGo

- Changed first paragraph of Data Integrity sectionGo

- Added Register Data Output with CRC Enabled figureGo

- Changed Conversion Data Output with CRC Enabled and Conversion Data Output with Inverted Data Output Enabled figure captionsGo

- Deleted conversion result from bit CRC[1:0] descriptionGo

- Changed 50 µs to 600 µs and changed (MUX[3:1] = 1110) to (MUX[3:0] = 1110) in Pseudo Code Example sectionGo

- Deleted Power-Supply Ramp Rate sectionGo

- Changed 50 µs to 600 µs in Power-Supply Sequencing sectionGo

Changes from * Revision (May 2017) to A Revision

- 进行生产发布Go

5 Pin Configuration and Functions

Pin Functions

| PIN | ANALOG OR DIGITAL

INPUT/OUTPUT |

DESCRIPTION(1) | ||

|---|---|---|---|---|

| NAME | NO. | |||

| RTE | PW | |||

| AIN0 | 9 | 11 | Analog input | Analog input 0 |

| AIN1 | 8 | 10 | Analog input | Analog input 1 |

| AIN2 | 5 | 7 | Analog input | Analog input 2 |

| AIN3 | 4 | 6 | Analog input | Analog input 3 |

| AVDD | 10 | 12 | Analog supply | Positive analog power supply. Connect a 100-nF (or larger) capacitor to AVSS. |

| AVSS | 3 | 5 | Analog supply | Negative analog power supply |

| DGND | 2 | 4 | Digital supply | Digital ground |

| DVDD | 11 | 13 | Digital supply | Positive digital power supply. Connect a 100-nF (or larger) capacitor to DGND. |

| GPIO0 | 16 | 2 | Digital input/output | General-purpose input/output 0 |

| GPIO1 | 15 | 1 | Digital input/output | General-purpose input/output 1 |

| GPIO2/DRDY | 12 | 14 | Digital input/output | General-purpose input/output 2 or data ready; active low. |

| REFN | 6 | 8 | Analog input | Negative reference input |

| REFP | 7 | 9 | Analog input | Positive reference input |

| RESET | 1 | 3 | Digital input | Reset; active low |

| RX | 14 | 16 | Digital input | Serial data input |

| TX | 13 | 15 | Digital output | Serial data output |

| Thermal pad | Pad | — | — | Thermal power pad. Connect to AVSS. |

6 Specifications

6.1 Absolute Maximum Ratings(1)

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Power-supply voltage | AVDD to AVSS | –0.3 | 7 | V |

| DVDD to DGND | –0.3 | 7 | ||

| AVSS to DGND | –2.8 | 0.3 | ||

| Analog input voltage | AIN0, AIN1, AIN2, AIN3, REFP, REFN | AVSS – 0.3 | AVDD + 0.3 | V |

| Digital input voltage | TX, RX, GPIO0, GPIO1, GPIO2/DRDY, RESET | DGND – 0.3 | DVDD + 0.3 | V |

| Input current | Continuous, any pin except power-supply pins | –10 | 10 | mA |

| Temperature | Junction, TJ | 150 | °C | |

| Storage, Tstg | –60 | 150 | ||

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±2000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±750 | |||

6.3 Recommended Operating Conditions

over operating ambient temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| POWER SUPPLY | ||||||

| Unipolar analog power supply | AVDD to AVSS | 2.3 | 5.5 | V | ||

| AVSS to DGND | –0.1 | 0 | 0.1 | |||

| Bipolar analog power supply | AVDD to DGND | 2.3 | 2.5 | 2.75 | V | |

| AVSS to DGND | –2.75 | –2.5 | –2.3 | |||

| Digital power supply | DVDD to DGND | 2.3 | 5.5 | V | ||

| ANALOG INPUTS(1) | ||||||

| V(AINx) | Absolute input voltage(2) | PGA disabled, gain = 1 to 4 | AVSS – 0.1 | AVDD + 0.1 | V | |

| PGA enabled, gain = 1 to 4 | AVSS + 0.2 | AVDD – 0.2 | ||||

| PGA enabled, gain = 8 to 128 | AVSS + 0.2 +

|VINMAX|·(Gain – 4) / 8 |

AVDD – 0.2 –

|VINMAX|·(Gain – 4) / 8 |

||||

| VIN | Differential input voltage | VIN = VAINP – VAINN(3) | –VREF / Gain | VREF / Gain | V | |

| VOLTAGE REFERENCE INPUTS | ||||||

| VREF | Differential reference input voltage | VREF = V(REFP) – V(REFN) | 0.75 | 2.5 | AVDD – AVSS | V |

| V(REFN) | Absolute negative reference voltage | AVSS – 0.1 | V(REFP) – 0.75 | V | ||

| V(REFP) | Absolute positive reference voltage | V(REFN) + 0.75 | AVDD + 0.1 | V | ||

| DIGITAL INPUTS | ||||||

| Input voltage | RX, GPIO0, GPIO1, GPIO2/DRDY, RESET | DGND | DVDD | V | ||

| TEMPERATURE RANGE | ||||||

| TA | Operating ambient temperature | –40 | 125 | °C | ||

PGA disabled means the low-noise PGA is powered down and bypassed. Gains of 1, 2, and 4 are still possible in this case.

See the Low-Noise Programmable Gain Stage section for more information.

6.4 Thermal Information

| THERMAL METRIC(1) | ADS122U04 | UNIT | ||

|---|---|---|---|---|

| WQFN (RTE) | TSSOP (PW) | |||

| 16 PINS | 16 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 57.7 | 90.3 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 29.0 | 31.7 | °C/W |

| RθJB | Junction-to-board thermal resistance | 19.9 | 41.8 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.3 | 1.8 | °C/W |

| ψJB | Junction-to-board characterization parameter | 19.8 | 41.2 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 11.8 | N/A | °C/W |

6.5 Electrical Characteristics

minimum and maximum specifications apply from TA = –40°C to +125°C; typical specifications are at TA = 25°C; all specifications are at AVDD = 2.3 V to 5.5 V, AVSS = 0 V, DVDD = 3.3 V, PGA enabled, all data rates, and internal reference enabled (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| ANALOG INPUTS | ||||||

| Absolute input current | PGA disabled, gain = 1 to 4, normal mode, VIN = 0 V | ±5 | nA | |||

| PGA disabled, gain = 1 to 4, turbo mode, VIN = 0 V | ±10 | |||||

| Gain = 1 to 128, VIN = 0 V | ±1 | |||||

| Absolute input current drift | PGA disabled, gain = 1 to 4, VIN = 0 V | 10 | pA/°C | |||

| Gain = 1 to 128, VIN = 0 V | 5 | |||||

| Differential input current | PGA disabled, gain = 1 to 4, normal mode,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

±5 | nA | |||

| PGA disabled, gain = 1 to 4, turbo mode,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

±10 | |||||

| Gain = 1 to 128,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

±1 | |||||

| Differential input current drift | PGA disabled, gain = 1 to 4,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

10 | pA/°C | |||

| Gain = 1 to 128,

VCM = AVDD / 2, –VREF / Gain ≤ VIN ≤ VREF / Gain |

2 | |||||

| SYSTEM PERFORMANCE | ||||||

| Resolution (no missing codes) | 24 | Bits | ||||

| DR | Data rate | Normal mode | 20, 45, 90, 175, 330, 600, 1000 | SPS | ||

| Turbo mode | 40, 90, 180, 350, 660, 1200, 2000 | |||||

| Noise (input-referred)(1) | Normal mode, gain = 128, DR = 20 SPS | 110 | nVRMS | |||

| INL | Integral nonlinearity | AVDD = 3.3 V, gain = 1 to 128, VCM = AVDD / 2, external VREF, normal mode, best fit | –15 | ±6 | 15 | ppmFSR |

| VIO | Input offset voltage | PGA disabled, gain = 1 to 4, differential inputs | ±4 | µV | ||

| Gain = 1, differential inputs, TA = 25°C | –150 | ±5 | 150 | |||

| Gain = 2 to 128, differential inputs | ±4 | |||||

| Offset drift | PGA disabled, gain = 1 to 4 | 0.02 | µV/°C | |||

| Gain = 1 to 128 | 0.1 | 0.6 | ||||

| Gain error(2) | PGA disabled, gain = 1 to 4 | ±0.01% | ||||

| Gain = 1 to 32, TA = 25°C | –0.05% | ±0.01% | 0.05% | |||

| Gain = 64 to 128, TA = 25°C | –0.1% | ±0.015% | 0.1% | |||

| Gain drift(2) | PGA disabled, gain = 1 to 4 | 0.5 | ppm/°C | |||

| Gain = 1 to 32 | 0.5 | 2 | ||||

| Gain = 64 to 128 | 1 | 4 | ||||

| SYSTEM PERFORMANCE (continued) | ||||||

| NMRR | Normal-mode rejection ratio | 50 Hz ±1 Hz, DR = 20 SPS | 78 | 88 | dB | |

| 60 Hz ±1 Hz, DR = 20 SPS | 80 | 88 | ||||

| CMRR | Common-mode rejection ratio | At dc, gain = 1, AVDD = 3.3 V | 90 | 105 | dB | |

| fCM = 50 Hz or 60 Hz, DR = 20 SPS, AVDD = 3.3 V | 105 | 115 | ||||

| fCM = 50 Hz or 60 Hz, DR = 2 kSPS, AVDD = 3.3 V | 95 | 110 | ||||

| PSRR | Power-supply rejection ratio | AVDD at dc, VCM = AVDD / 2 | 85 | 105 | dB | |

| DVDD at dc, VCM = AVDD / 2 | 95 | 115 | ||||

| INTERNAL VOLTAGE REFERENCE | ||||||

| VREF | Reference voltage | 2.048 | V | |||

| Accuracy | TA = 25°C, TSSOP package | –0.15% | ±0.01% | 0.15% | ||

| TA = 25°C, WQFN package | –0.25% | ±0.04% | 0.25% | |||

| Temperature drift | 5 | 30 | ppm/°C | |||

| Long-term drift | 1000 hours | 110 | ppm | |||

| VOLTAGE REFERENCE INPUTS | ||||||

| Reference input current | REFP = VREF, REFN = AVSS, AVDD = 3.3 V | ±10 | nA | |||

| INTERNAL OSCILLATOR | ||||||

| fCLK | Frequency | Normal mode | 1.024 | MHz | ||

| Turbo mode | 2.048 | |||||

| Accuracy | Normal mode | –2% | ±1% | 2% | ||

| Turbo mode | –4% | ±2% | 4% | |||

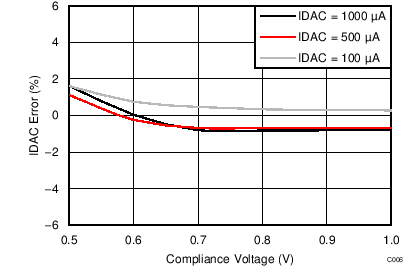

| EXCITATION CURRENT SOURCES (IDACs) (AVDD = 3.3 V to 5.5 V) | ||||||

| Current settings | 10, 50, 100, 250, 500, 1000, 1500 | µA | ||||

| Compliance voltage | All IDAC settings | AVDD – 0.9 | V | |||

| Accuracy (each IDAC) | IDAC = 50 µA to 1.5 mA | –6% | ±1% | 6% | ||

| Current matching between IDACs | IDAC = 50 µA to 1.5 mA, TA = 25°C | 0.3% | 2% | |||

| Temperature drift (each IDAC) | IDAC = 50 µA to 1.5 mA | 50 | ppm/°C | |||

| Temperature drift matching between IDACs | IDAC = 50 µA to 1.5 mA | 8 | 40 | ppm/°C | ||

| BURN-OUT CURRENT SOURCES (BOCS) | ||||||

| Magnitude | Sink and source | 10 | µA | |||

| Accuracy | ±5% | |||||

| TEMPERATURE SENSOR | ||||||

| Conversion resolution | 14 | Bits | ||||

| Temperature resolution | 0.03125 | °C | ||||

| Accuracy | TA = 0°C to +85°C | –1 | ±0.25 | 1 | °C | |

| TA = –40°C to +125°C | –1.5 | ±0.5 | 1.5 | |||

| Accuracy vs analog supply voltage | 0.0625 | 0.25 | °C/V | |||

| DIGITAL INPUTS/OUTPUTS | ||||||

| VIL | Logic input level, low | DGND | 0.3 DVDD | V | ||

| VIH | Logic input level, high | 0.7 DVDD | DVDD | V | ||

| VOL | Logic output level, low | IOL = 1 mA | 0.2 DVDD | V | ||

| VOH | Logic output level, high | IOH = 1 mA | 0.8 DVDD | V | ||

| Input current | DGND ≤ VDigital Input ≤ DVDD | –1 | 1 | µA | ||

| ANALOG SUPPLY CURRENT (AVDD = 3.3 V, VIN = 0 V, IDACs Turned Off) | ||||||

| IAVDD | Analog supply current | Power-down mode | 0.1 | 3 | µA | |

| Normal mode, PGA disabled, gain = 1 to 4 | 250 | |||||

| Normal mode, gain = 1 to 16 | 360 | 510 | ||||

| Normal mode, gain = 32 | 455 | |||||

| Normal mode, gain = 64, 128 | 550 | |||||

| Turbo mode, PGA disabled, gain = 1 to 4 | 370 | |||||

| Turbo mode, gain = 1 to 16 | 580 | |||||

| Turbo mode, gain = 32 | 765 | |||||

| Turbo mode, gain = 64, 128 | 955 | |||||

| ADDITIONAL ANALOG SUPPLY CURRENTS PER FUNCTION (AVDD = 3.3 V) | ||||||

| IAVDD | Analog supply current | External reference selected | 60 | µA | ||

| IDAC overhead (excludes the actual IDAC current) | 195 | |||||

| DIGITAL SUPPLY CURRENT (DVDD = 3.3 V, All Data Rates, UART Not Active) | ||||||

| IDVDD | Digital supply current | Power-down mode | 0.3 | 5 | µA | |

| Normal mode | 65 | 100 | ||||

| Turbo mode | 100 | |||||

| POWER DISSIPATION (AVDD = DVDD = 3.3 V, All Data Rates, VIN = 0 V, UART Not Active) | ||||||

| PD | Power dissipation | Normal mode, gain = 1 to 16 | 1.4 | mW | ||

| Turbo mode, gain = 1 to 16 | 2.2 | |||||

6.6 UART Timing Requirements

over operating ambient temperature range and DVDD = 2.3 V to 5.5 V (unless otherwise noted)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| 1/tBAUD | Bus baud rate | 2 | 120 | kBaud | ||

| tr(RX) | Rise time | 10-pF load | 15 | % of tBAUD | ||

| tf(RX) | Fall time | 10-pF load | 15 | % of tBAUD | ||

| tJITTER | Edge timing variance | –1% | 1% | |||

| tw(RSL) | Pulse duration, RESET low | 250 | ns | |||

| td(RSRX) | Delay time, start of communication after RESET rising edge

(or RESET command decoded(2)) |

80 | µs | |||

| Timeout(1) | Normal mode | 32760 | tMOD | |||

| Turbo mode | 65520 | |||||

tMOD = 1 / fMOD. Modulator frequency fMOD = 256 kHz (normal mode) and 512 kHz (turbo mode).

6.7 UART Switching Characteristics

over operating ambient temperature range and DVDD = 2.3 V to 5.5 V (unless otherwise noted)| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT(1) | |

|---|---|---|---|---|---|---|

| tp(RDDR) | Propagation delay time, RDATA command decoded to DRDY rising edge(2) | Manual data read mode | 7 | tCLK | ||

| tp(RDTX) | Propagation delay time, RDATA command decoded to TX falling edge(2) | Manual data read mode | 2 | tBAUD | ||

| tp(DRTX) | Propagation delay time, DRDY rising edge to TX falling edge(2) | Automatic data read mode | 2 | tBAUD | ||

| tw(DRH) | Pulse duration, DRDY high | 2 | tMOD | |||

| tw(DRL) | Pulse duration, DRDY low | Automatic data read mode | 4 | tCLK | ||

| tp(RREG) | Propagation delay time, RREG command decoded to TX falling edge(2) | 2 | tBAUD | |||

tMOD = 1 / fMOD. Modulator frequency fMOD = 256 kHz (normal mode) and 512 kHz (turbo mode).

Figure 1. UART Timing Requirements

Figure 1. UART Timing Requirements  Figure 2. RESET Pin and RESET Command Timing Requirements

Figure 2. RESET Pin and RESET Command Timing Requirements  Figure 3. Manual Data Read Mode DRDY Switching Characteristics

Figure 3. Manual Data Read Mode DRDY Switching Characteristics  Figure 4. Automatic Data Read Mode DRDY Switching Characteristics

Figure 4. Automatic Data Read Mode DRDY Switching Characteristics  Figure 5. Register Read Switching Characteristics

Figure 5. Register Read Switching Characteristics 6.8 Typical Characteristics

at TA = 25°C, AVDD = 3.3 V, and AVSS = 0 V using internal VREF = 2.048 V (unless otherwise noted)

| Normal mode, PGA disabled, VIN = 0 V |

| Turbo mode, PGA disabled, VIN = 0 V |

| Normal mode, PGA disabled, VCM = 1.65 V |

Differential Input Voltage

| Turbo mode, PGA disabled, VCM = 1.65 V |

Differential Input Voltage

| PGA enabled, external reference, best fit |

| PGA enabled, gain = 1, 620 samples |

| PGA enabled | ||

| PGA enabled, gain = 1, 620 samples |

| PGA disabled |

| PGA disabled |

| Normal mode |

| Normal mode |

| DVDD = 3.3 V |

| Normal mode |

| Power-down mode |

| Normal mode |

| Normal mode, PGA enabled, VIN = 0 V |

| Turbo mode, PGA enabled, VIN = 0 V |

| Normal mode, PGA enabled, VCM = 1.65 V |

Differential Input Voltage

| Turbo mode, PGA enabled, VCM = 1.65 V |

Differential Input Voltage

| PGA enabled, internal reference, best fit |

| PGA disabled |

| PGA disabled, gain = 1, 620 samples |

| PGA enabled, gain = 128, 620 samples |

| PGA enabled |

| PGA enabled |

| Normal mode | ||

| DVDD = 3.3 V |

| Power-down mode |

| Normal mode |

7 Parameter Measurement Information

7.1 Noise Performance

Delta-sigma (ΔΣ) analog-to-digital converters (ADCs) are based on the principle of oversampling. The input signal of a ΔΣ ADC is sampled at a high frequency (modulator frequency) and subsequently filtered and decimated in the digital domain to yield a conversion result at the respective output data rate. The ratio between modulator frequency and output data rate is called oversampling ratio (OSR). By increasing the OSR, and thus reducing the output data rate, the noise performance of the ADC can be optimized. In other words, the input-referred noise drops when reducing the output data rate because more samples of the internal modulator are averaged to yield one conversion result. Increasing the gain also reduces the input-referred noise, which is particularly useful when measuring low-level signals.

Table 1 to Table 8 summarize the device noise performance. Data are representative of typical noise performance at TA = 25°C using the internal 2.048-V reference. Data shown are the result of averaging readings from a single device over a time period of approximately 0.75 seconds and are measured with the inputs internally shorted together. Table 1, Table 3, Table 5, and Table 7 list the input-referred noise in units of μVRMS for the conditions shown. Values in µVPP are shown in parenthesis. Table 2, Table 4, Table 6, and Table 8 list the corresponding data in effective resolution calculated from μVRMS values using Equation 1. Noise-free resolution calculated from peak-to-peak noise values using Equation 2 are shown in parenthesis.

The input-referred noise (Table 1, Table 3, Table 5, and Table 7) only changes marginally when using an external low-noise reference, such as the REF5020. Use Equation 1 and Equation 2 to calculate effective resolution numbers and noise-free resolution when using a reference voltage other than 2.048 V:

Table 1. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, PGA Enabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Enabled) | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | |

| 20 | 5.10 (21.69) | 2.49 (10.71) | 1.25 (5.74) | 0.64 (2.92) | 0.41 (1.52) | 0.24 (0.98) | 0.14 (0.54) | 0.11 (0.46) |

| 45 | 6.53 (29.99) | 3.02 (14.47) | 1.67 (6.80) | 0.93 (4.00) | 0.52 (2.43) | 0.28 (1.39) | 0.17 (0.71) | 0.13 (0.57) |

| 90 | 9.01 (41.61) | 4.67 (24.36) | 2.41 (10.95) | 1.24 (6.54) | 0.73 (3.46) | 0.41 (2.06) | 0.25 (1.20) | 0.19 (0.91) |

| 175 | 12.78 (63.79) | 6.75 (37.30) | 3.26 (17.00) | 1.92 (9.81) | 1.02 (5.27) | 0.60 (3.32) | 0.35 (1.93) | 0.25 (1.49) |

| 330 | 17.75 (107.88) | 8.75 (48.95) | 4.72 (28.25) | 2.62 (14.47) | 1.42 (8.06) | 0.85 (4.64) | 0.50 (2.93) | 0.37 (1.91) |

| 600 | 24.73 (153.77) | 12.89 (76.01) | 6.81 (38.94) | 3.84 (22.30) | 2.02 (12.07) | 1.18 (6.69) | 0.70 (4.49) | 0.51 (3.14) |

| 1000 | 36.90 (228.90) | 18.07 (108.90) | 9.48 (58.24) | 5.49 (31.55) | 2.86 (17.41) | 1.65 (10.23) | 1.04 (6.21) | 0.73 (4.69) |

Table 2. Effective Resolution From RMS Noise (Noise-Free Resolution From Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, PGA Enabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Enabled) | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | |

| 20 | 19.62 (17.53) | 19.65 (17.54) | 19.64 (17.44) | 19.61 (17.22) | 19.25 (17.36) | 19.02 (16.99) | 18.80 (16.85) | 18.15 (16.09) |

| 45 | 19.26 (17.06) | 19.37 (17.11) | 19.23 (17.20) | 19.07 (16.94) | 18.91 (16.68) | 18.80 (16.49) | 18.52 (16.46) | 17.91 (15.78) |

| 90 | 18.79 (16.59) | 18.74 (16.36) | 18.70 (16.51) | 18.66 (16.23) | 18.42 (16.18) | 18.25 (15.92) | 17.97 (15.70) | 17.36 (15.10) |

| 175 | 18.29 (15.97) | 18.21 (15.74) | 18.26 (15.88) | 18.02 (15.48) | 17.94 (15.57) | 17.70 (15.23) | 17.48 (15.02) | 16.97 (14.39) |

| 330 | 17.82 (15.21) | 17.84 (15.35) | 17.73 (15.12) | 17.58 (15.15) | 17.46 (14.96) | 17.20 (14.75) | 16.97 (14.41) | 16.40 (14.03) |

| 600 | 17.34 (14.70) | 17.28 (14.72) | 17.20 (14.68) | 17.02 (14.70) | 16.95 (14.37) | 16.73 (14.22) | 16.46 (13.80) | 15.94 (13.32) |

| 1000 | 16.76 (14.13) | 16.79 (14.20) | 16.72 (14.10) | 16.51 (13.99) | 16.45 (13.99) | 16.24 (13.61) | 15.91 (13.33) | 15.42 (12.74) |

Table 3. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, PGA Disabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Disabled) | ||

|---|---|---|---|

| 1 | 2 | 4 | |

| 20 | 5.04 (19.71) | 2.53 (10.06) | 1.57 (5.68) |

| 45 | 6.57 (33.34) | 3.43 (14.00) | 1.60 (6.98) |

| 90 | 8.75 (42.59) | 4.35 (22.83) | 2.13 (10.52) |

| 175 | 12.64 (65.71) | 6.27 (35.00) | 3.40 (16.83) |

| 330 | 18.58 (106.06) | 9.33 (52.59) | 4.54 (26.30) |

| 600 | 25.74 (150.81) | 12.57 (79.15) | 6.47 (36.87) |

| 1000 | 36.98 (221.61) | 18.67 (111.61) | 9.27 (55.07) |

Table 4. Effective Resolution From RMS Noise (Noise-Free Resolution From Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Normal Mode, PGA Disabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Disabled) | ||

|---|---|---|---|

| 1 | 2 | 4 | |

| 20 | 19.63 (17.66) | 19.63 (17.64) | 19.32 (17.46) |

| 45 | 19.25 (16.91) | 19.19 (17.16) | 19.29 (17.16) |

| 90 | 18.84 (16.55) | 18.84 (16.45) | 18.87 (16.57) |

| 175 | 18.31 (15.93) | 18.32 (15.84) | 18.20 (15.89) |

| 330 | 17.75 (15.24) | 17.74 (15.25) | 17.78 (15.25) |

| 600 | 17.28 (14.73) | 17.31 (14.66) | 17.27 (14.76) |

| 1000 | 16.76 (14.17) | 16.74 (14.16) | 16.75 (14.18) |

Table 5. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, PGA Enabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Enabled) | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | |

| 40 | 4.41 (19.43) | 2.25 (10.62) | 1.12 (5.32) | 0.63 (2.74) | 0.36 (1.64) | 0.22 (1.10) | 0.13 (0.63) | 0.10 (0.51) |

| 90 | 5.76 (30.73) | 2.98 (14.16) | 1.62 (7.84) | 0.92 (4.43) | 0.52 (2.59) | 0.31 (1.59) | 0.18 (0.97) | 0.15 (0.76) |

| 180 | 8.49 (44.61) | 4.48 (22.25) | 2.29 (13.23) | 1.34 (6.83) | 0.71 (4.11) | 0.43 (2.49) | 0.28 (1.51) | 0.22 (1.05) |

| 350 | 12.77 (71.04) | 6.33 (37.00) | 3.33 (19.17) | 1.89 (10.76) | 1.04 (5.91) | 0.61 (3.54) | 0.41 (2.13) | 0.29 (1.64) |

| 660 | 17.10 (105.64) | 9.04 (54.97) | 4.51 (27.74) | 2.84 (16.98) | 1.42 (8.45) | 0.86 (5.07) | 0.57 (3.32) | 0.41 (2.38) |

| 1200 | 25.26 (153.74) | 12.51 (78.75) | 6.58 (39.68) | 3.90 (23.84) | 2.11 (13.19) | 1.23 (7.46) | 0.81 (5.17) | 0.58 (3.50) |

| 2000 | 35.35 (226.39) | 17.82 (112.98) | 9.40 (59.37) | 5.37 (32.97) | 3.02 (18.73) | 1.76 (11.12) | 1.12 (7.06) | 0.83 (5.41) |

Table 6. Effective Resolution From RMS Noise (Noise-Free Resolution From Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, PGA Enabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Enabled) | |||||||

|---|---|---|---|---|---|---|---|---|

| 1 | 2 | 4 | 8 | 16 | 32 | 64 | 128 | |

| 40 | 19.83 (17.69) | 19.80 (17.56) | 19.80 (17.55) | 19.63 (17.51) | 19.44 (17.25) | 19.15 (16.83) | 18.91 (16.63) | 18.29 (15.94) |

| 90 | 19.44 (17.02) | 19.39 (17.14) | 19.27 (16.99) | 19.09 (16.82) | 18.91 (16.59) | 18.66 (16.30) | 18.44 (16.01) | 17.70 (15.36) |

| 180 | 18.88 (16.49) | 18.80 (16.49) | 18.77 (16.24) | 18.54 (16.19) | 18.46 (15.93) | 18.18 (15.65) | 17.80 (15.37) | 17.15 (14.90) |

| 350 | 18.29 (15.82) | 18.30 (15.76) | 18.23 (15.71) | 18.05 (15.55) | 17.91 (15.40) | 17.68 (15.14) | 17.25 (14.87) | 16.75 (14.25) |

| 660 | 17.87 (15.24) | 17.79 (15.19) | 17.79 (15.17) | 17.46 (14.88) | 17.46 (14.89) | 17.18 (14.62) | 16.78 (14.23) | 16.25 (13.71) |

| 1200 | 17.31 (14.70) | 17.32 (14.67) | 17.25 (14.66) | 17.00 (14.39) | 16.89 (14.24) | 16.67 (14.07) | 16.27 (13.60) | 15.75 (13.16) |

| 2000 | 16.82 (14.14) | 16.81 (14.15) | 16.73 (14.07) | 16.54 (13.92) | 16.37 (13.74) | 16.15 (13.49) | 15.80 (13.15) | 15.23 (12.53) |

Table 7. Noise in μVRMS (μVPP)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, PGA Disabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Disabled) | ||

|---|---|---|---|

| 1 | 2 | 4 | |

| 40 | 4.30 (18.73) | 2.18 (9.84) | 1.10 (5.38) |

| 90 | 6.19 (32.78) | 3.14 (13.53) | 1.42 (7.19) |

| 180 | 9.08 (47.57) | 4.49 (25.48) | 2.18 (10.96) |

| 350 | 12.40 (72.79) | 5.89 (33.34) | 3.07 (18.31) |

| 660 | 17.59 (103.97) | 9.05 (51.15) | 4.39 (24.69) |

| 1200 | 24.67 (149.07) | 12.56 (76.35) | 6.31 (37.48) |

| 2000 | 34.54 (224.19) | 17.76 (113.98) | 8.85 (56.87) |

Table 8. Effective Resolution From RMS Noise (Noise-Free Resolution From Peak-to-Peak Noise)

at AVDD = 3.3 V, AVSS = 0 V, Turbo Mode, PGA Disabled, and Internal VREF = 2.048 V

| DATA RATE

(SPS) |

GAIN (PGA Disabled) | ||

|---|---|---|---|

| 1 | 2 | 4 | |

| 40 | 19.86 (17.74) | 19.84 (17.67) | 19.83 (17.54) |

| 90 | 19.34 (16.93) | 19.32 (17.21) | 19.46 (17.12) |

| 180 | 18.78 (16.39) | 18.80 (16.29) | 18.84 (16.51) |

| 350 | 18.33 (15.78) | 18.41 (15.91) | 18.34 (15.77) |

| 660 | 17.83 (15.27) | 17.79 (15.29) | 17.83 (15.34) |

| 1200 | 17.34 (14.75) | 17.32 (14.71) | 17.31 (14.74) |

| 2000 | 16.86 (14.16) | 16.82 (14.13) | 16.82 (14.14) |

8 Detailed Description

8.1 Overview

The ADS122U04 is a small, low-power, 24-bit, ΔΣ ADC that offers many integrated features to reduce system cost and component count in applications measuring small sensor signals.

In addition to the ΔΣ ADC core and single-cycle settling digital filter, the device offers a low-noise, high input impedance, programmable gain amplifier (PGA), an internal 2.048-V voltage reference, and a clock oscillator. The device also integrates a highly linear and accurate temperature sensor as well as two matched programmable current sources (IDACs) for sensor excitation. All of these features are intended to reduce the required external circuitry in typical sensor applications and improve overall system performance. The device is fully configured through five registers and controlled by six commands through a universal asynchronous receiver/transmitter (UART)-compatible interface. The Functional Block Diagram section shows the device functional block diagram.

The ADS122U04 ADC measures a differential signal, VIN, which is the difference in voltage between nodes AINP and AINN. The converter core consists of a differential, switched-capacitor, ΔΣ modulator followed by a digital filter. The digital filter receives a high-speed bitstream from the modulator and outputs a code proportional to the input voltage. This architecture results in a very strong attenuation of any common-mode signal.

The device has two available conversion modes: single-shot conversion and continuous conversion mode. In single-shot conversion mode, the ADC performs one conversion of the input signal upon request and stores the value in an internal data buffer. The device then enters a low-power state to save power. Single-shot conversion mode is intended to provide significant power savings in systems that require only periodic conversions, or when there are long idle periods between conversions. In continuous conversion mode, the ADC automatically begins a conversion of the input signal as soon as the previous conversion is completed. New data are available at the programmed data rate. Data can be read at any time without concern of data corruption and always reflect the most recently completed conversion.

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 Multiplexer

Figure 45 shows the flexible input multiplexer of the device. Either four single-ended signals, two differential signals, or a combination of two single-ended signals and one differential signal can be measured. The multiplexer is configured by four bits (MUX[3:0]) in the configuration register. When single-ended signals are measured, the negative ADC input (AINN) is internally connected to AVSS by a switch within the multiplexer. For system-monitoring purposes, the analog supply [(AVDD – AVSS) / 4] or the currently selected external reference voltage [(VREFP – VREFN) / 4] can be selected as inputs to the ADC. The multiplexer also offers the possibility to route any of the two programmable current sources to any analog input (AINx) or to the dedicated reference pins (REFP, REFN).

Figure 45. Analog Input Multiplexer

Figure 45. Analog Input Multiplexer Electrostatic discharge (ESD) diodes to AVDD and AVSS protect the inputs. The absolute voltage on any input must stay within the range provided by Equation 3 to prevent the ESD diodes from turning on:

If the voltages on the input pins have any potential to violate these conditions, external Schottky clamp diodes or series resistors may be required to limit the input current to safe values (see the Absolute Maximum Ratings table). Overdriving an unused input on the device can affect conversions taking place on other input pins.