ZHCSX83 October 2024 ADS127L21B

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 引脚配置和功能

- 5 规格

- 6 参数测量信息

-

7 详细说明

- 7.1 概述

- 7.2 功能方框图

- 7.3 特性说明

- 7.4 器件功能模式

- 7.5 编程

- 8 寄存器映射

- 9 应用和实施

- 10器件和文档支持

- 11修订历史记录

- 12机械、封装和可订购信息

9.2.3.3 应用曲线

以下图表由 TINA-TI™ 基于 SPICE 的模拟仿真程序生成。在 THS4551 米6体育平台手机版_好二三四文件夹中下载 THS4551 SPICE 模型。

图 9-9 展示了抗混叠滤波器的频率响应以及抗混叠滤波器和 ADC 的总 响应。如该图所示,滤波器提供从奈奎斯特频率到 12.8MHz fMOD 频率的 90dB 阻带衰减。

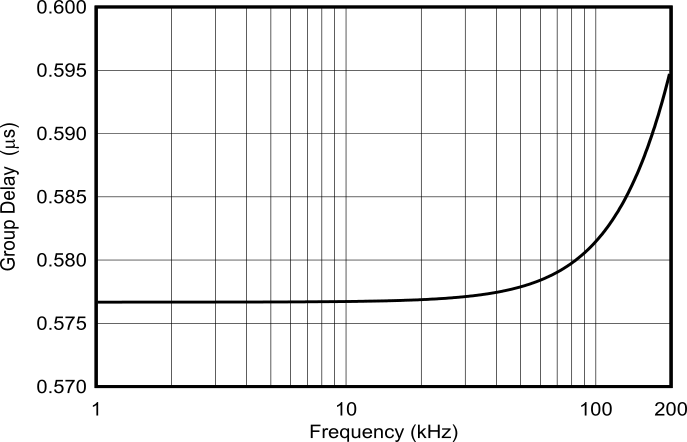

图 9-10 展示了模拟滤波器群延迟。与 ADC 数字滤波器的 85μs 群延迟 (34 / fDATA) 相比,0.575μs 的群延迟很小。模拟滤波器群延迟线性度为 0.017μs,在 165kHz 通带的边缘达到峰值。

图 9-9 抗混叠滤波器频率响应

图 9-9 抗混叠滤波器频率响应 图 9-10 抗混叠滤波器群延迟

图 9-10 抗混叠滤波器群延迟图 9-11 展示了抗混叠滤波器电路的噪声密度、ADC 的噪声密度以及滤波器和 ADC 的组合噪声密度。噪声密度是每 √Hz 带宽绘制的噪声电压与频率间关系图。

图 9-12 展示了从 1Hz 启动频率到 ADC 最终带宽的总噪声。低于 200Hz 时,噪声主要由 THS4551 放大器的 1/f 电压和电流噪声决定。在 200Hz 以上,噪声主要是 ADC 噪声。滤波器和 ADC 在 165kHz 带宽上的组合噪声为 11.8μV,满足 12μV 的目标值。

通过代入 THP210 输入驱动器来代替 THS4551,可以提高低频噪声性能。有关详细信息,请参阅 THP210 和 ADS127L11 性能 应用手册。

图 9-11 噪声密度

图 9-11 噪声密度 图 9-12 总噪声

图 9-12 总噪声