-

ADS131E0x 4 通道、6 通道 和 8 通道、24 位同步采样 Δ-Σ ADC

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Device Comparison

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5

Programming

- 9.5.1 Data Format

- 9.5.2 SPI Interface

- 9.5.3

SPI Command Definitions

- 9.5.3.1 Sending Multibyte Commands

- 9.5.3.2 WAKEUP: Exit STANDBY Mode

- 9.5.3.3 STANDBY: Enter STANDBY Mode

- 9.5.3.4 RESET: Reset Registers to Default Values

- 9.5.3.5 START: Start Conversions

- 9.5.3.6 STOP: Stop Conversions

- 9.5.3.7 OFFSETCAL: Channel Offset Calibration

- 9.5.3.8 RDATAC: Start Read Data Continuous Mode

- 9.5.3.9 SDATAC: Stop Read Data Continuous Mode

- 9.5.3.10 RDATA: Read Data

- 9.5.3.11 RREG: Read from Register

- 9.5.3.12 WREG: Write to Register

- 9.6

Register Map

- 9.6.1

Register Descriptions

- 9.6.1.1 ID: ID Control Register (Factory-Programmed, Read-Only) (address = 00h) [reset = xxh]

- 9.6.1.2 CONFIG1: Configuration Register 1 (address = 01h) [reset = 91h]

- 9.6.1.3 CONFIG2: Configuration Register 2 (address = 02h) [reset = E0h]

- 9.6.1.4 CONFIG3: Configuration Register 3 (address = 03h) [reset = 40]

- 9.6.1.5 FAULT: Fault Detect Control Register (address = 04h) [reset = 00h]

- 9.6.1.6 CHnSET: Individual Channel Settings (address = 05h to 0Ch) [reset = 10h]

- 9.6.1.7 FAULT_STATP: Fault Detect Positive Input Status (address = 12h) [reset = 00h]

- 9.6.1.8 FAULT_STATN: Fault Detect Negative Input Status (address = 13h) [reset = 00h]

- 9.6.1.9 GPIO: General-Purpose IO Register (address = 14h) [reset = 0Fh]

- 9.6.1

Register Descriptions

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13器件和文档支持

- 14机械、封装和可订购信息

- 重要声明

ADS131E0x 4 通道、6 通道 和 8 通道、24 位同步采样 Δ-Σ ADC

1 特性

2 应用

- 电源保护:断路器和继电器保护

- 电能计量:单相、多相和电能质量

- 电池测试系统

- 测试和测量

- 同步采样数据采集系统

3 说明

ADS131E0x 是一系列多通道同步采样、24 位 Δ-Σ 模数转换器 (ADC),内置可编程增益放大器(PGA)、内部基准和板载振荡器。凭借 ADC 的宽动态范围、可扩展数据传输速率以及内部故障检测监测计,ADS131E0x 受到工业电源监测和保护 以及测试和测量应用的青睐。真正的高阻抗输入支持 ADS131E0x 直接与电阻分压器网络或电压互感器相连以测量线路电压或与电流互感器或罗戈夫斯基线圈相连来测量电流。借助于高集成度和出色的性能,ADS131E0x 系列米6体育平台手机版_好二三四可在大大降低尺寸、功耗和总体成本的前提下创建可升级的工业用电源系统。

ADS131E0x 在每通道上有一个灵活输入多路复用器,此多路复用器被独立连接至内部生成信号以实现测试、温度、和故障检测。故障检测可在器件内部执行,此器件使用集成的带有受数模转换器 (DAC) 控制的触发电平的比较器。ADS131E0x 运行的数据速率可高达 64kSPS。

这些完整的模拟前端 (AFE) 解决方案封装在 TQFP-64 封装内并且额定工业用温度范围为 -40°C 至 +105°C。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| ADS131E0x | TQFP (64) | 10.00mm x 10.00mm |

- 要了解所有可用封装,请参见数据表末尾的可订购米6体育平台手机版_好二三四附录。

ADS131E08 简化电路原理图

4 修订历史记录

Changes from B Revision (December 2013) to C Revision

- Added ESD 额定值表,特性 描述 部分,器件功能模式,应用和实施部分,电源相关建议部分,布局部分,器件和文档支持部分以及机械、封装和可订购信息部分Go

- Changed formatting of Thermal Information table note Go

Changes from A Revision (April 2013) to B Revision

- Deleted 器件图Go

- Changed 通篇文档中的 ADS131E0x 系列器件 说明 至仅为 24 位Go

- Added AVSS to DGND row to Absolute Maximum Ratings tableGo

- Changed minimum specification to External Reference, VREFP parameter in Electrical Characteristics tableGo

- Changed conditions in Figure 10Go

- Changed conditions in Figure 11Go

- Changed START Opcode to START in Figure 39Go

- Changed Reset (RESET) section for clarityGo

- Changed Power-Up Sequencing sectionGo

Changes from * Revision (June 2012) to A Revision

- Deleted AGND to DGND row from Absolute Maximum Ratings tableGo

- Changed value of Digital input to DVDD row in Absolute Maximum Ratings tableGo

- Added minimum and maximum specifications to External Reference, Reference input voltage parameter in Electrical Characteristics tableGo

- Added minimum and maximum specifications to External Reference, VREFP parameter in Electrical Characteristics tableGo

- Changed Channel Performance (AC Performance), Accuracy parameter in Electrical Characteristics tableGo

- Changed Internal Reference, VO parameter in Electrical Characteristics tableGo

- Changed Internal Reference, Temperature drift parameter in Electrical Characteristics tableGo

- Added Figure 15 Go

5 Device Comparison

| PRODUCT | NO. OF INPUTS | REFERENCE OPTIONS | RESOLUTION (Bits) | POWER-UP TIME (ms) |

|---|---|---|---|---|

| ADS130E08 | 8 | Internal, external | 16 | 128 |

| ADS131E04 | 4 | Internal, external | 24 | 128 |

| ADS131E06 | 6 | Internal, external | 24 | 128 |

| ADS131E08 | 8 | Internal, external | 24 | 128 |

| ADS131E08S | 8 | Internal only | 24 | 3 |

6 Pin Configuration and Functions

Pin Functions

| PIN | I/O | DESCRIPTION | |

|---|---|---|---|

| NAME | NO. | ||

| AVDD | 19, 21, 22, 56, 59 | Supply | Analog supply. Connect a 1-µF (or larger) capacitor to AVSS for each AVDD pin. |

| AVDD1 | 54 | Supply | Charge pump analog supply. Connect a 1-µF (or larger) capacitor to AVSS1. |

| AVSS | 20, 23, 32, 57, 58 | Supply | Analog ground |

| AVSS1 | 53 | Supply | Charge pump analog ground |

| CS | 39 | Digital input | Chip select; active low |

| CLK | 37 | Digital input | Master clock input. Connect to DGND if unused. |

| CLKSEL | 52 | Digital input | Master clock select |

| DAISY_IN | 41 | Digital input | Daisy-chain input. Connect to DGND if unused. |

| DGND | 33, 49, 51 | Supply | Digital ground |

| DIN | 34 | Digital input | Serial data input |

| DOUT | 43 | Digital output | Serial data output |

| DRDY | 47 | Digital output | Data ready; active low. Connect to DGND with a 10-kΩ resistor if unused. |

| DVDD | 48, 50 | Supply | Digital core power supply. Connect a 1-µF (or larger) capacitor to DGND for each DVDD pin. |

| GPIO1 | 42 | Digital input/output | General-purpose input/output pin 1. Connect to DGND with a 10-kΩ resistor if unused. |

| GPIO2 | 44 | Digital input/output | General-purpose input/output pin 2. Connect to DGND with a 10-kΩ resistor if unused. |

| GPIO3 | 45 | Digital input/output | General-purpose input/output pin 3. Connect to DGND with a 10-kΩ resistor if unused. |

| GPIO4 | 46 | Digital input/output | General-purpose input/output pin 4. Connect to DGND with a 10-kΩ resistor if unused. |

| IN1N(1) | 15 | Analog input | Negative analog input 1 |

| IN1P(1) | 16 | Analog input | Positive analog input 1 |

| IN2N(1) | 13 | Analog input | Negative analog input 2 |

| IN2P(1) | 14 | Analog input | Positive analog input 2 |

| IN3N(1) | 11 | Analog input | Negative analog input 3 |

| IN3P(1) | 12 | Analog input | Positive analog input 3 |

| IN4N(1) | 9 | Analog input | Negative analog input 4 |

| IN4P(1) | 10 | Analog input | Positive analog input 4 |

| IN5N(1) | 7 | Analog input | Negative analog input 5 (ADS131E06 and ADS131E08 only) |

| IN5P(1) | 8 | Analog input | Positive analog input 5 (ADS131E06 and ADS131E08 only) |

| IN6N(1) | 5 | Analog input | Negative analog input 6 (ADS131E06 and ADS131E08 only) |

| IN6P(1) | 6 | Analog input | Positive analog input 6 (ADS131E06 and ADS131E08 only) |

| IN7N(1) | 3 | Analog input | Negative analog input 7 (ADS131E08 only) |

| IN7P(1) | 4 | Analog input | Positive analog input 7 (ADS131E08 only) |

| IN8N(1) | 1 | Analog input | Negative analog input 8 (ADS131E08 only) |

| IN8P(1) | 2 | Analog input | Positive analog input 8 (ADS131E08 only) |

| NC | 27, 29, 62, 64 | — | No connection, leave floating. Can be connected to AVDD or AVSS with a 10-kΩ or higher resistor. |

| OPAMPN | 61 | Analog input | Op amp inverting input; leave floating if unused and power-down the op amp. |

| OPAMPP | 60 | Analog input | Op amp noninverting input; leave floating if unused and power-down the op amp. |

| OPAMPOUT | 63 | Analog output | Op amp output; leave floating if unused and power-down the op amp. |

| PWDN | 35 | Digital input | Power-down; active low |

| RESET | 36 | Digital input | System reset; active low |

| RESV1 | 31 | Digital input | Reserved for future use. Connect directly to DGND. |

| SCLK | 40 | Digital input | Serial clock input |

| START | 38 | Digital input | Start conversion |

| TESTN | 18 | Analog input/output | Test signal, negative pin. See the Unused Inputs and Outputs section for unused pins. |

| TESTP | 17 | Analog input/output | Test signal, positive pin. See the Unused Inputs and Outputs section for unused pins. |

| VCAP1 | 28 | Analog output | Analog bypass capacitor. Connect a 22-µF capacitor to AVSS. |

| VCAP2 | 30 | Analog output | Analog bypass capacitor. Connect a 1-µF capacitor to AVSS. |

| VCAP3 | 55 | Analog output | Analog bypass capacitor. Connect a parallel combination of 1-µF and 0.1-µF capacitors to AVSS. |

| VCAP4 | 26 | Analog output | Analog bypass capacitor. Connect a 1-µF capacitor to AVSS. |

| VREFN | 25 | Analog input | Negative reference voltage. Connect to AVSS |

| VREFP | 24 | Analog input/output | Positive reference voltage. Connect a minimum 10-µF capacitor to VREFN. |

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±1000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±500 | |||

7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| POWER SUPPLY | ||||||

| AVDD | Analog power supply | AVDD to AVSS | 2.7 | 5.0 | 5.25 | V |

| DVDD | Digital power supply | DVDD to DGND | 1.7 | 1.8 | 3.6 | V |

| Analog to digital supply | AVDD to DVDD | –2.1 | 3.6 | V | ||

| ANALOG INPUTS | ||||||

| VIN | Differential input voltage | VIN = V(INxP) – V(INxN) | –VREF / Gain | VREF / Gain | V | |

| VCM | Common-mode input voltage | VCM = (V(INxP) – V(INxN)) / 2 | See the Input Common-Mode Range section | V | ||

| VOLTAGE REFERENCE INPUTS | ||||||

| VREF | Reference input voltage | AVDD = 3 V, VREF = (VVREFP – VVREFN) | 2 | 2.5 | AVDD | V |

| AVDD = 5 V, VREF = (VVREFP – VVREFN) | 2 | 4 | AVDD | V | ||

| VREFN | Negative reference input | AVSS | V | |||

| VREFP | Positive input | AVDD – 3 | AVSS + 2.5 | AVDD | V | |

| EXTERNAL CLOCK SOURCE | ||||||

| fCLK | Master clock rate | CLKSEL pin = 0, (AVDD – AVSS) = 3 V |

1.7 | 2.048 | 2.25 | MHz |

| CLKSEL pin = 0, (AVDD – AVSS) = 5 V |

1.0 | 2.048 | 2.25 | |||

| DIGITAL INPUTS | ||||||

| Input voltage | DGND – 0.1 | DVDD + 0.1 | V | |||

| TEMPERATURE RANGE | ||||||

| TA | Operating ambient temperature | –40 | 105 | °C | ||

7.4 Thermal Information

| THERMAL METRIC(1) | ADS131E0x | UNIT | |

|---|---|---|---|

| PAG (TQFP) | |||

| 64 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 35 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 31 | °C/W |

| RθJB | Junction-to-board thermal resistance | 26 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.1 | °C/W |

| ψJB | Junction-to-board characterization parameter | NA | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | NA | °C/W |

7.5 Electrical Characteristics

Minimum and maximum specifications apply from –40°C to +105°C. Typical specifications are at 25°C. All specifications are at DVDD = 1.8 V, AVDD = 3 V, AVSS = 0 V, VREF = 2.4 V, external fCLK = 2.048 MHz, data rate = 8 kSPS, and gain = 1, unless otherwise noted.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| ANALOG INPUTS | ||||||||

| Ci | Input capacitance | 20 | pF | |||||

| IIB | Input bias current | PGA output in normal range | 5 | nA | ||||

| DC input impedance | 200 | MΩ | ||||||

| PGA PERFORMANCE | ||||||||

| Gain settings | 1, 2, 4, 8, 12 | |||||||

| BW | Bandwidth | See Table 3 | ||||||

| ADC PERFORMANCE | ||||||||

| DR | Data rate | fCLK = 2.048 MHz | 1 | 64 | kSPS | |||

| Resolution | DR = 1 kSPS, 2 kSPS, 4 kSPS, 8 kSPS, and 16 kSPS | 24 | Bits | |||||

| DR = 32 kSPS and 64 kSPS | 16 | Bits | ||||||

| CHANNEL PERFORMANCE (DC PERFORMANCE) | ||||||||

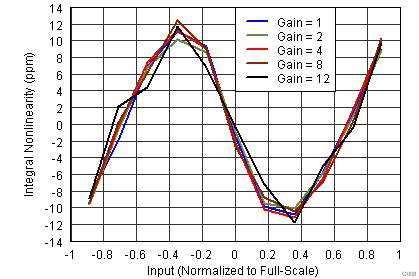

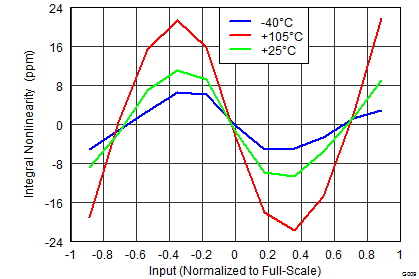

| INL | Integral nonlinearity | Full-scale, best fit | 10 | ppm | ||||

| Dynamic range | G = 1 | 105 | dB | |||||

| Gain settings other than 1 | See the Noise Measurements section | |||||||

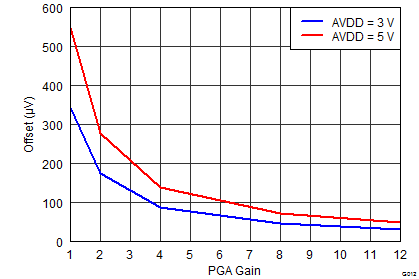

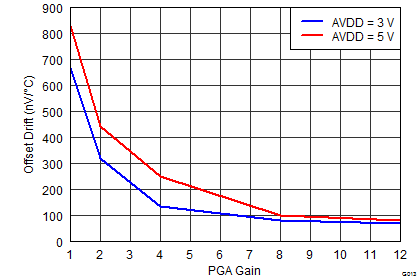

| EO | Offset error | 350 | μV | |||||

| Offset error drift | 0.65 | μV/°C | ||||||

| EG | Gain error | Excluding voltage reference error | 0.1% | |||||

| Gain drift | Excluding voltage reference drift | 3 | ppm/°C | |||||

| Gain match between channels | 0.2 | % of FS | ||||||

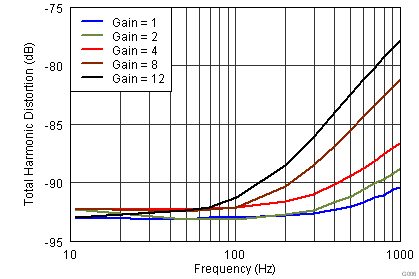

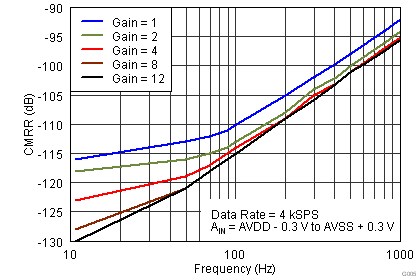

| CHANNEL PERFORMANCE (AC PERFORMANCE) | ||||||||

| CMRR | Common-mode rejection ratio | fCM = 50 Hz and 60 Hz(1) | –110 | dB | ||||

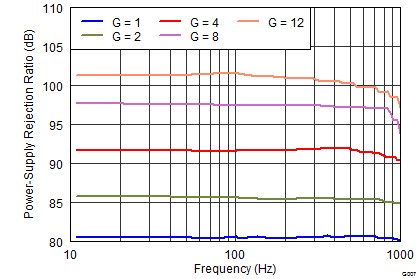

| PSRR | Power-supply rejection ratio | fPS = 50 Hz and 60 Hz | –80 | dB | ||||

| Crosstalk | fIN = 50 Hz and 60 Hz | –110 | dB | |||||

| Accuracy | 3000:1 dynamic range with a 1-second measurement (VRMS / IRMS) |

AVDD = 3 V, VREF = 2.4 V | 0.04% | |||||

| AVDD = 5 V, VREF = 4 V | 0.025% | |||||||

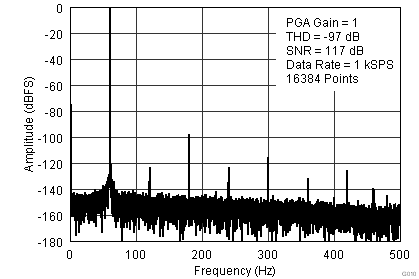

| SNR | Signal-to-noise ratio | fIN = 50 Hz and 60 Hz, gain = 1 | 107 | dB | ||||

| THD | Total harmonic distortion | 10 Hz, –0.5 dBFs | –93 | dB | ||||

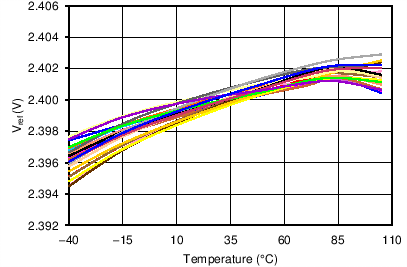

| INTERNAL REFERENCE | ||||||||

| VREF | Output voltage | TA = 25°C, VREF = 2.4 V | 2.394 | 2.4 | 2.406 | V | ||

| TA = 25°C, VREF = 4 V | 4 | V | ||||||

| VREF accuracy | ±0.2% | |||||||

| Temperature drift | TA = –40°C to +105°C | 20 | ppm/°C | |||||

| Start-up time | Settled to 0.2% | 150 | ms | |||||

| EXTERNAL REFERENCE | ||||||||

| Input impedance | 6 | kΩ | ||||||

| INTERNAL OSCILLATOR | ||||||||

| Accuracy | ±2% | |||||||

| TA = 25°C | ±0.5% | |||||||

| TA = –40°C to 105°C | 2.5% | |||||||

| Internal oscillator clock frequency | Nominal frequency | 2.048 | MHz | |||||

| Internal oscillator start-up time | 20 | μs | ||||||

| Internal oscillator power consumption | 120 | μW | ||||||

| FAULT DETECT AND ALARM | ||||||||

| Comparator threshold accuracy | ±30 | mV | ||||||

| OPERATIONAL AMPLIFIER | ||||||||

| Integrated noise | 0.1 Hz to 250 Hz | 9 | µVRMS | |||||

| Noise density | 2 kHz | 120 | nV/√Hz | |||||

| GBP | Gain bandwidth product | 50 kΩ || 10-pF load | 100 | kHz | ||||

| SR | Slew rate | 50 kΩ || 10-pF load | 0.25 | V/µs | ||||

| Load current | 50 | µA | ||||||

| THD | Total harmonic distortion | fIN = 100 Hz | 70 | dB | ||||

| Common-mode input range | AVSS + 0.7 | AVDD – 0.3 | V | |||||

| Quiescent power consumption | 20 | µA | ||||||

| SYSTEM MONITORS | ||||||||

| Supply reading error | Analog | 2% | ||||||

| Digital | 2% | |||||||

| Device wake up | From power-up to DRDY low | 150 | ms | |||||

| STANDBY mode | 31.25 | µs | ||||||

| Temperature sensor reading | Voltage | TA = 25°C | 145 | mV | ||||

| Coefficient | 490 | μV/°C | ||||||

| SELF-TEST SIGNAL | ||||||||

| Signal frequency | See the Register Map section for settings | fCLK / 221 | Hz | |||||

| fCLK / 220 | ||||||||

| Signal voltage | See the Register Map section for settings | ±1 | mV | |||||

| ±2 | ||||||||

| DIGITAL INPUT AND OUTPUT (DVDD = 1.8 V to 3.6 V) | ||||||||

| VIH | Logic level, input voltage |

High | 0.8 DVDD | DVDD+0.1 | V | |||

| VIL | Low | –0.1 | 0.2 DVDD | V | ||||

| VOH | Logic level, output voltage |

High | IOH = –500 µA | 0.9 DVDD | V | |||

| VOL | Low | IOL = +500 µA | 0.1 DVDD | V | ||||

| IIN | Input current | 0 V < VDigitalInput < DVDD | –10 | 10 | μA | |||

| SUPPLY CURRENT (OPERATIONAL AMPLIFIER TURNED OFF) | ||||||||

| IAVDD | Normal mode | AVDD – AVSS = 3 V | 5.1 | mA | ||||

| AVDD – AVSS = 5 V | 5.8 | mA | ||||||

| IDVDD | DVDD = 3.3 V | 1 | mA | |||||

| DVDD = 1.8 V | 0.4 | mA | ||||||

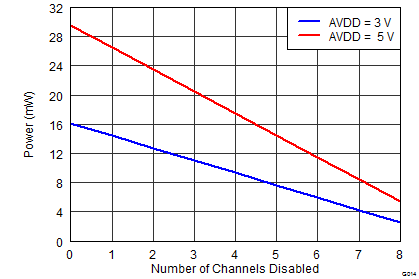

| POWER DISSIPATION (ANALOG SUPPLY = 3 V) | ||||||||

| Quiescent power dissipation | ADS131E04 | Normal mode | 9.3 | 10.2 | mW | |||

| Power-down mode | 10 | µW | ||||||

| Standby mode | 2 | mW | ||||||

| ADS131E06 | Normal mode | 12.7 | 13.5 | mW | ||||

| Power-down mode | 10 | µW | ||||||

| Standby mode | 2 | mW | ||||||

| ADS131E08 | Normal mode | 16 | 17.6 | mW | ||||

| Power-down mode | 10 | µW | ||||||

| Standby mode | 2 | mW | ||||||

| POWER DISSIPATION (ANALOG SUPPLY = 5 V) | ||||||||

| Quiescent power dissipation | ADS131E04 | Normal mode | 18 | mW | ||||

| Power-down mode | 20 | µW | ||||||

| Standby mode | 4.2 | mW | ||||||

| ADS131E06 | Normal mode | 24.3 | mW | |||||

| Power-down mode | 20 | µW | ||||||

| Standby mode | 4.2 | mW | ||||||

| ADS131E08 | Normal mode | 29.7 | mW | |||||

| Power-down mode | 20 | µW | ||||||

| Standby mode | 4.2 | mW | ||||||

7.6 Timing Requirements

over operating ambient temperature range and DVDD = 1.7 V to 3.6 V (unless otherwise noted)| 2.7 V ≤ DVDD ≤ 3.6 V | 1.7 V ≤ DVDD ≤ 2.0 V | UNIT | ||||

|---|---|---|---|---|---|---|

| MIN | MAX | MIN | MAX | |||

| tCLK | Master clock period | 444 | 588 | 444 | 588 | ns |

| tCSSC | Delay time, first SCLK rising edge after CS falling edge | 6 | 17 | ns | ||

| tSCLK | SCLK period | 50 | 66.6 | ns | ||

| tSPWH, L | Pulse duration, SCLK high or low | 15 | 25 | ns | ||

| tDIST | Setup time, DIN valid before SCLK falling edge | 10 | 10 | ns | ||

| tDIHD | Hold time, DIN valid after SCLK falling edge | 10 | 11 | ns | ||

| tCSH | Pulse duration, CS high | 2 | 2 | tCLK | ||

| tSCCS | Delay time, CS rising edge after final SCLK falling edge | 4 | 4 | tCLK | ||

| tSDECODE | Command decode time | 4 | 4 | tCLK | ||

| tDISCK2ST | Setup time, DAISY_IN valid before SCLK falling edge | 10 | 10 | ns | ||

| tDISCK2HT | Hold time, DAISY_IN valid after SCLK falling edge | 10 | 10 | ns | ||

7.7 Switching Characteristics

over operating ambient temperature range, DVDD = 1.7 V to 3.6 V, and load on DOUT = 20 pF || 100 kΩ (unless otherwise noted)| PARAMETER | 2.7 V ≤ DVDD ≤ 3.6 V | 1.7 V ≤ DVDD ≤ 2.0 V | UNIT | |||

|---|---|---|---|---|---|---|

| MIN | MAX | MIN | MAX | |||

| tCSDOD | Propagation delay time, CS falling edge to DOUT driven | 10 | 20 | ns | ||

| tDOST | Propagation delay time, SCLK rising edge to valid new DOUT | 17 | 32 | ns | ||

| tDOHD | Hold time, SCLK falling edge to invalid DOUT | 10 | 10 | ns | ||

| tCSDOZ | Propagation delay time, CS rising edge to DOUT high impedance | 10 | 20 | ns | ||

NOTE:

SPI settings are CPOL = 0 and CPHA = 1.

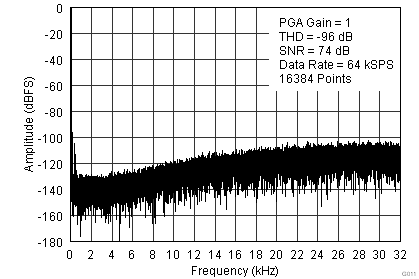

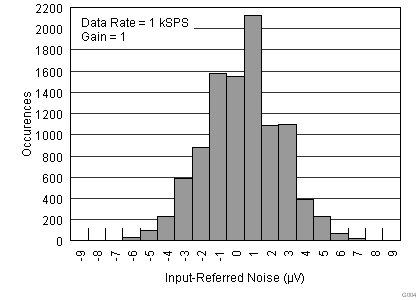

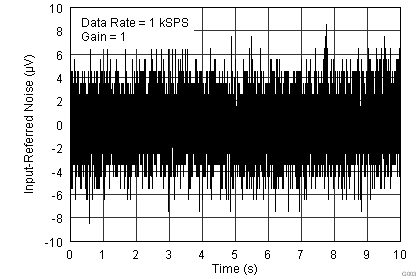

7.8 Typical Characteristics

all plots are at TA = 25°C, AVDD = 3 V, AVSS = 0 V, DVDD = 1.8 V, internal VREFP = 2.4 V, VREFN = AVSS, external clock = 2.048 MHz, data rate = 8 kSPS, and gain = 1, unless otherwise noted.

8 Parameter Measurement Information

8.1 Noise Measurements

Adjust the data rate and PGA gain to optimize the ADS131E0x noise performance. When averaging is increased by reducing the data rate, noise drops correspondingly. Increasing the PGA gain reduces the input-referred noise, which is particularly useful when measuring low-level signals. Table 1 summarizes the ADS131E0x noise performance with a 3-V analog power supply. Table 2 summarizes the ADS131E0x noise performance with a 5-V analog power supply. Data are representative of typical noise performance at TA = 25°C. Data shown are the result of averaging the readings from multiple devices and are measured with the inputs shorted together. A minimum of 1000 consecutive readings are used to calculate the RMS noise for each reading. For the two highest data rates, noise is limited by the ADC quantization noise and does not have a Gaussian distribution. Table 1 and Table 2 show measurements taken with an internal reference. Data are representative of the ADS131E0x noise performance shown in both effective number of bits (ENOB) and dynamic range when using a low-noise external reference (such as the REF5025). ENOB data in Table 1 and Table 2 are calculated using Equation 1 and dynamic range data in Table 1 and Table 2 are calculated using Equation 2.

Table 1. Input-Referred Noise, 3-V Analog Supply, and 2.4-V Reference

| DR BITS (CONFIG1 Register) |

OUTPUT DATA RATE (kSPS) | –3-dB BANDWIDTH (Hz) | PGA GAIN | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| x1 | x2 | x4 | x8 | x12 | ||||||||

| DYNAMIC RANGE (dB) | ENOB | DYNAMIC RANGE (dB) | ENOB | DYNAMIC RANGE (dB) | ENOB | DYNAMIC RANGE (dB) | ENOB | DYNAMIC RANGE (dB) | ENOB | |||

| 000 | 64 | 16768 | 74.1 | 12.31 | 74.1 | 12.30 | 74.0 | 12.29 | 74.0 | 12.29 | 73.9 | 12.27 |

| 001 | 32 | 8384 | 89.6 | 14.89 | 89.6 | 14.88 | 89.4 | 14.85 | 88.6 | 14.71 | 87.6 | 14.55 |

| 010 | 16 | 4192 | 102.8 | 17.07 | 102.3 | 16.99 | 100.6 | 16.72 | 97.1 | 16.12 | 94.2 | 15.65 |

| 011 | 8 | 2096 | 108.2 | 18.0 | 107.4 | 17.9 | 105.2 | 17.5 | 101.6 | 16.9 | 98.9 | 16.5 |

| 100 | 4 | 1048 | 111.4 | 18.6 | 109.4 | 18.4 | 107.4 | 18.1 | 103.5 | 17.4 | 100.5 | 17.0 |

| 101 | 2 | 524 | 114.6 | 19.1 | 113.7 | 19.0 | 111.4 | 18.6 | 107.7 | 18.0 | 104.9 | 17.5 |

| 110 | 1 | 262 | 117.7 | 19.6 | 116.8 | 19.5 | 114.5 | 19.1 | 110.7 | 18.5 | 108.0 | 18.0 |

Table 2. Input-Referred Noise, 5-V Analog Supply, And 4-V Reference

| DR BITS (CONFIG1 Register) |

OUTPUT DATA RATE (kSPS) | –3-dB BANDWIDTH (Hz) | PGA GAIN | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| x1 | x2 | x4 | x8 | x12 | ||||||||

| DYNAMIC RANGE (dB) | ENOB | DYNAMIC RANGE (dB) | ENOB | DYNAMIC RANGE (dB) | ENOB | DYNAMIC RANGE (dB) | ENOB | DYNAMIC RANGE (dB) | ENOB | |||

| 000 | 64 | 16768 | 74.7 | 12.41 | 74.7 | 12.41 | 74.7 | 12.41 | 74.7 | 12.41 | 74.6 | 12.39 |

| 001 | 32 | 8384 | 90.3 | 15.01 | 90.3 | 15.00 | 90.2 | 14.99 | 89.9 | 14.93 | 89.4 | 14.85 |

| 010 | 16 | 4192 | 104.3 | 17.33 | 104 | 17.28 | 103.1 | 17.12 | 100.5 | 16.70 | 98.1 | 16.3 |

| 011 | 8 | 2096 | 112.3 | 18.7 | 111.6 | 18.6 | 109.7 | 18.3 | 106.3 | 17.7 | 103.8 | 17.3 |

| 100 | 4 | 1048 | 116 | 19.3 | 115.2 | 19.2 | 113.1 | 18.8 | 109.5 | 18.3 | 106.9 | 17.8 |

| 101 | 2 | 524 | 119.1 | 19.8 | 118.2 | 19.7 | 116.2 | 19.4 | 112.6 | 18.8 | 109.9 | 18.3 |

| 110 | 1 | 262 | 122.1 | 20.4 | 121.3 | 20.2 | 119.1 | 19.9 | 115.6 | 19.3 | 112.9 | 18.8 |