ZHCSH75A September 2017 – December 2017 ADS7142

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics - All Modes

- 6.6 Electrical Characteristics - Manual Mode

- 6.7 Electrical Characteristics - Autonomous Modes

- 6.8 Electrical Characteristics - High Precision Mode

- 6.9 Timing Requirements

- 6.10 Switching Characteristics

- 6.11 Typical Characteristics for All Modes

- 6.12 Typical Characteristics for Manual Mode

- 6.13 Typical Characteristics for Autonomous Modes

- 6.14 Typical Characteristics for High Precision Mode

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Optimizing Power Consumed by the Device

- 7.6

Register Map

- 7.6.1 RESET REGISTERS

- 7.6.2 FUNCTIONAL MODE SELECT REGISTERS

- 7.6.3 INPUT CONFIG REGISTER

- 7.6.4 ANALOG MUX and SEQUENCER REGISTERS

- 7.6.5 OSCILLATOR and TIMING CONTROL REGISTERS

- 7.6.6 DATA BUFFER CONTROL REGISTER

- 7.6.7

ACCUMULATOR CONTROL REGISTERS

- 7.6.7.1 ACC_EN Register (address = 30h), [reset = 00h]

- 7.6.7.2 ACC_CH0_LSB Register (address = 08h), [reset = 00h]

- 7.6.7.3 ACC_CH0_MSB Register (address = 09h), [reset = 00h]

- 7.6.7.4 ACC_CH1_LSB Register (address = 0Ah), [reset = 00h]

- 7.6.7.5 ACC_CH1_MSB Register (address = 0Bh), [reset = 00h]

- 7.6.7.6 ACCUMULATOR_STATUS Register (address = 02h), [reset = 00h]

- 7.6.8

DIGITAL WINDOW COMPARATOR REGISTERS

- 7.6.8.1 ALERT_DWC_EN Register (address = 37h), [reset = 00h]

- 7.6.8.2 ALERT_CHEN (address = 34h), [reset = 00h]

- 7.6.8.3 DWC_HTH_CH0_MSB Register (address = 39h), [reset = 00h]

- 7.6.8.4 DWC_HTH_CH0_LSB Register (address = 38h), [reset = 00h]

- 7.6.8.5 DWC_LTH_CH0_MSB Register (address = 3Bh), [reset = 00h]

- 7.6.8.6 DWC_LTH_CH0_LSB Register (address = 3Ah), [reset = 00h]

- 7.6.8.7 DWC_HYS_CH0 (address = 40h), [reset = 00h]

- 7.6.8.8 DWC_HTH_CH1_MSB Register (address = 3Dh), [reset = 00h]

- 7.6.8.9 DWC_HTH_CH1_LSB Register (address = 3Ch), [reset = 00h]

- 7.6.8.10 DWC_LTH_CH1_MSB Register (address = 3Fh), [reset = 00h]

- 7.6.8.11 DWC_LTH_CH1_LSB Register (address = 3Eh), [reset = 00h]

- 7.6.8.12 DWC_HYS_CH1 (address = 41h), [reset = 00h]

- 7.6.8.13 PRE_ALT_MAX_EVENT_COUNT Register (address = 36h), [reset = 00h]

- 7.6.8.14 ALERT_TRIG_CHID Register (address = 03h), [reset = 00h]

- 7.6.8.15 ALERT_LOW_FLAGS Register (address = 0C), [reset = 00h]

- 7.6.8.16 ALERT_HIGH_FLAGS Register (address = 0Eh), [reset = 00h]

- 8 Application and Implementation

- 9 Power-Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

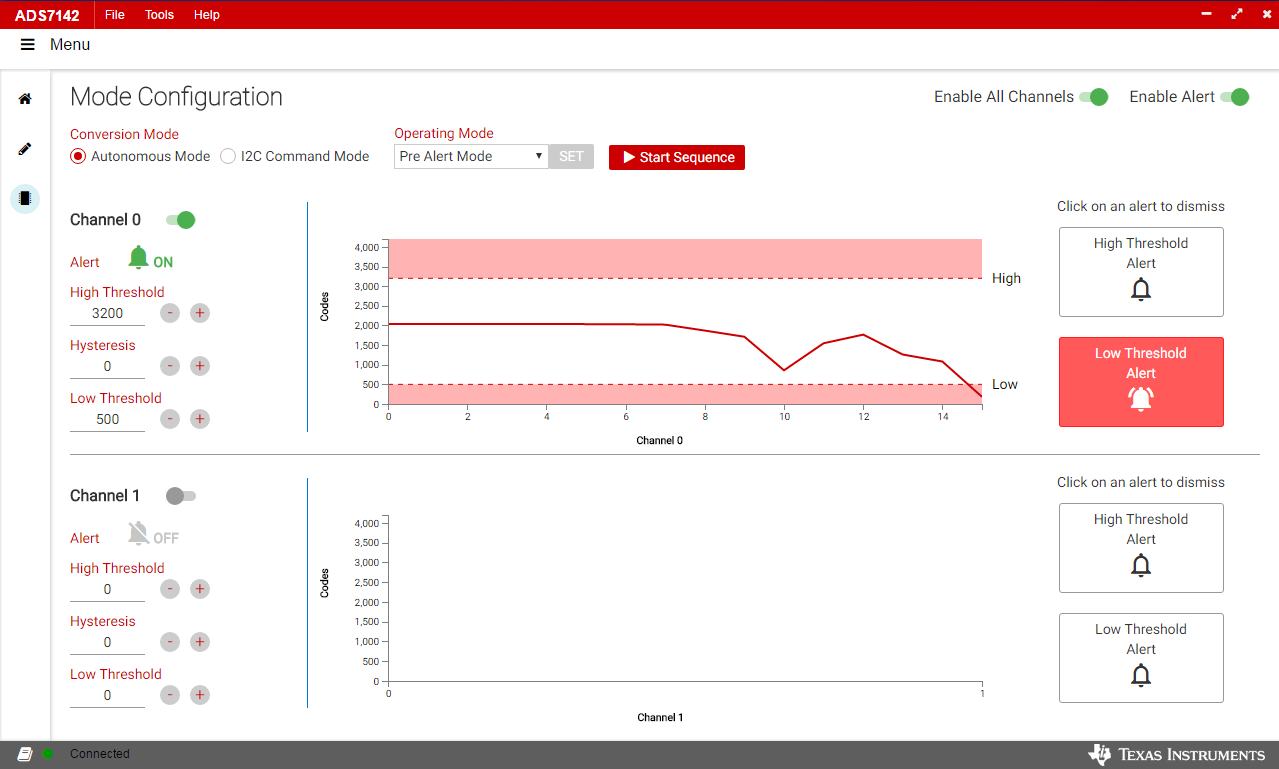

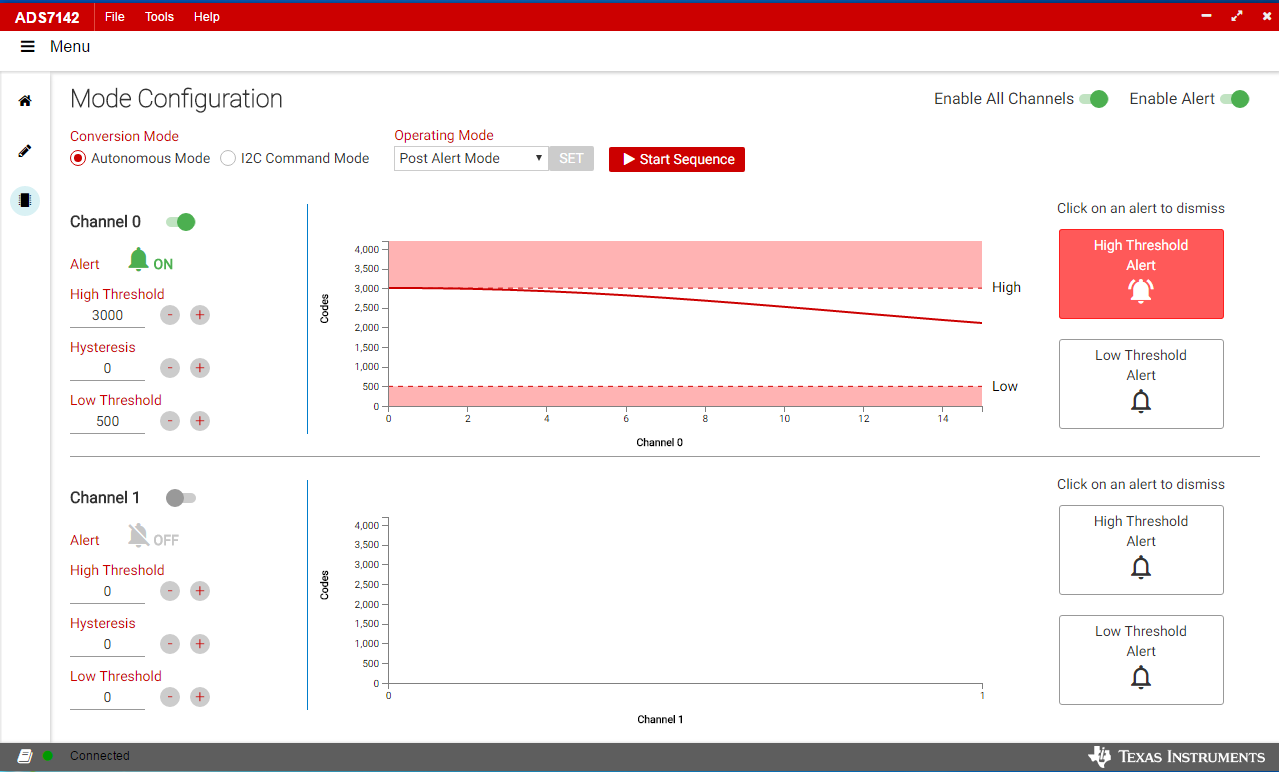

8.2.1.3 Application Curve

Figure 117. Pre-Alert Data Capture

Figure 117. Pre-Alert Data Capture

Figure 118. Post Alert Data Capture

Figure 118. Post Alert Data Capture