ZHCSPS0A May 2023 – June 2024 AFE78201 , AFE88201

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 引脚配置和功能

- 5 规格

- 6 详细说明

- 7 寄存器映射

- 8 应用和实施

- 9 器件和文档支持

- 10修订历史记录

- 11机械、封装和可订购信息

6.3.1.5 可编程压摆率

压摆率功能可控制输出电压或电流的变化速率。默认情况下已禁用该功能,但可以通过向 DAC_CFG.SR_EN 位写入逻辑 1 来启用该功能。在禁用压摆率控制功能的情况下,输出会以受输出驱动电路和所连负载限制的速率发生平滑变化。

启用该功能后,输出不会直接在两个值之间转换。相反,输出会以 DAC_CFG.SR_STEP[2:0] 和 DAC_CFG.SR_CLK[2:0] 定义的速率进行数字步进。SR_CLK 定义数字转换更新的速率。SR_STEP 定义每次更新时输出值的变化量。寄存器说明显示了 SR_STEP 和 SR_CLK 的不同设置。

输出转换所需的时间表示为方程式 6:

方程式 6.

其中

- Slew Time 以秒为单位进行表示

- Slew Step 由 DAC_CFG.SR_STEP 控制

- Slew Clock Rate 由 DAC_CFG.SR_CLK 控制

启用压摆率控制功能后,输出会以编程的压摆率发生变化。这种配置会导致输出形成梯形。如果清除代码置为有效(请参阅节 6.3.1.6),则输出将以编程的压摆率转换为 DAC_CLR_CODE 值。当写入新的 DAC 数据后,输出开始以当前 DAC 代码和新 DAC 数据确定的压摆率转换为新值。

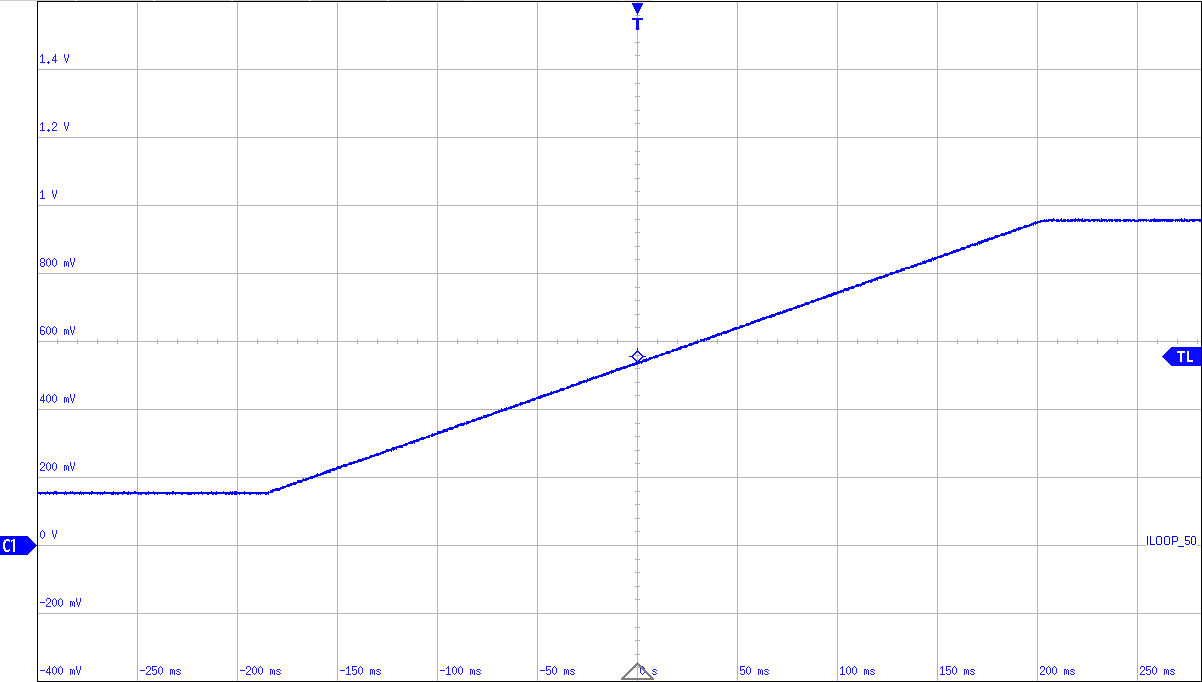

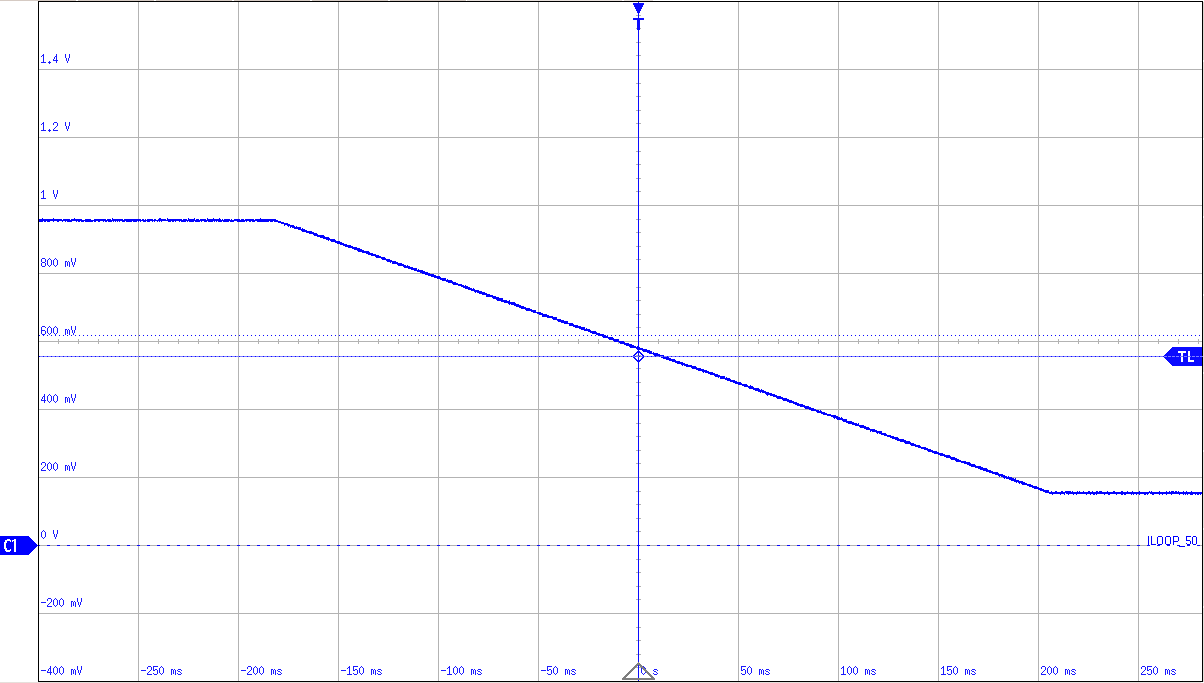

有两种压摆率控制模式可供使用:线性(默认)和正弦。图 6-3 和图 6-4 分别显示了典型的上升和下降 DAC 输出波形。

| 在 40Ω 分流器上测得的 4mA (0x0BA3) 至 24mA (0xF45D) 电流 |

| 在 40Ω 分流器上测得的 24mA (0xF45D) 至 4mA (0x0BA3) 电流 |

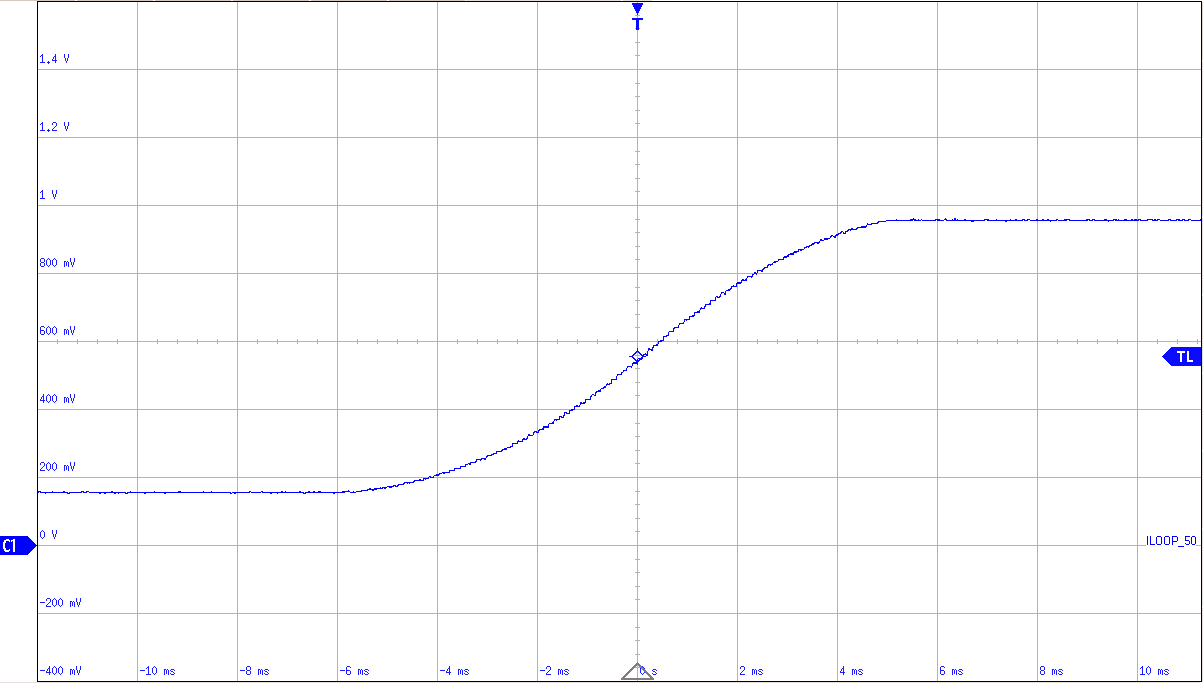

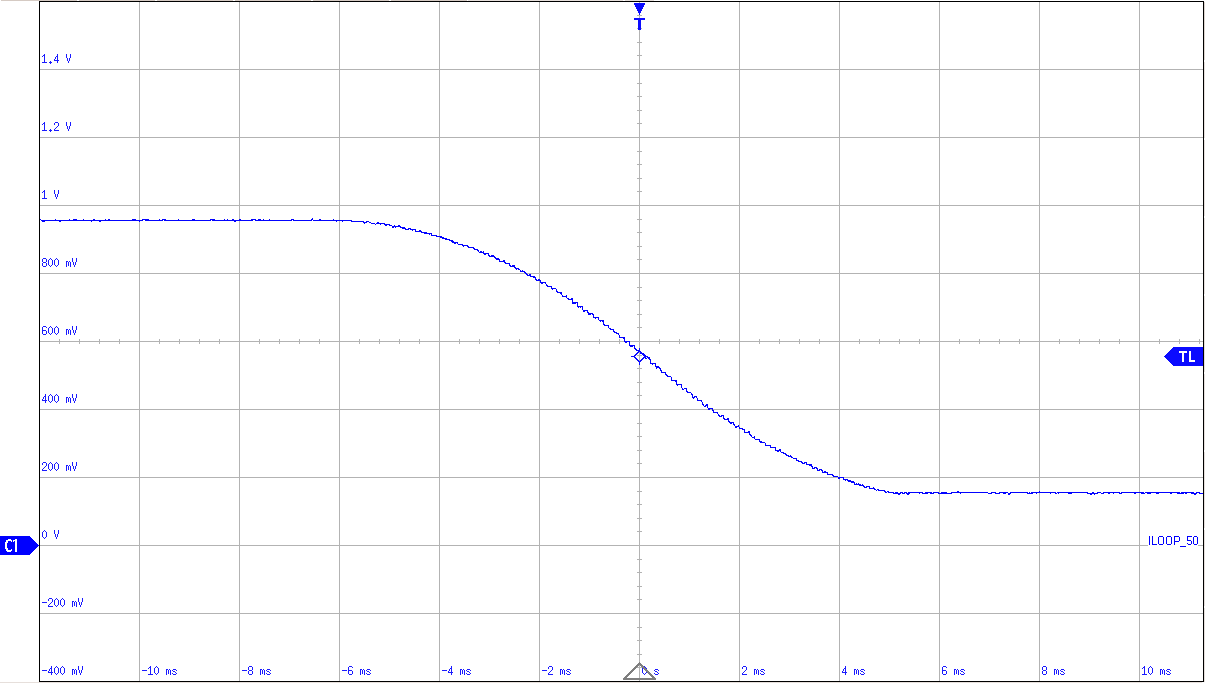

正弦模式可实现快速 DAC 稳定,同时改善模拟变化率特性。正弦模式由 DAC_CFG.SR_MODE 位进行选择。图 6-5 和图 6-6 分别显示了具有正弦压摆率控制功能的典型上升和下降 DAC 输出波形。

| 在 40Ω 分流器上测得的 4mA (0x0BA3) 至 24mA (0xF45D) 电流 |

| 在 40Ω 分流器上测得的 24mA (0xF45D) 至 4mA (0x0BA3) 电流 |

如果在 DAC 执行压摆率命令时禁用了压摆率功能,则会中止压摆率操作,且 DAC 输出将转至目标代码。