at

TA = 25°C, PVDD = VDD = IOVDD = 1.8 V, external or internal VREFIO =

1.25 V, RLOAD = 50 kΩ to GND, CLOAD = 100 pF to GND, and

digital inputs at IOVDD or GND (unless otherwise noted)

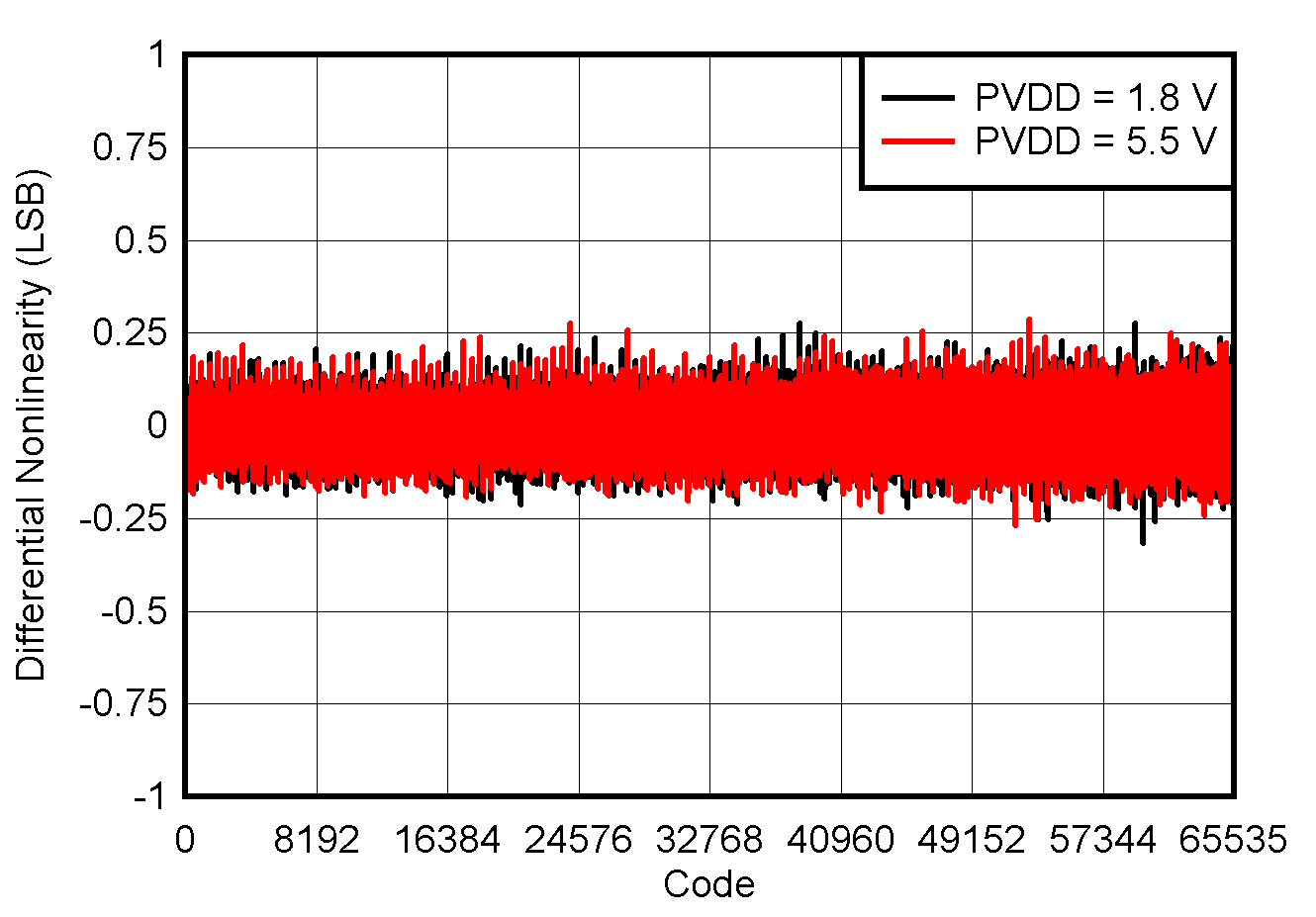

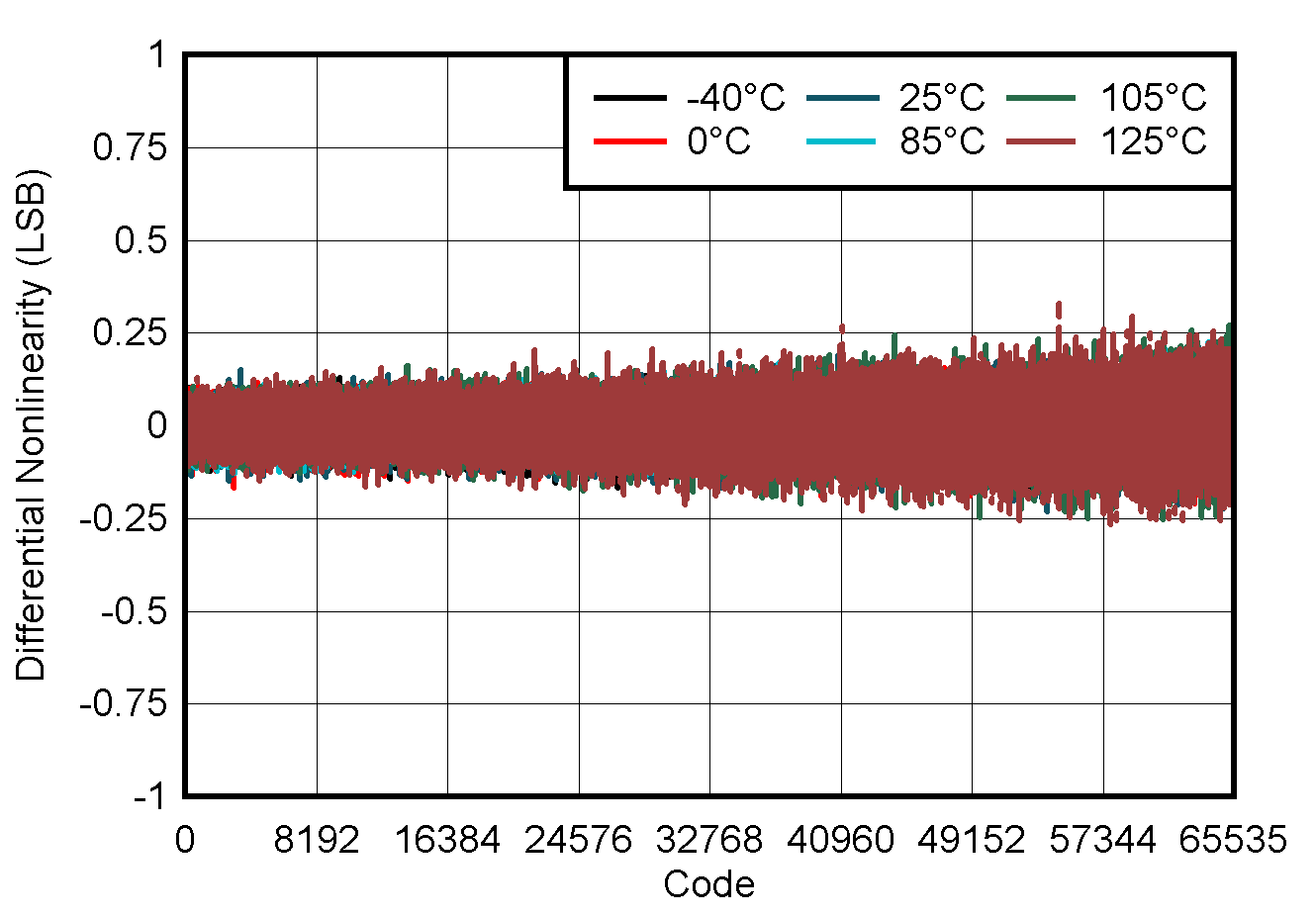

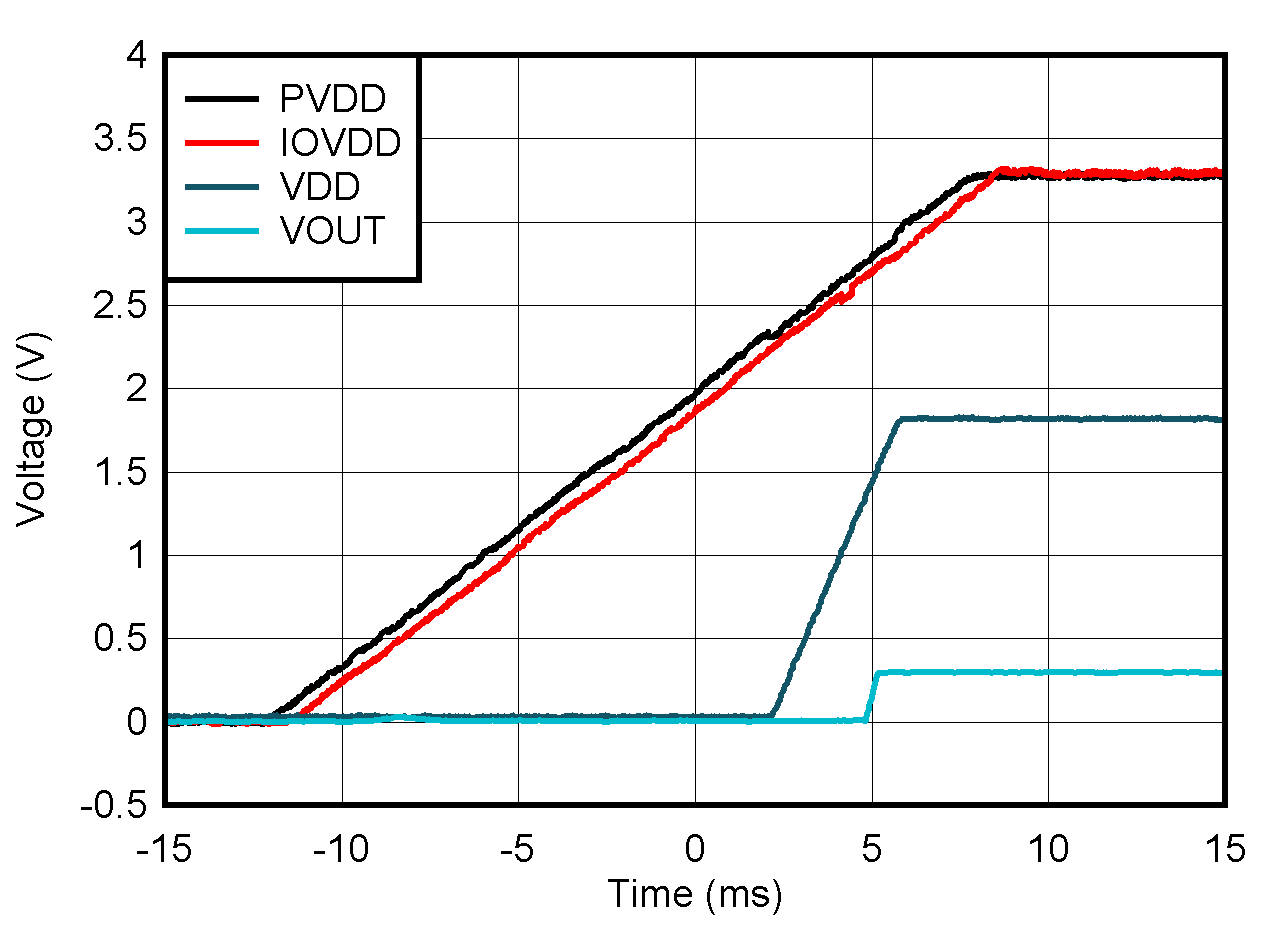

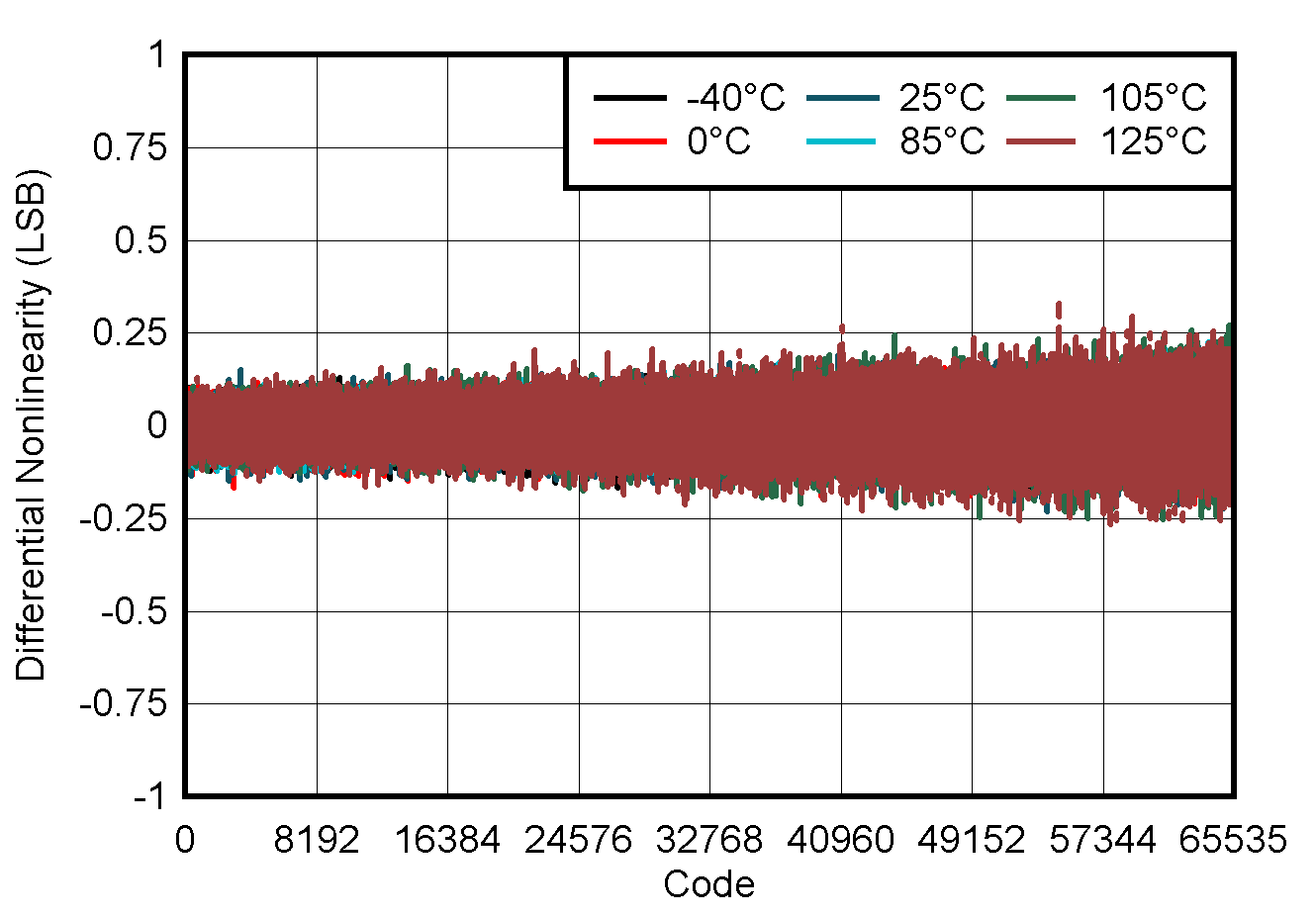

Figure 6-3 DAC

DNL vs Digital Input Code

Figure 6-3 DAC

DNL vs Digital Input Code Figure 6-5 DAC

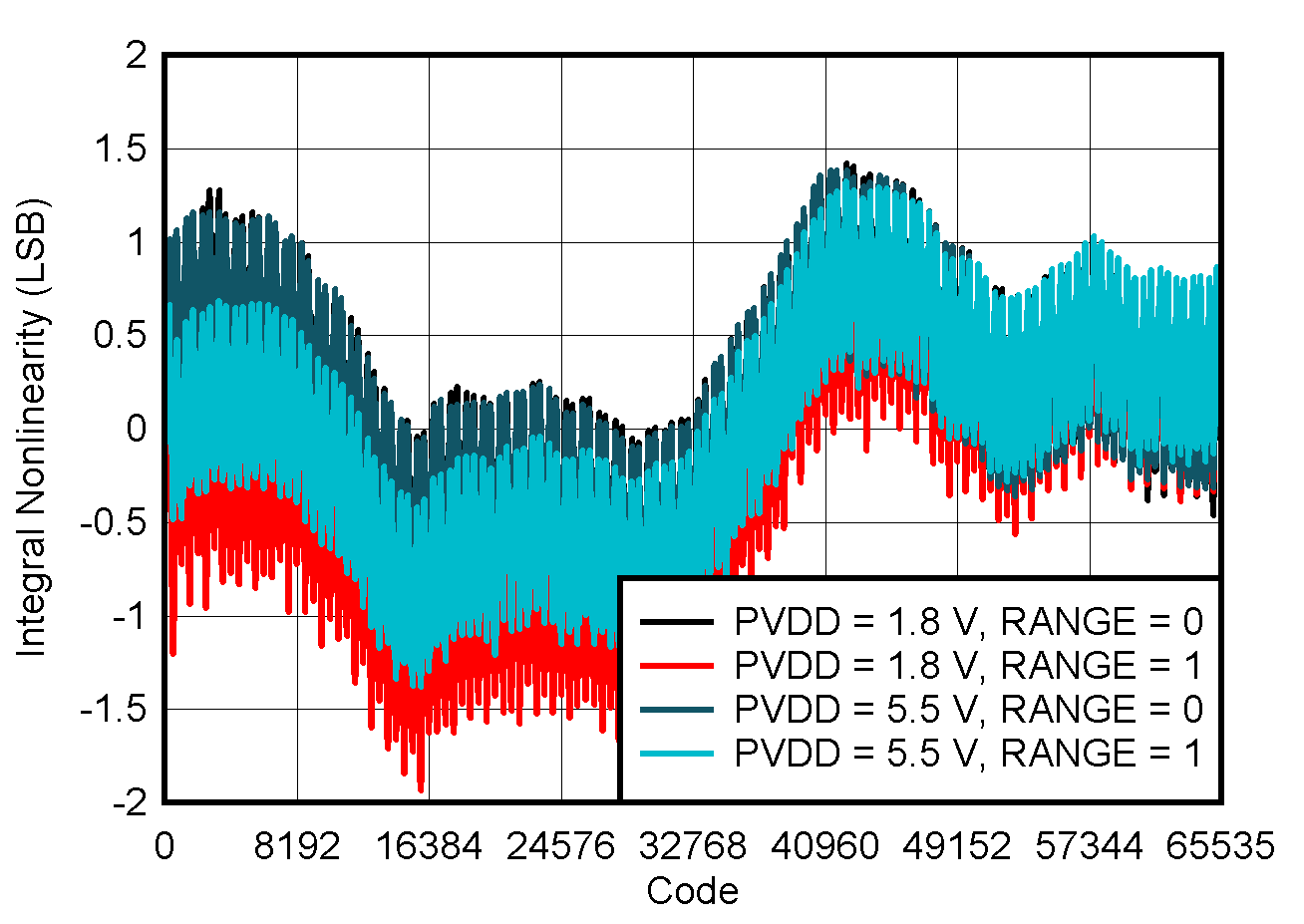

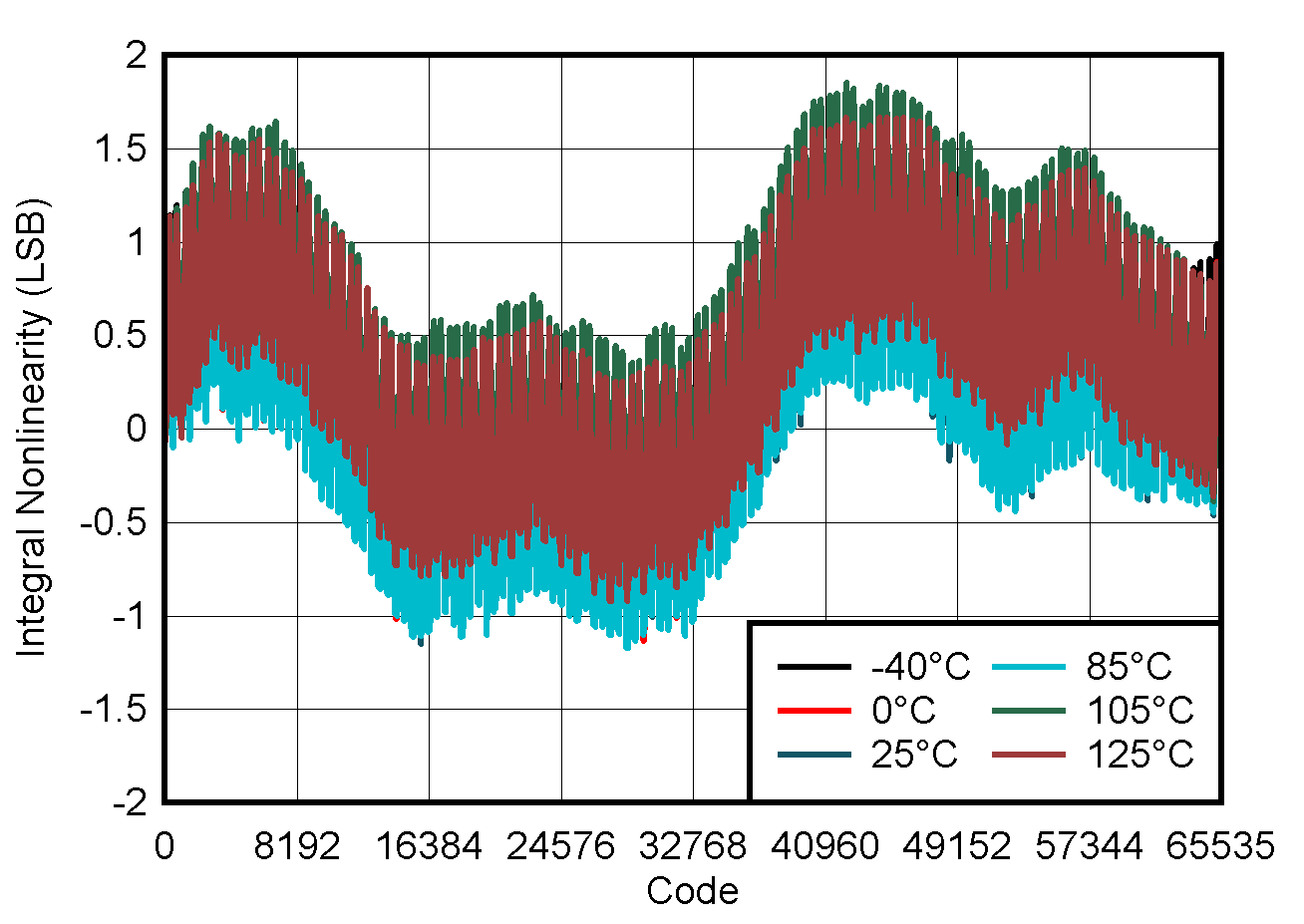

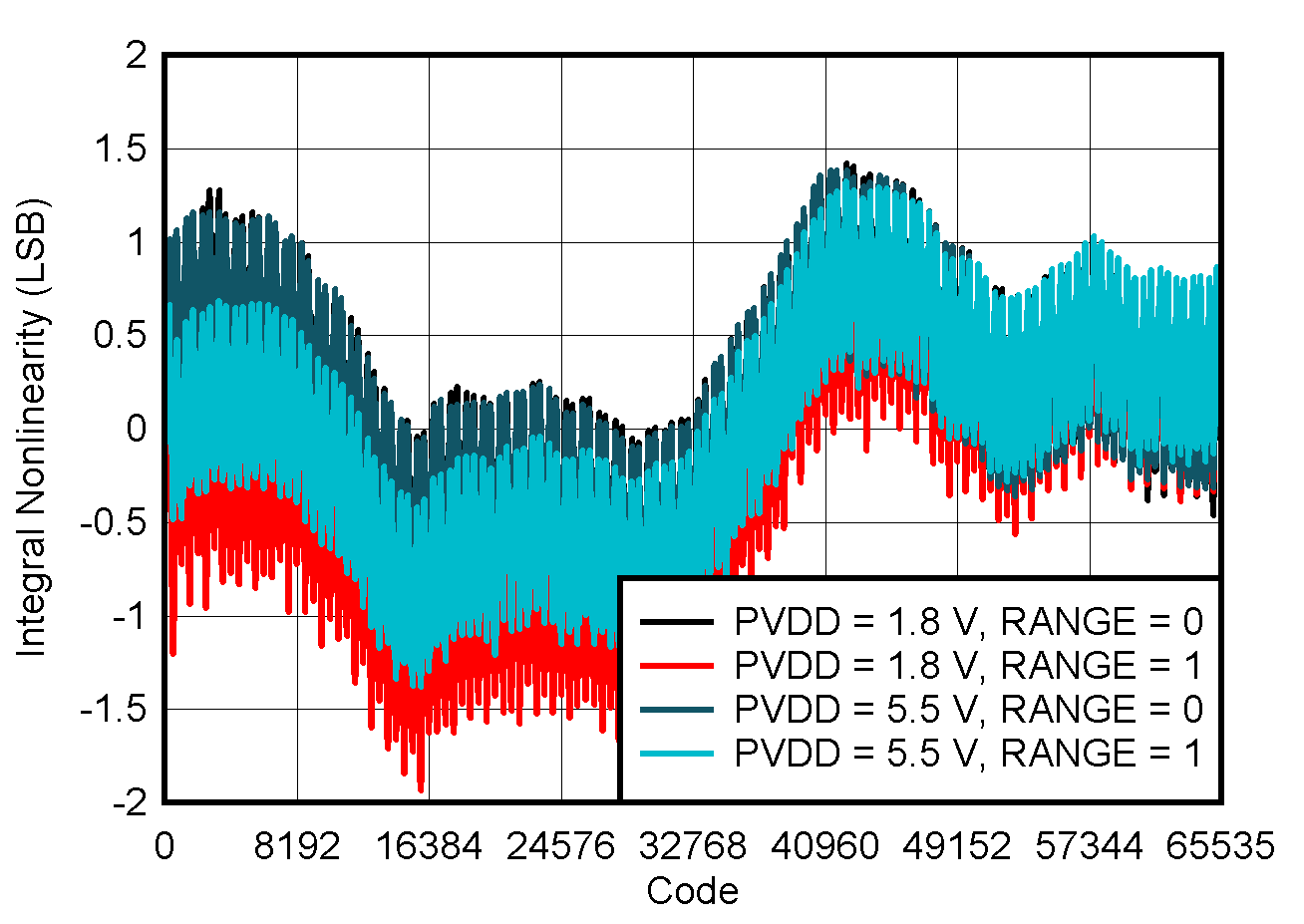

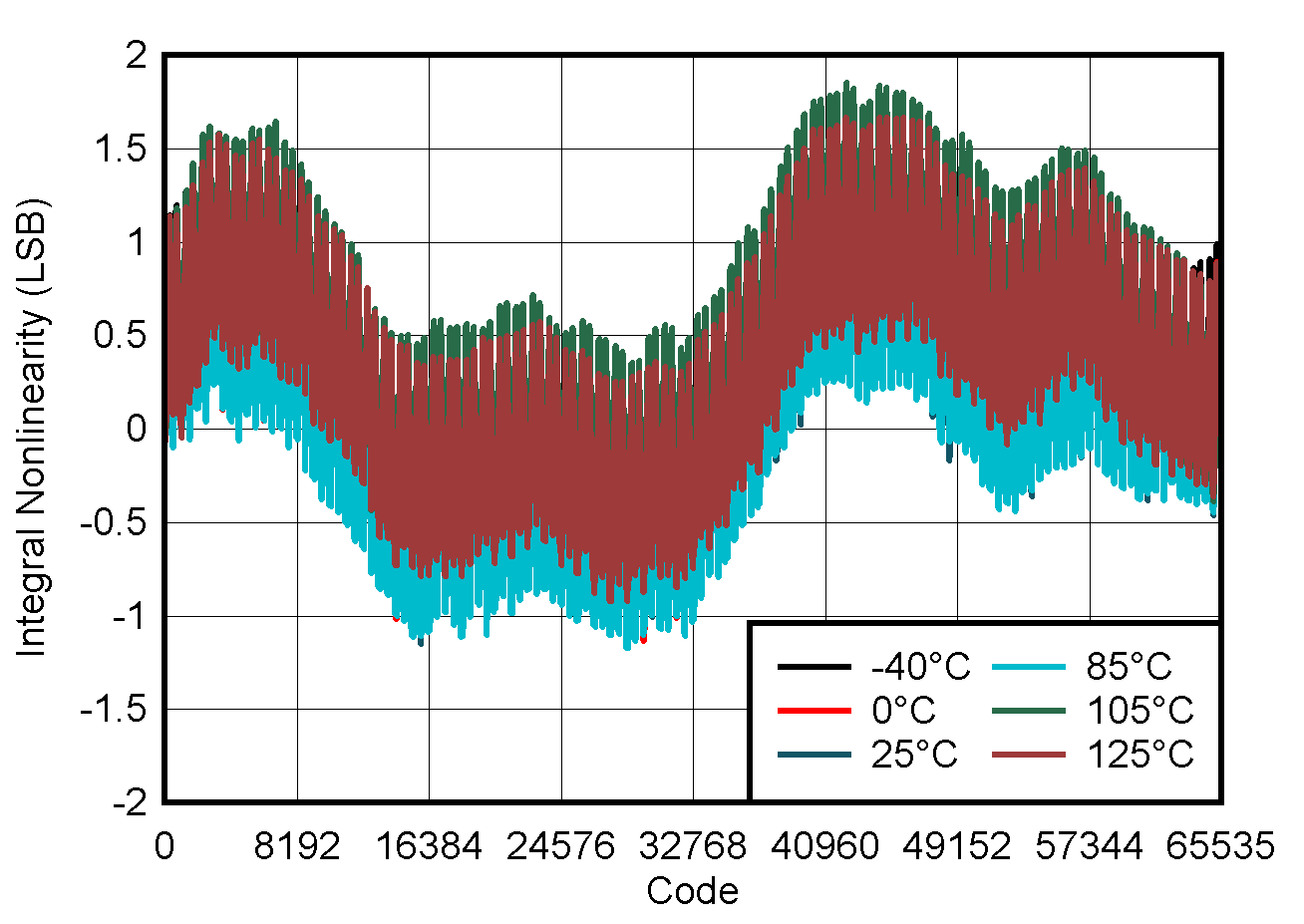

INL vs Digital Input Code

Figure 6-5 DAC

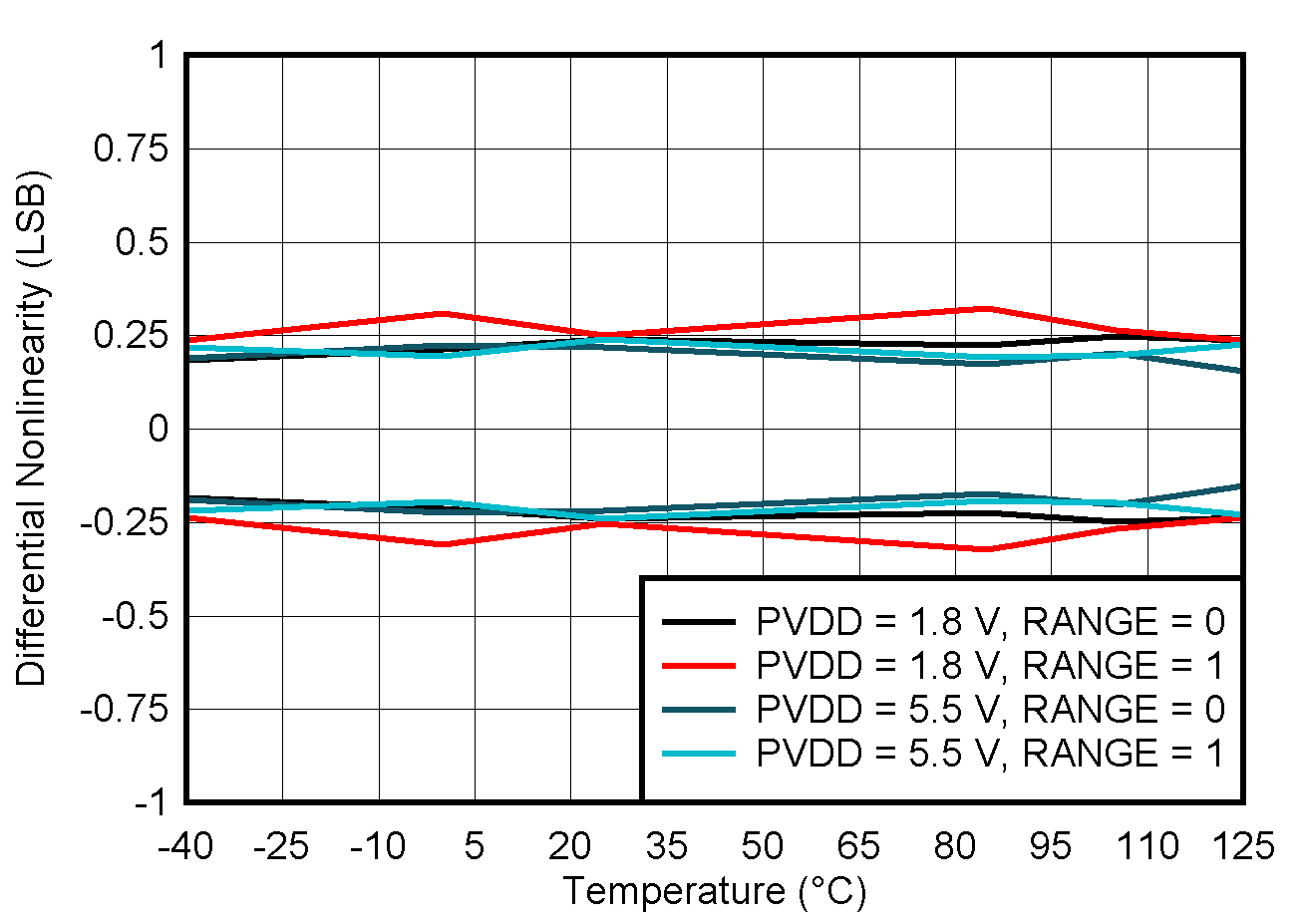

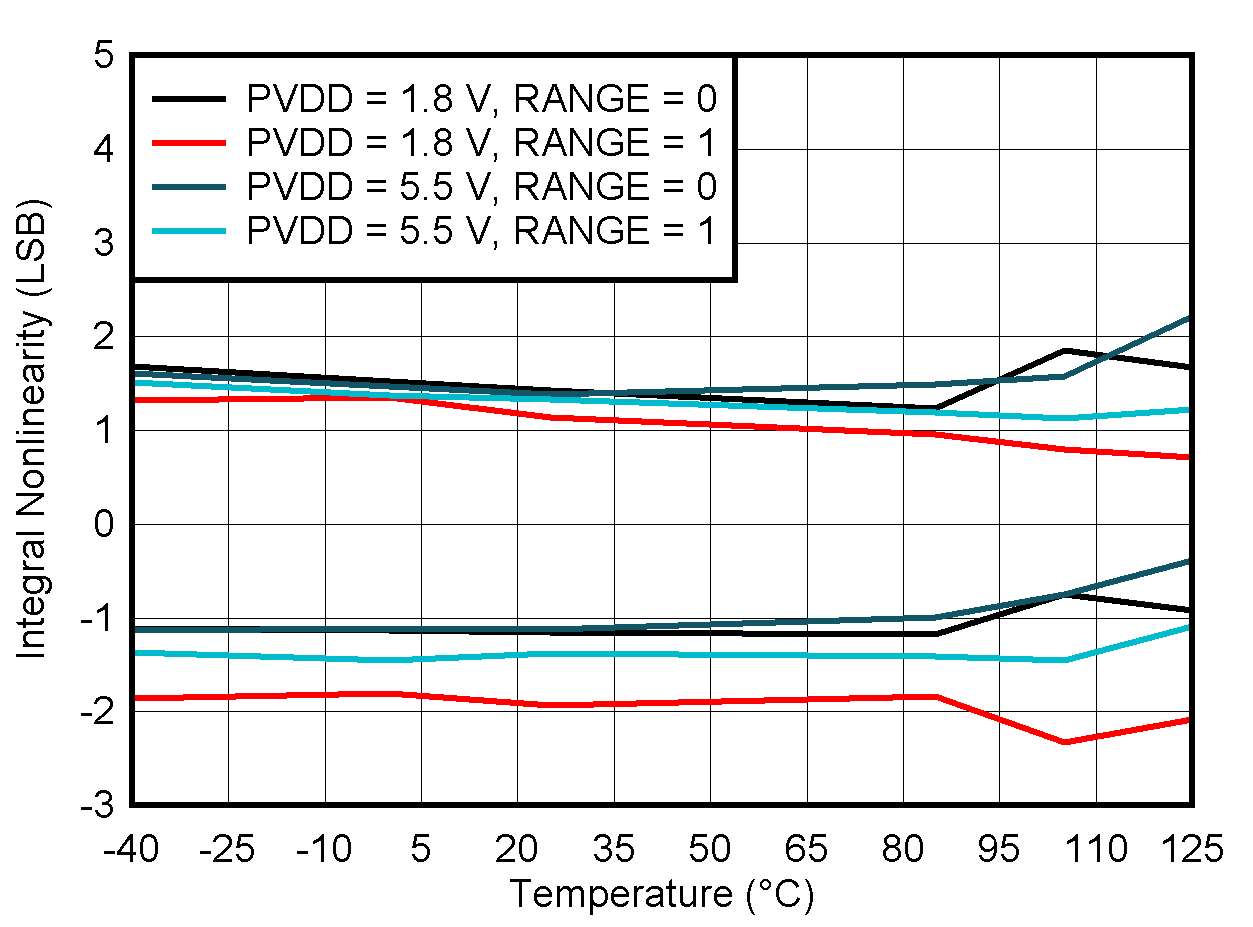

INL vs Digital Input Code Figure 6-7 MIN

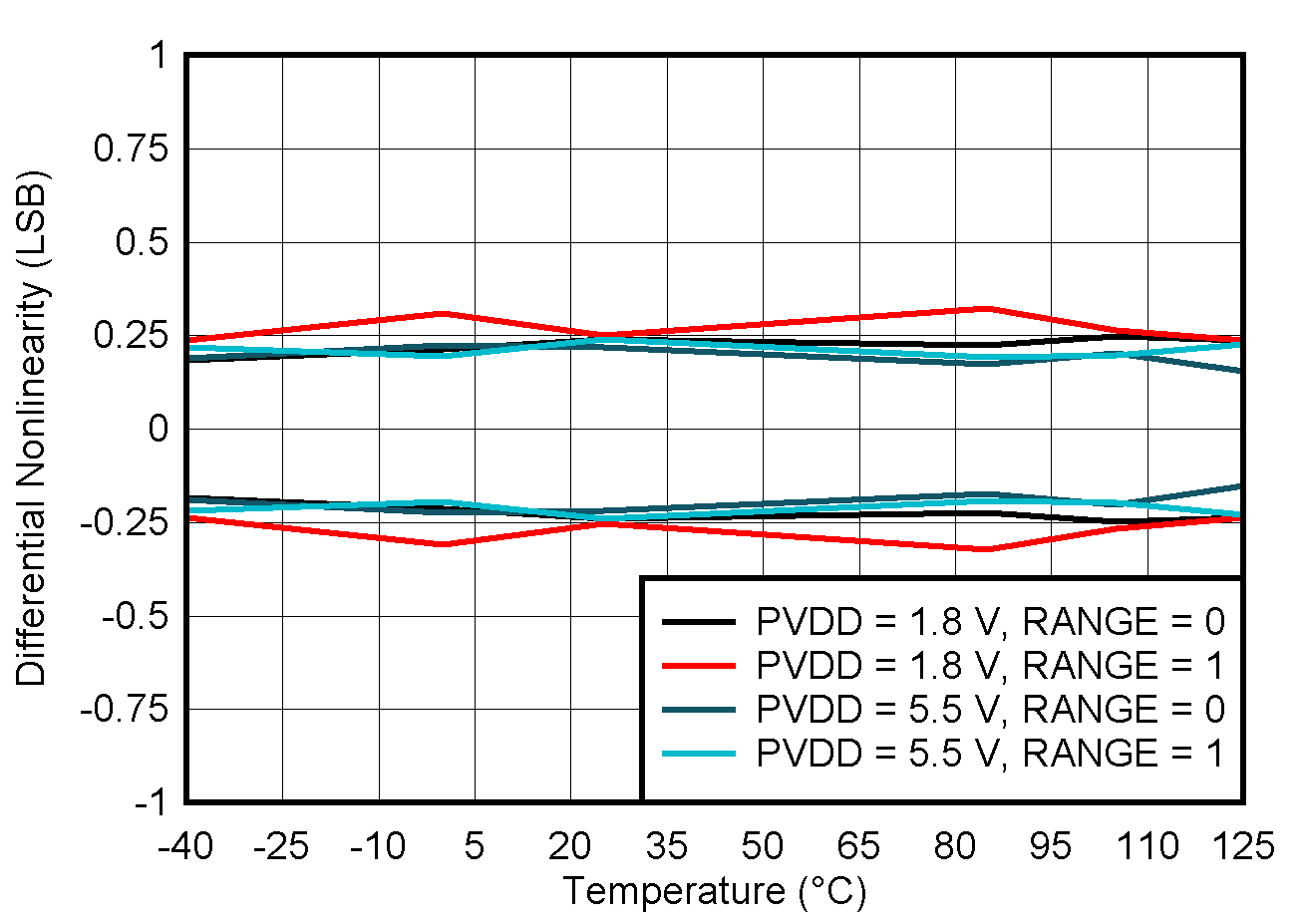

and MAX DAC DNL Range vs Temperature

Figure 6-7 MIN

and MAX DAC DNL Range vs Temperature Figure 6-9 DAC

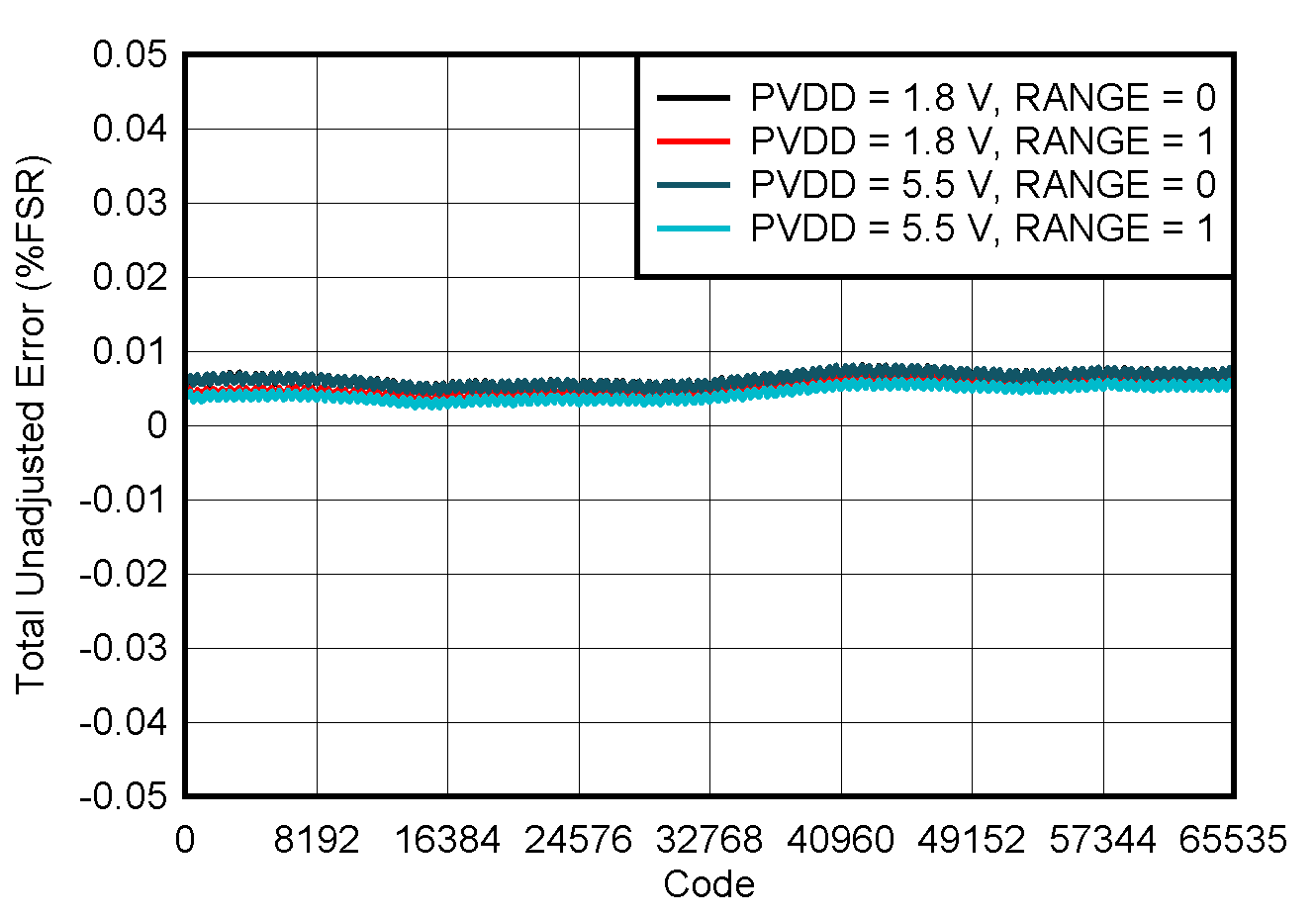

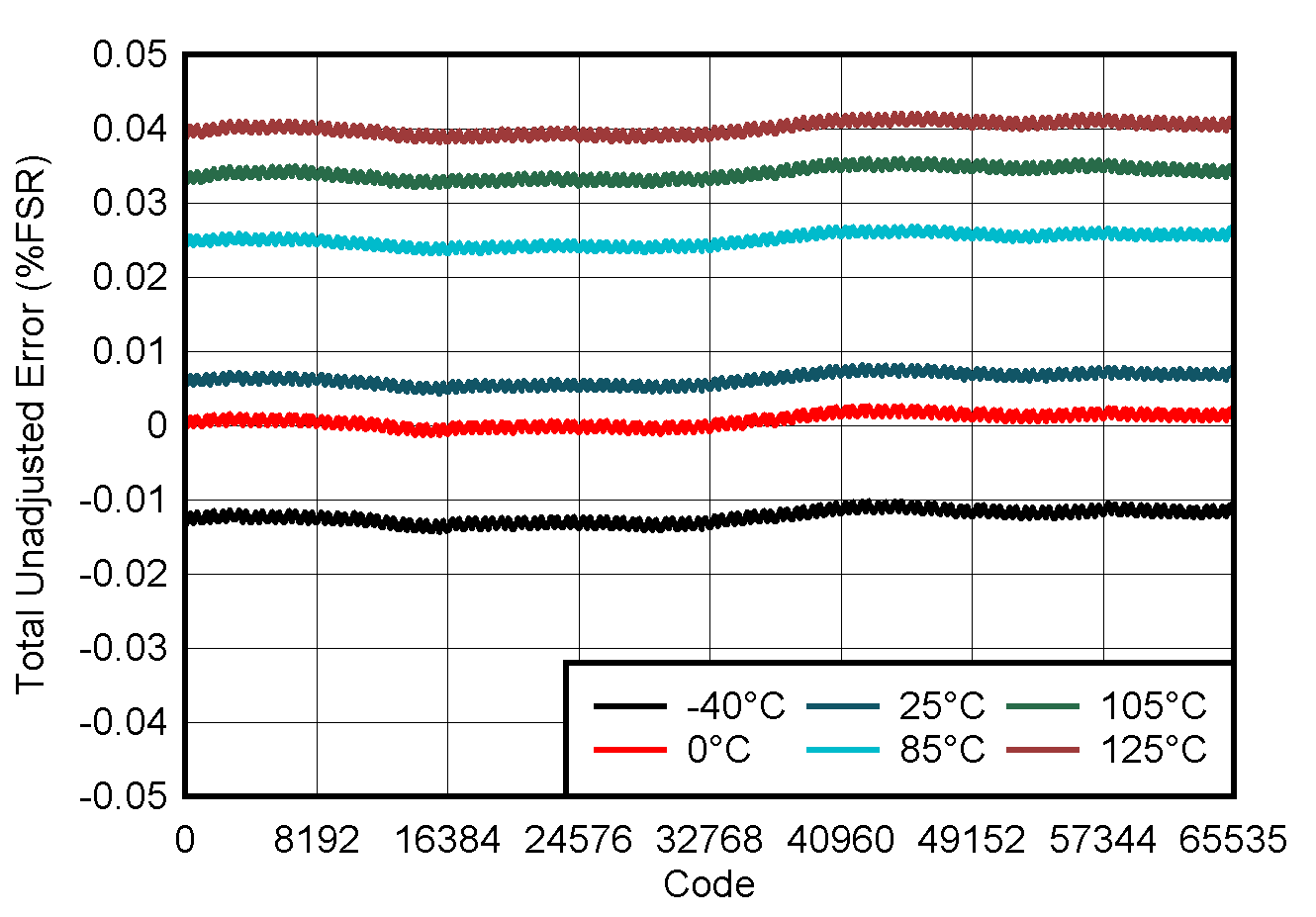

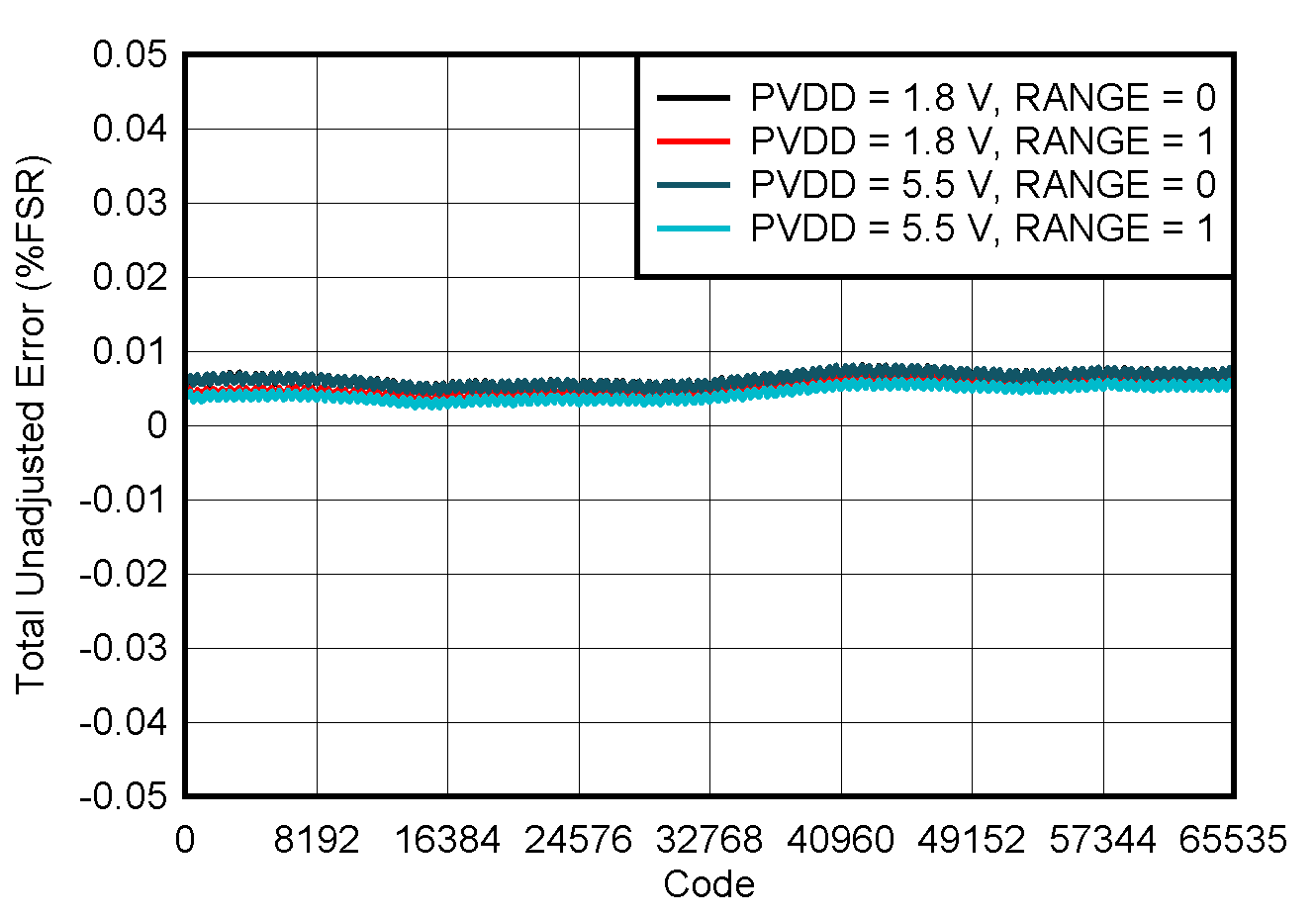

TUE vs Digital Input Code

Figure 6-9 DAC

TUE vs Digital Input Code Figure 6-11 MIN

and MAX DAC TUE vs Temperature

Figure 6-11 MIN

and MAX DAC TUE vs Temperature Figure 6-13 DAC

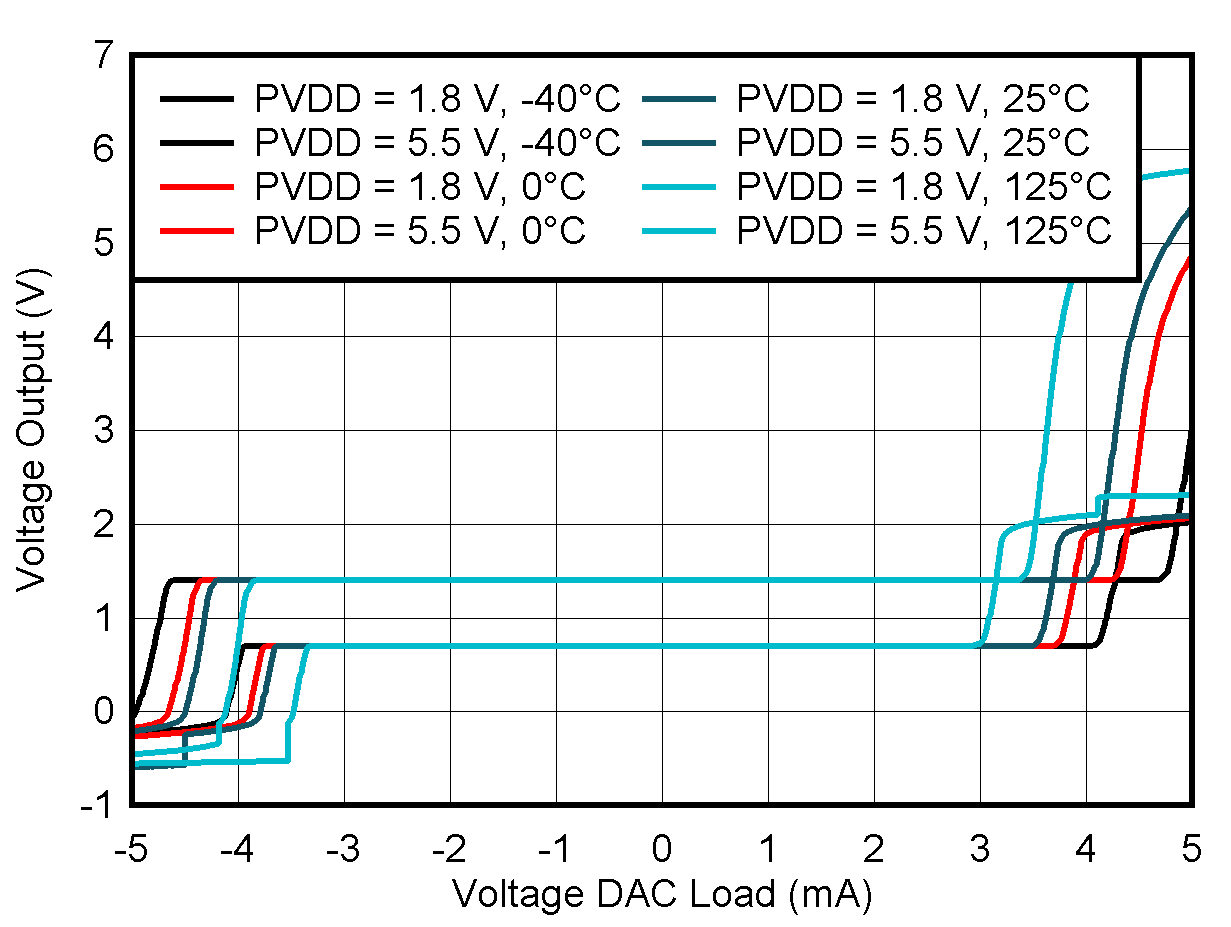

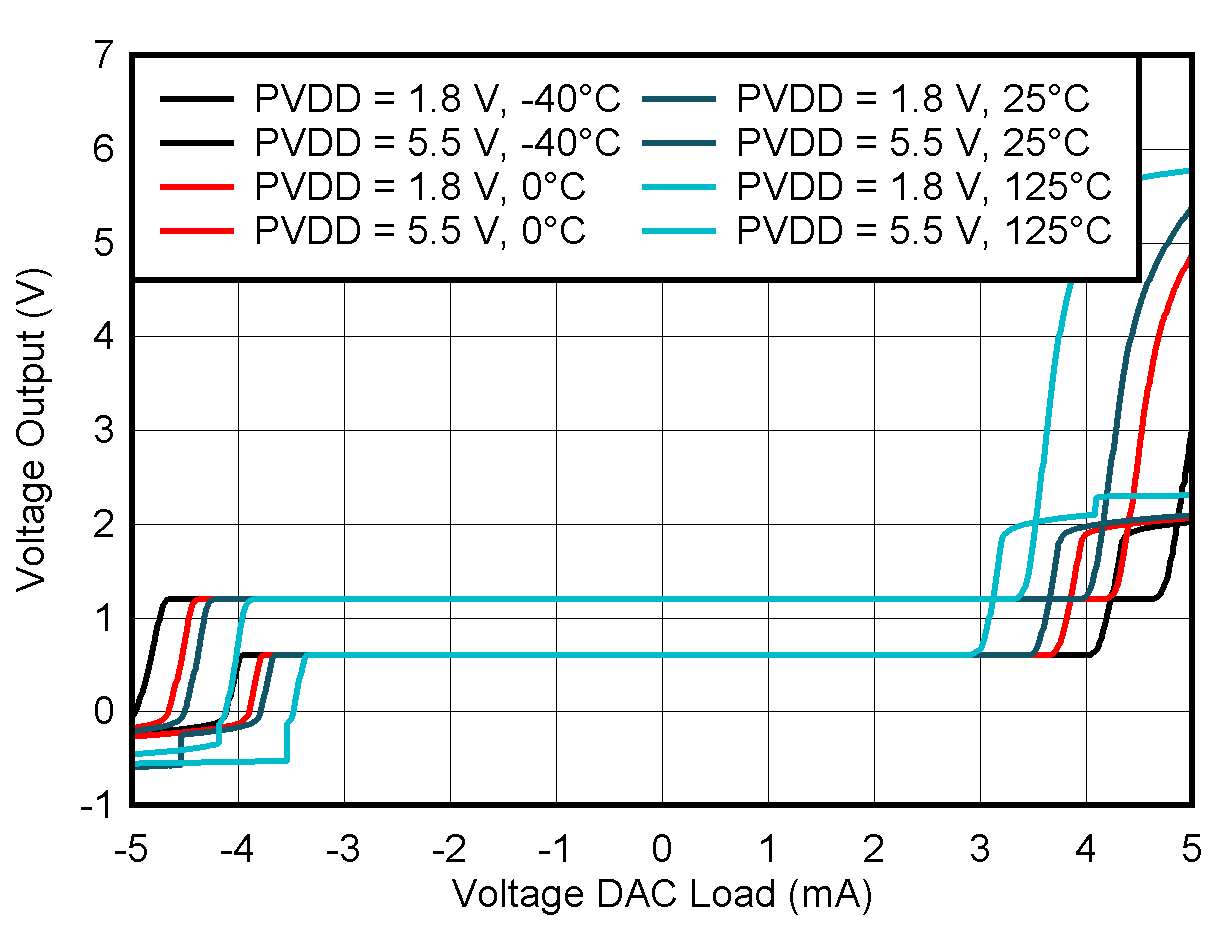

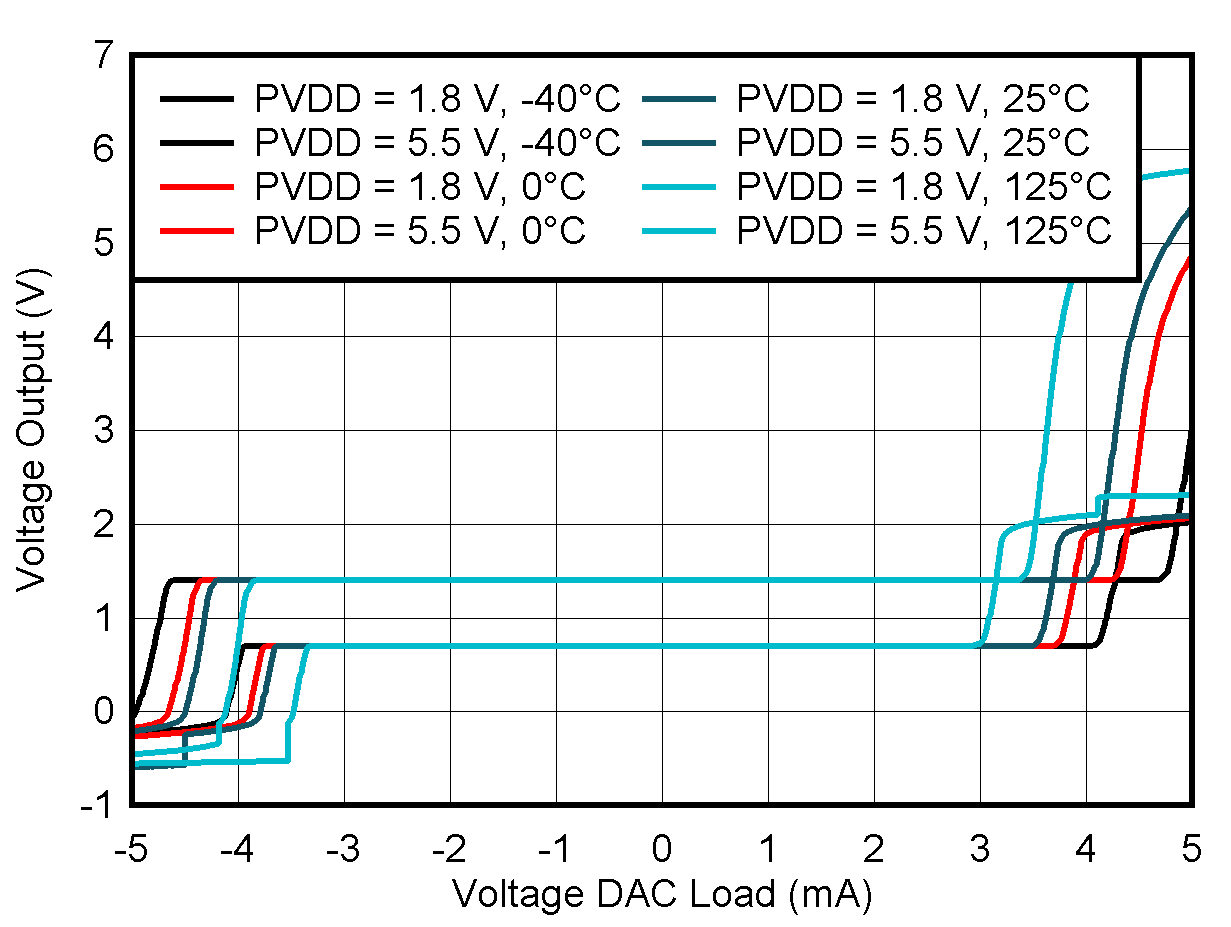

Source and Sink Current Capability

Figure 6-13 DAC

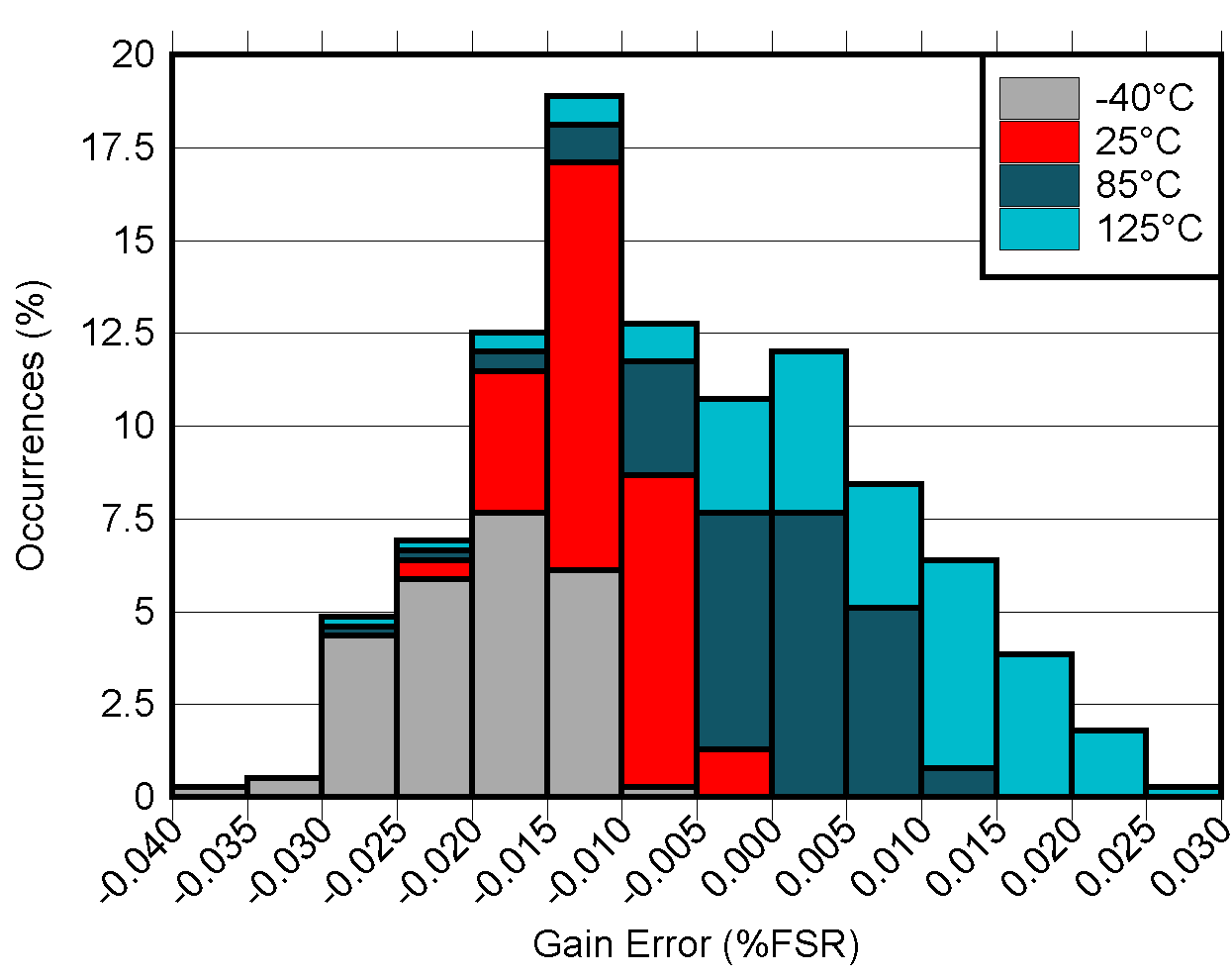

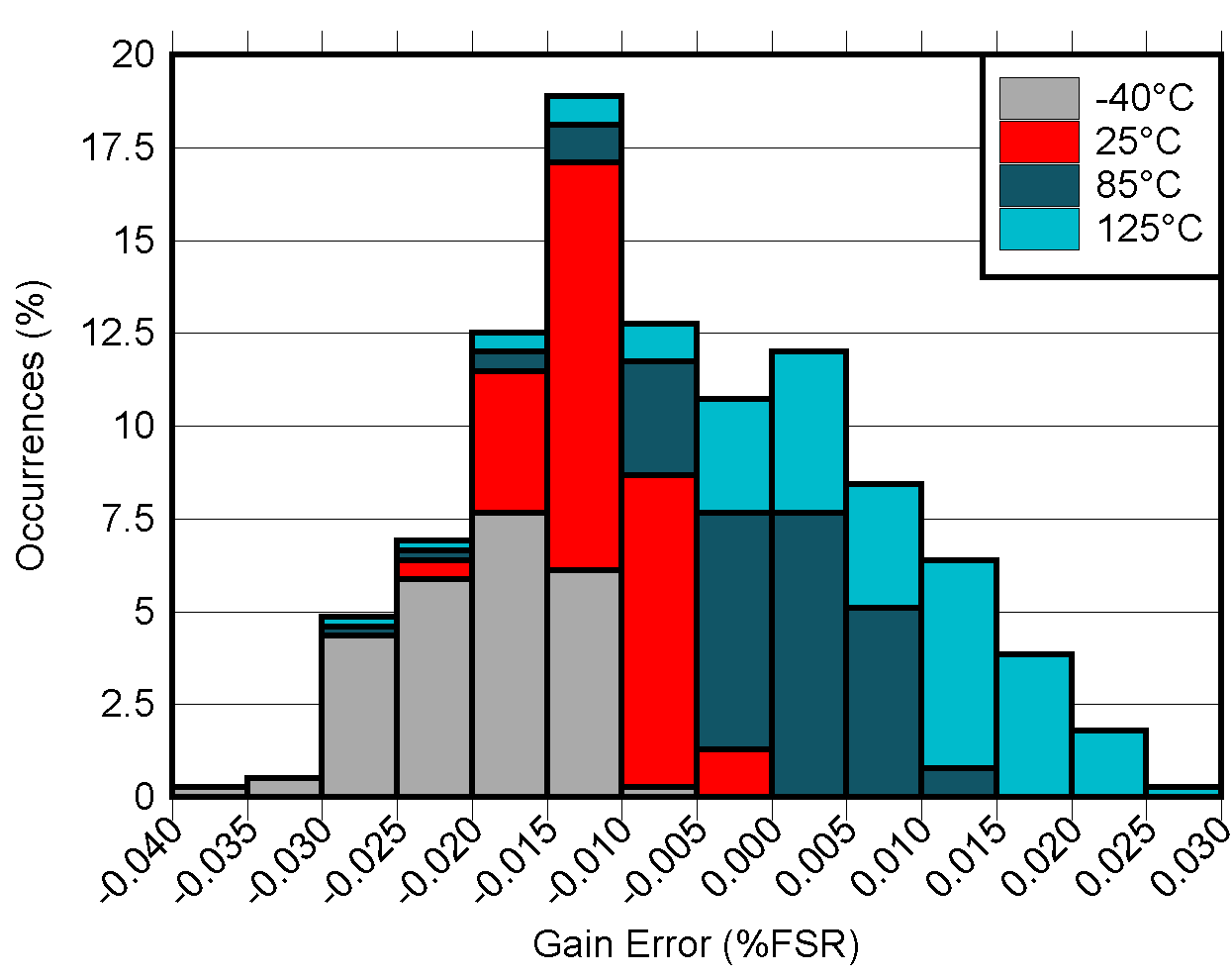

Source and Sink Current Capability Figure 6-15 DAC Gain Error vs Temperature

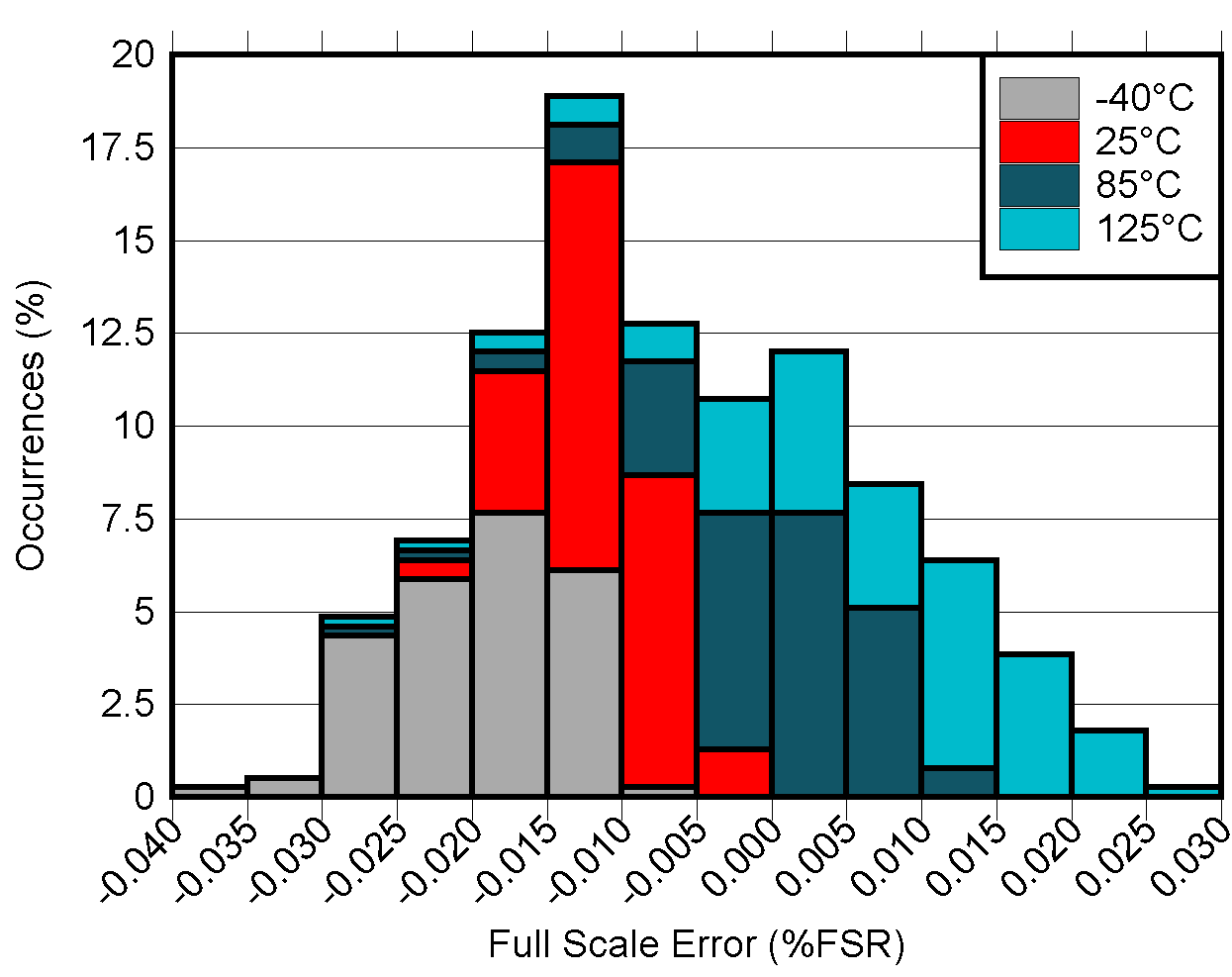

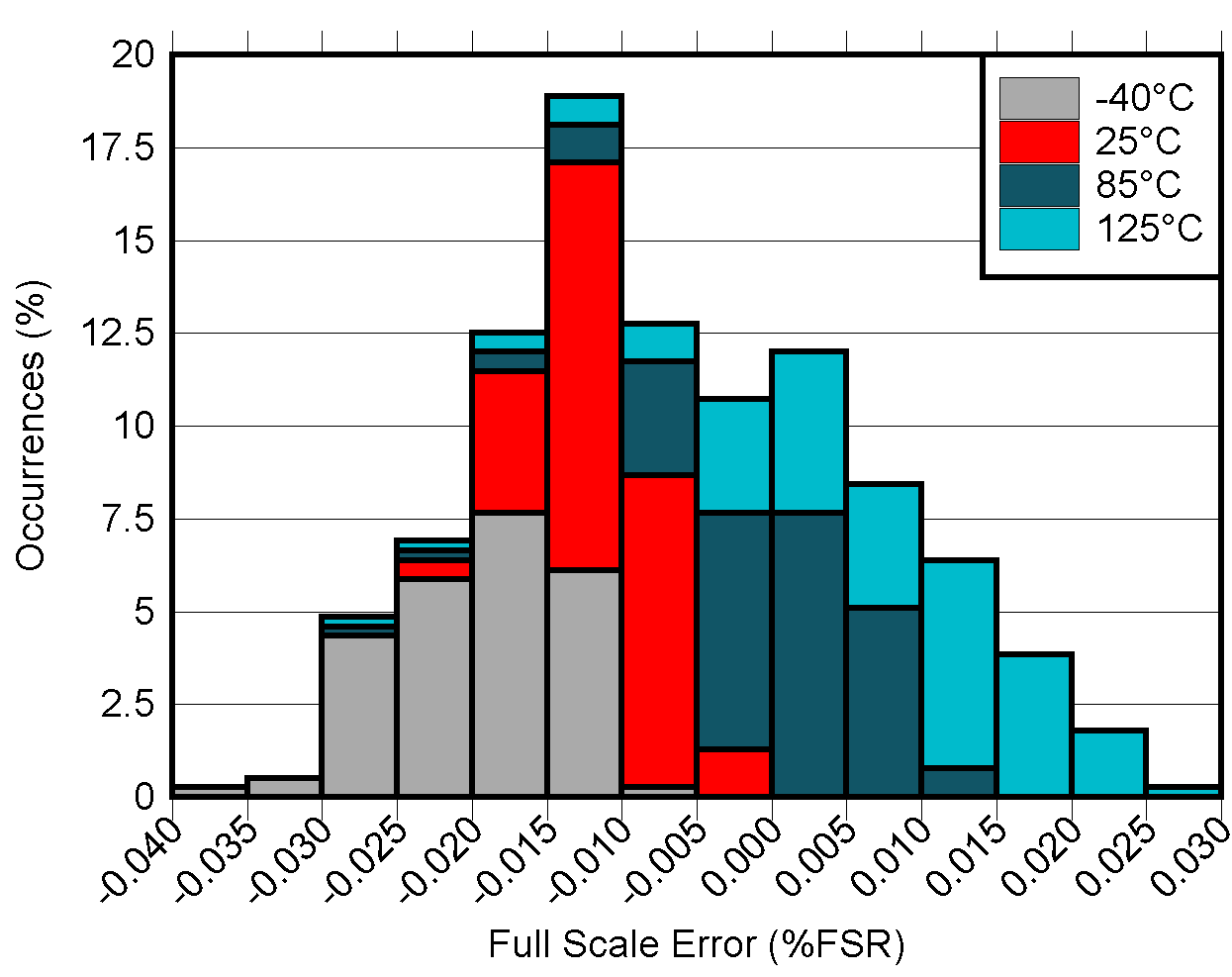

Figure 6-15 DAC Gain Error vs Temperature Figure 6-17 DAC Full Scale Error vs Temperature

Figure 6-17 DAC Full Scale Error vs Temperature Figure 6-19 DAC

Output Noise, 0.1 Hz to 10 Hz

Figure 6-19 DAC

Output Noise, 0.1 Hz to 10 Hz Figure 6-21 DAC

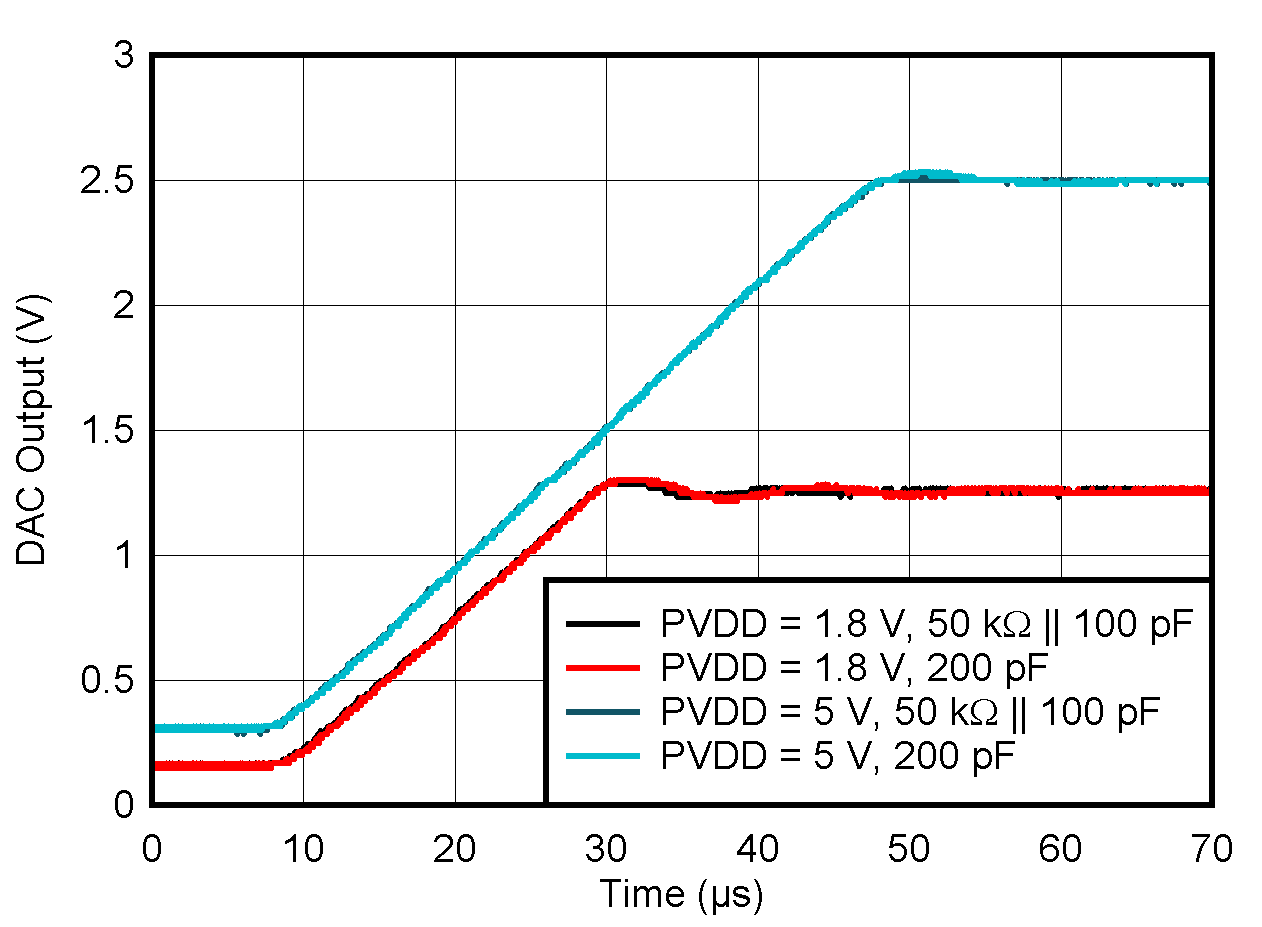

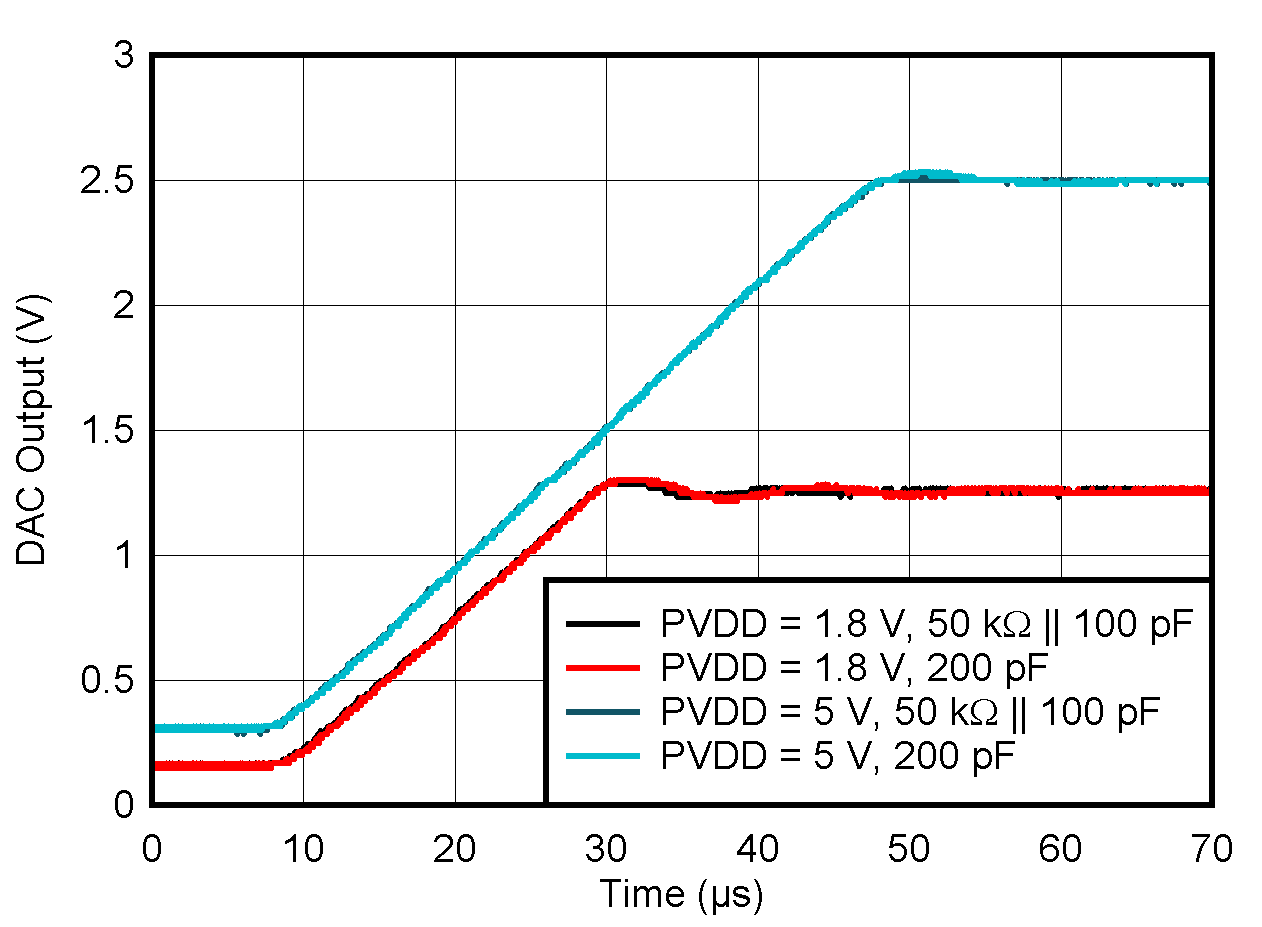

Settling Time vs Load (Rising Voltage Step)

Figure 6-21 DAC

Settling Time vs Load (Rising Voltage Step) Figure 6-23 DAC

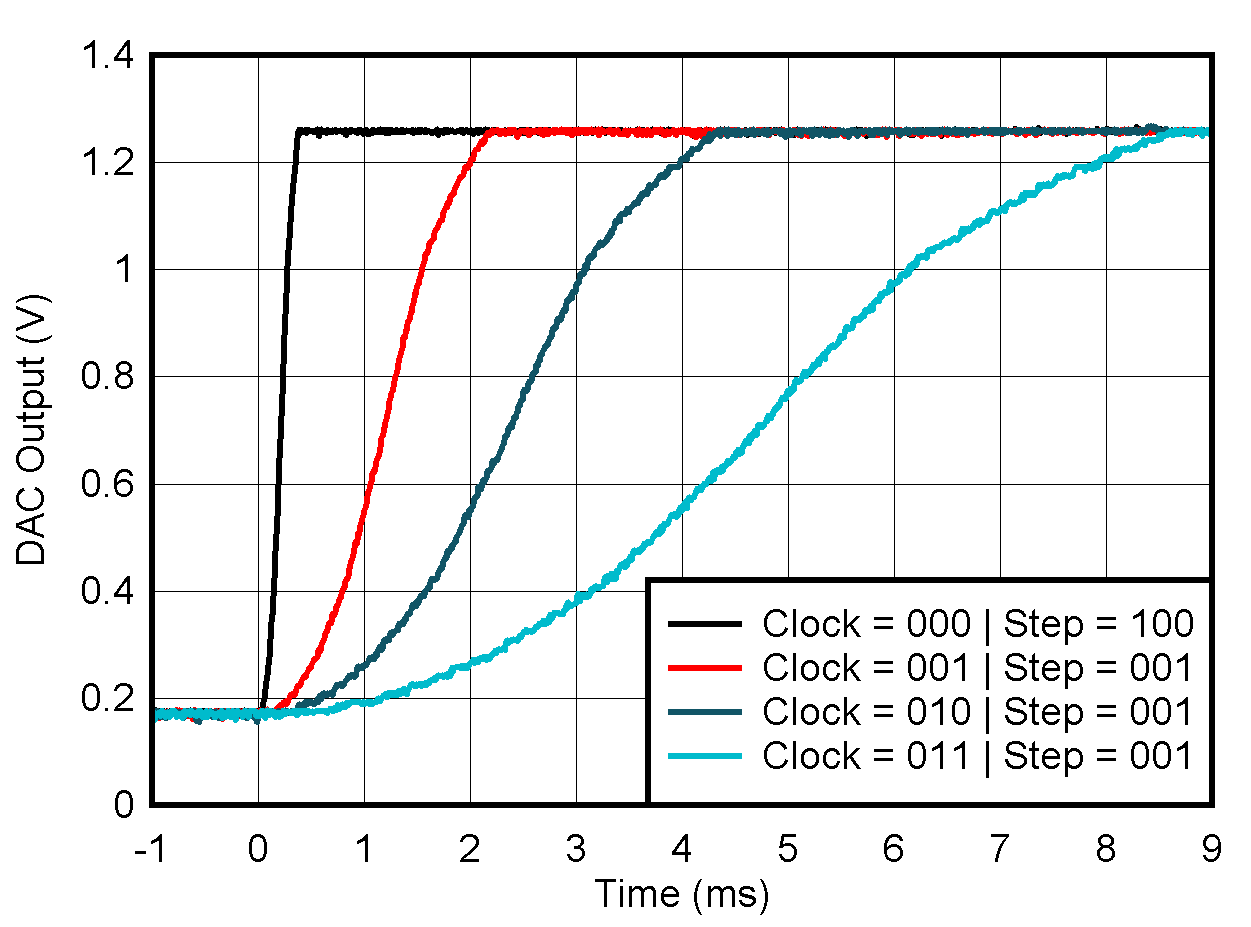

Settling Time With Linear Slew Rate Control

Figure 6-23 DAC

Settling Time With Linear Slew Rate Control Figure 6-25 DAC

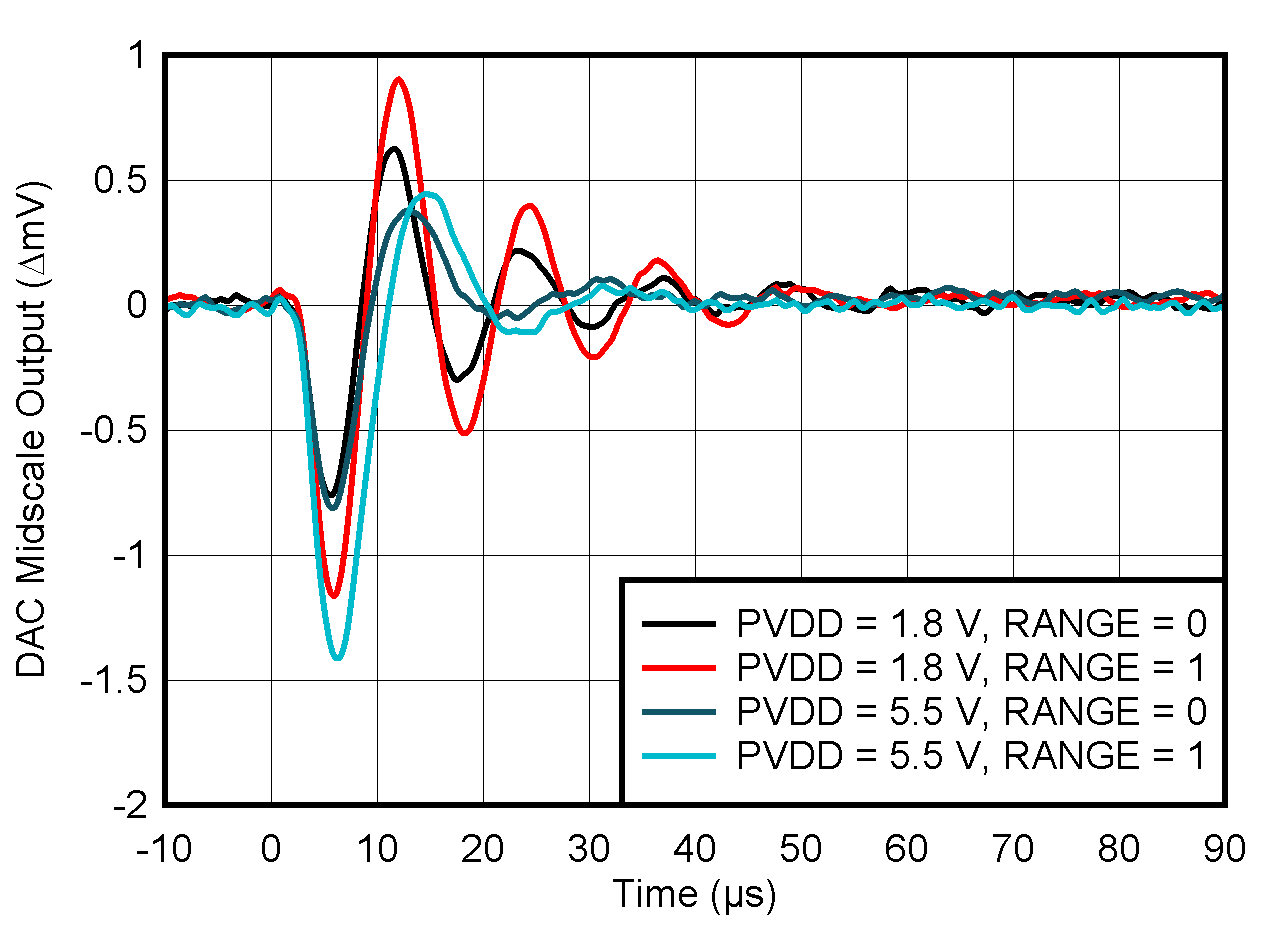

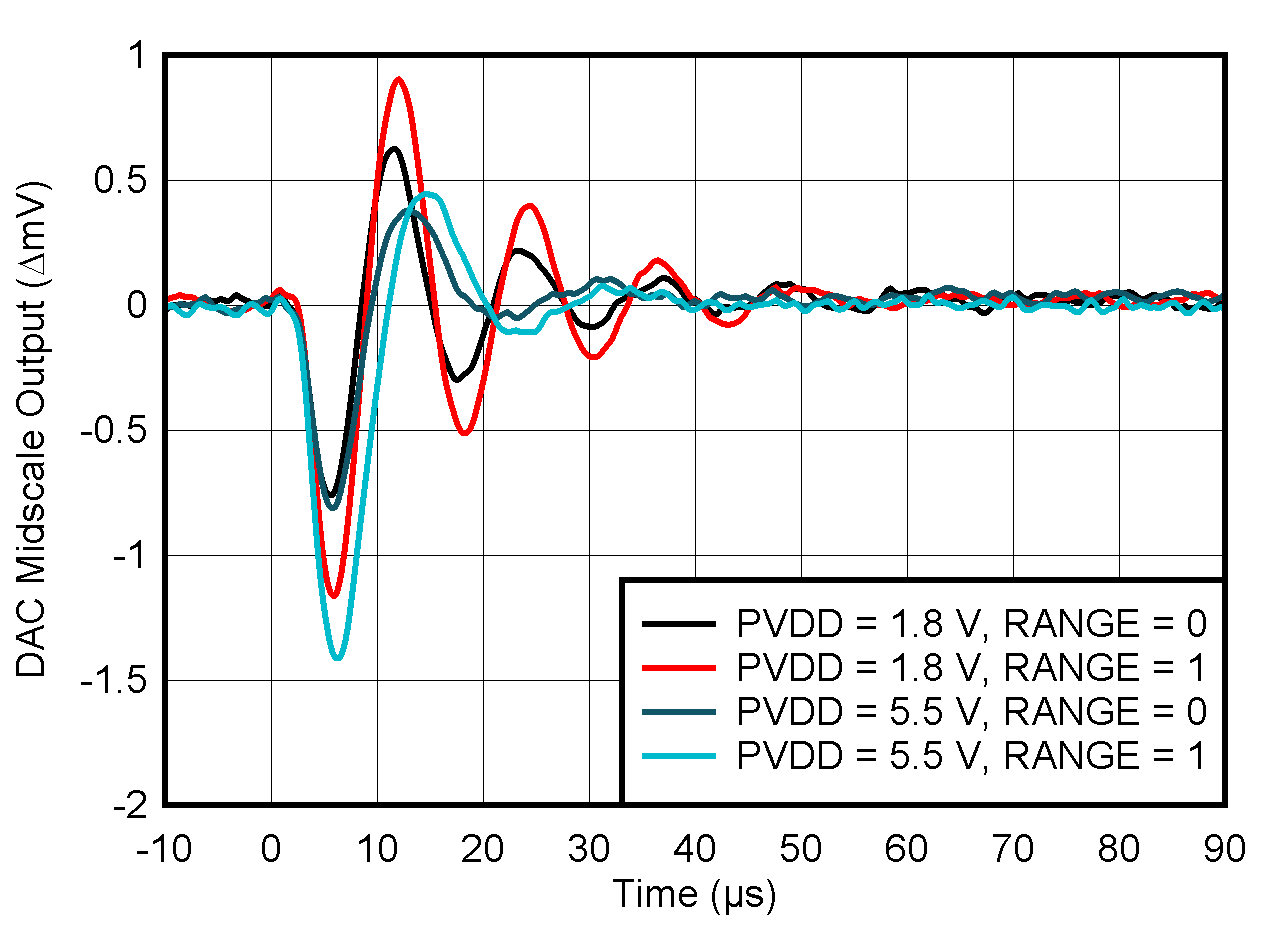

Glitch Impulse Rising Edge

Figure 6-25 DAC

Glitch Impulse Rising Edge Figure 6-27 DAC

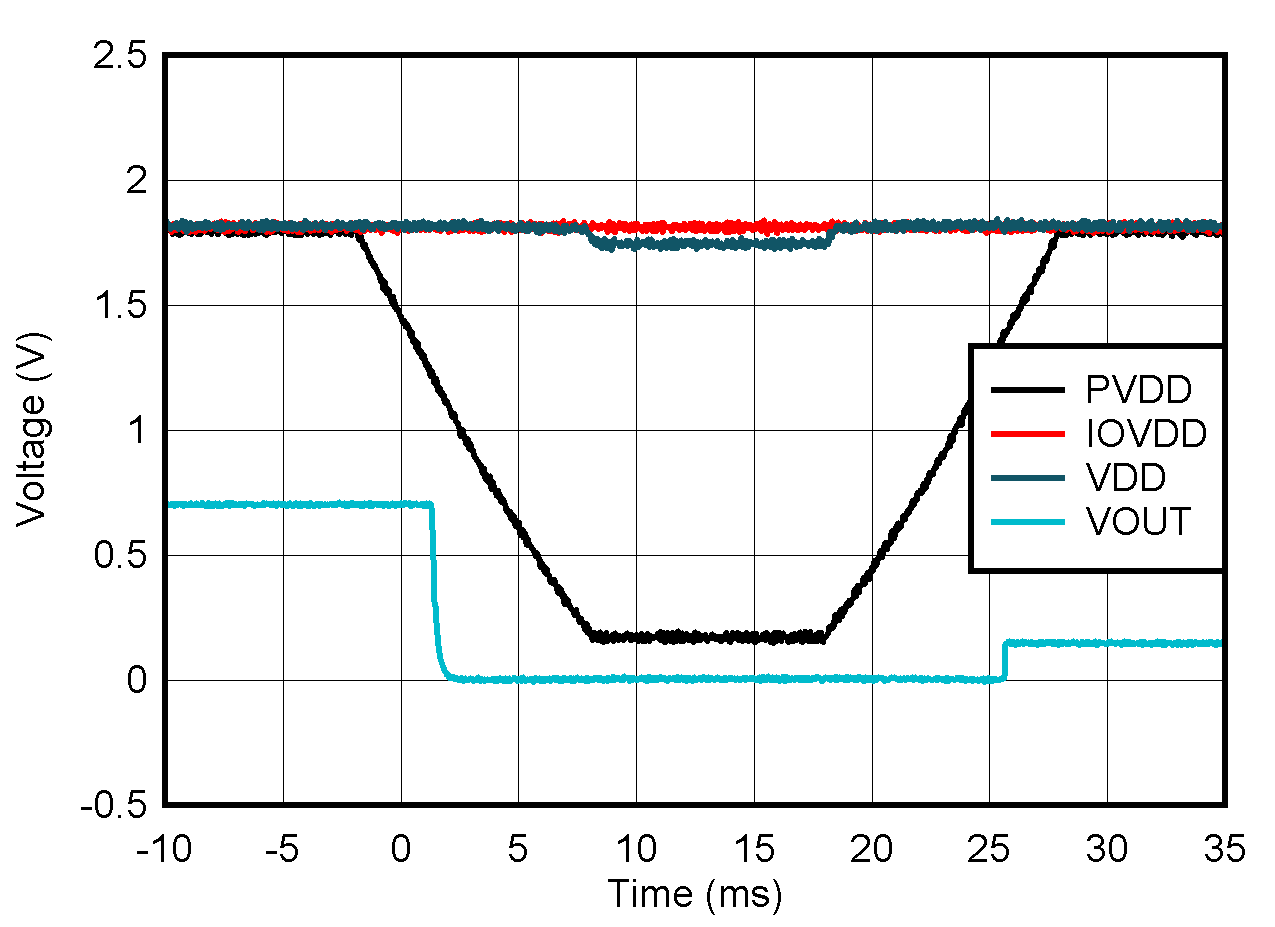

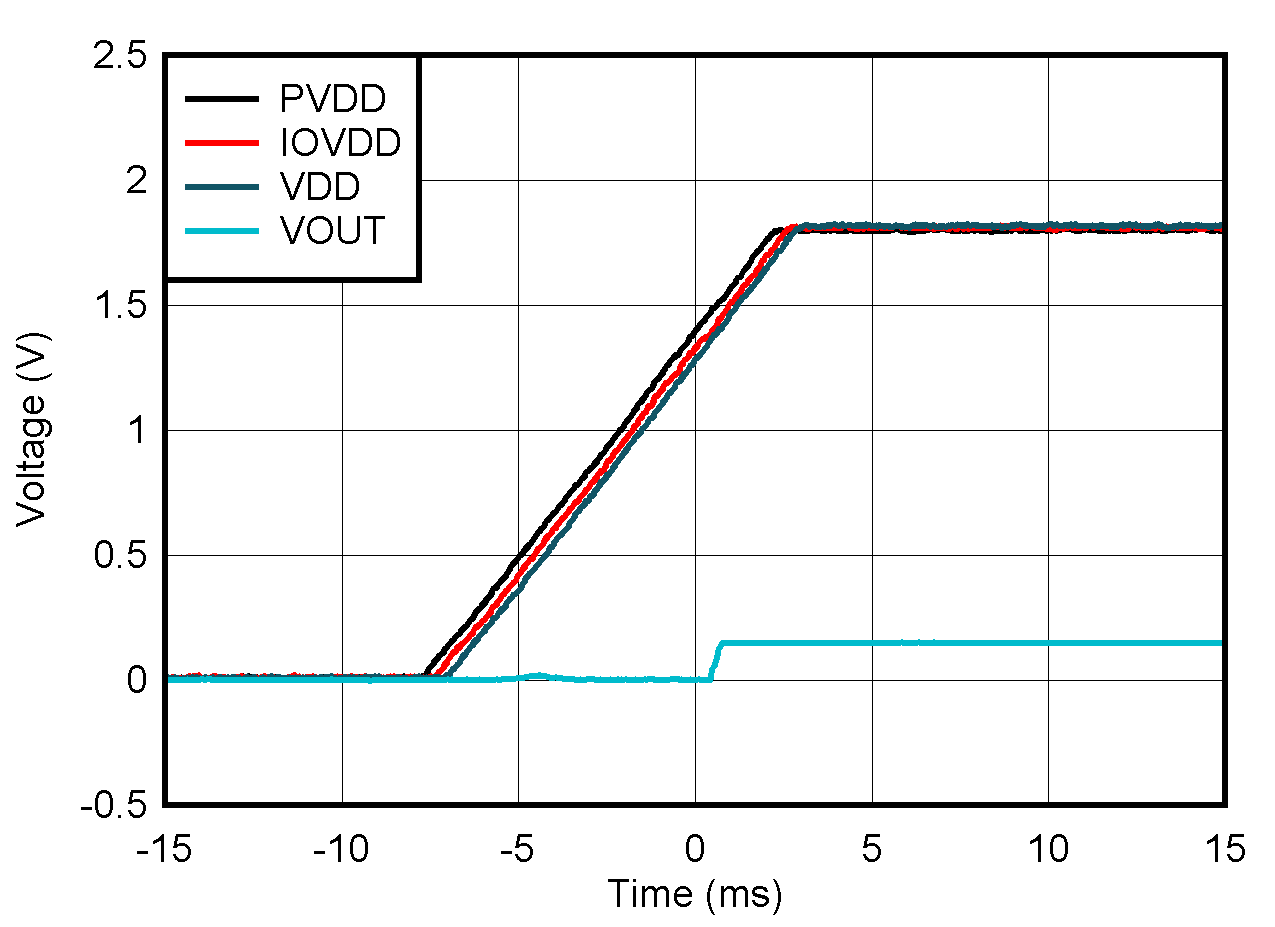

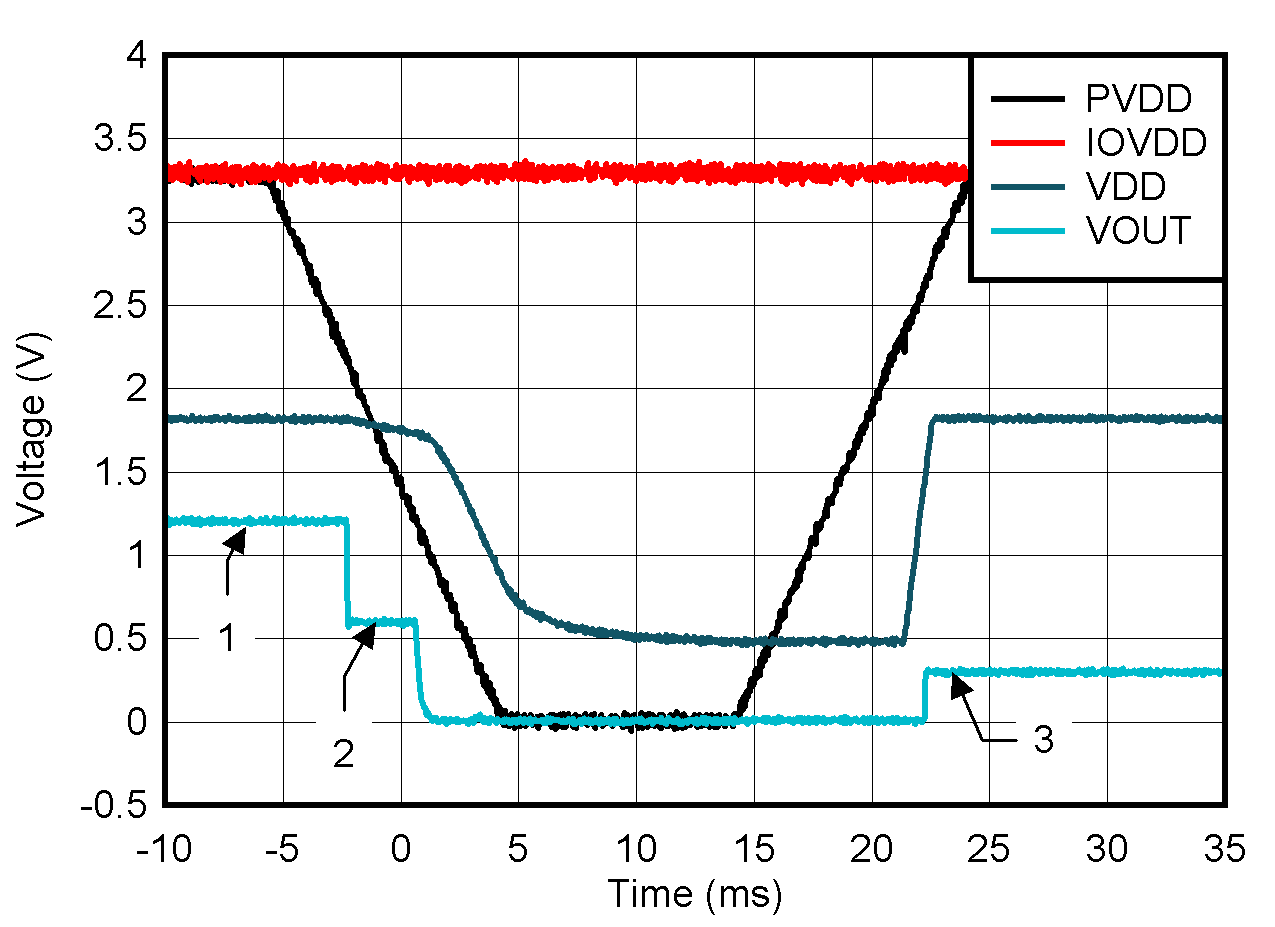

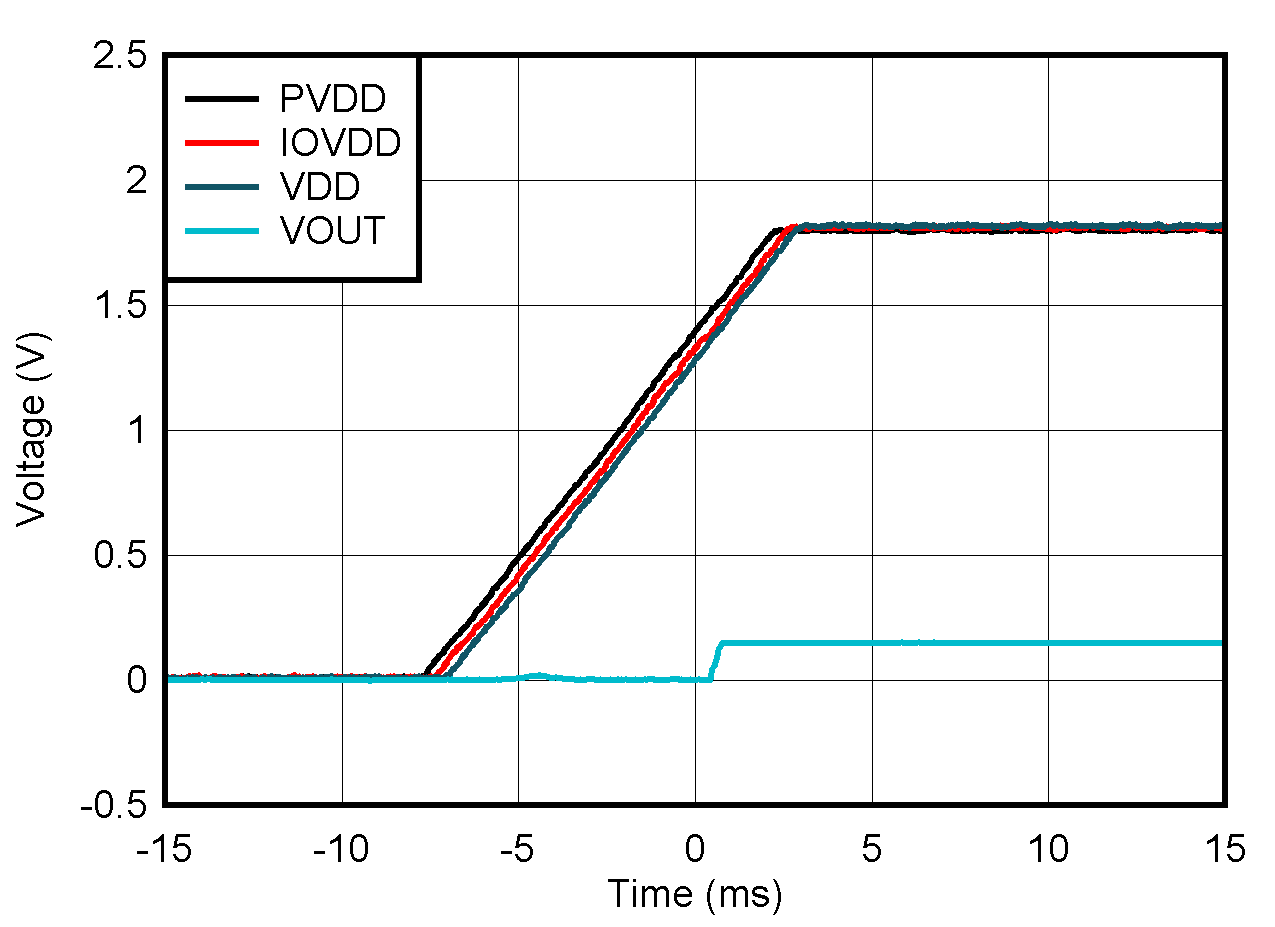

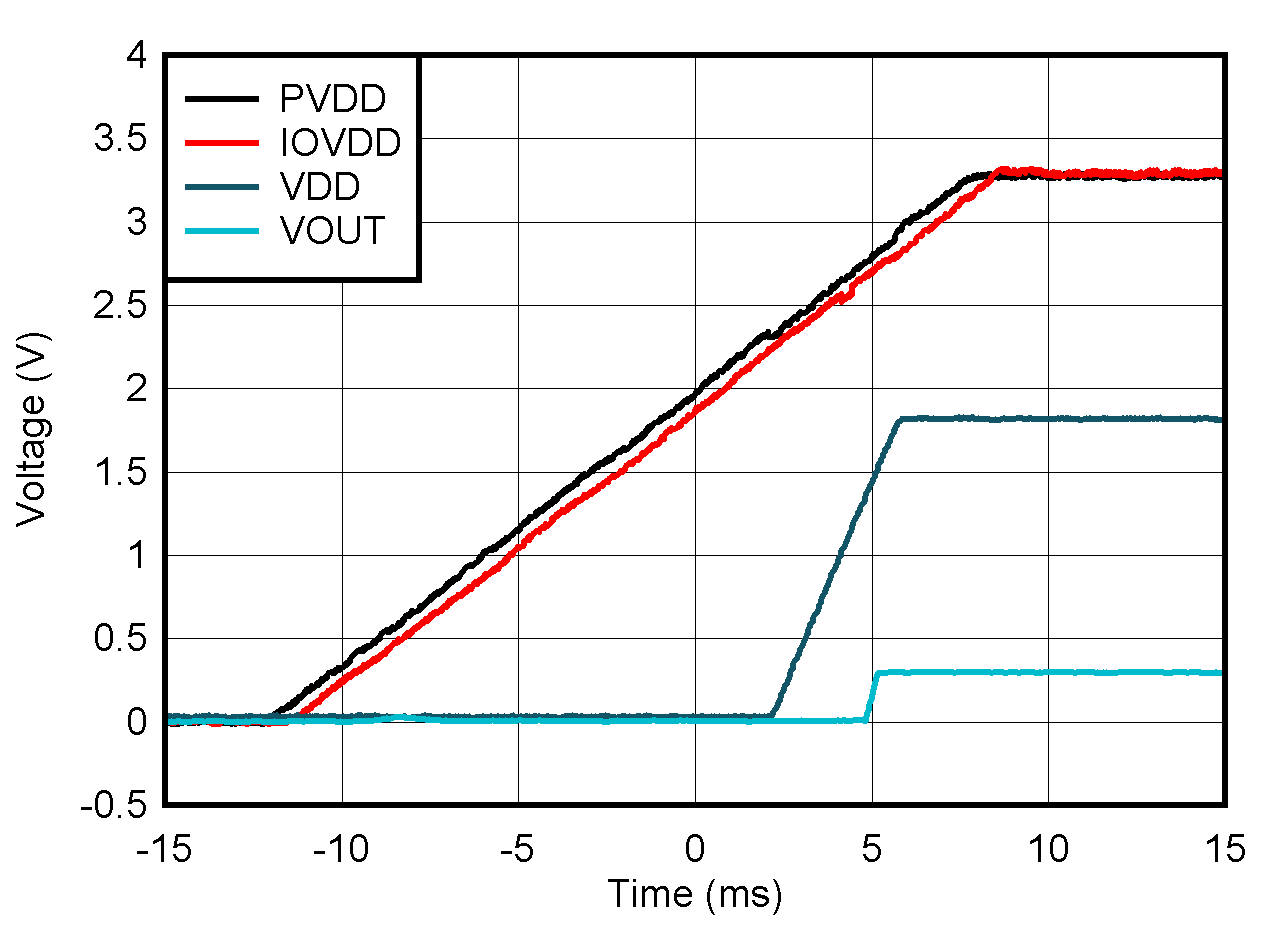

Supply Power On, PVDD = 1.8 V

Figure 6-27 DAC

Supply Power On, PVDD = 1.8 V

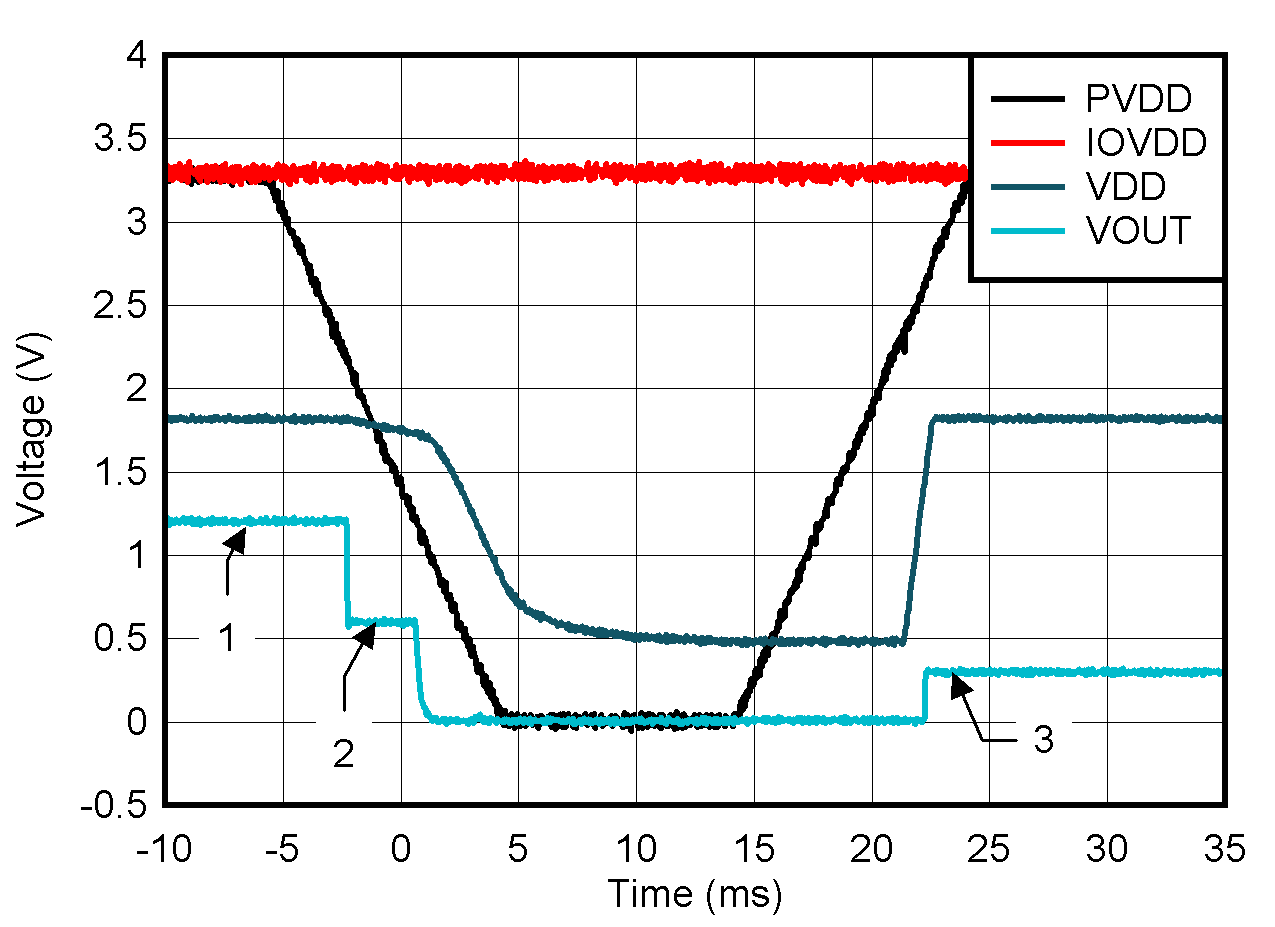

| 1: 0.4-V to 2-V range,

midcode |

3: 0.3-V to 2.2-V

range, |

| 2: 0.2-V to 1-V

range, midcode |

zero code |

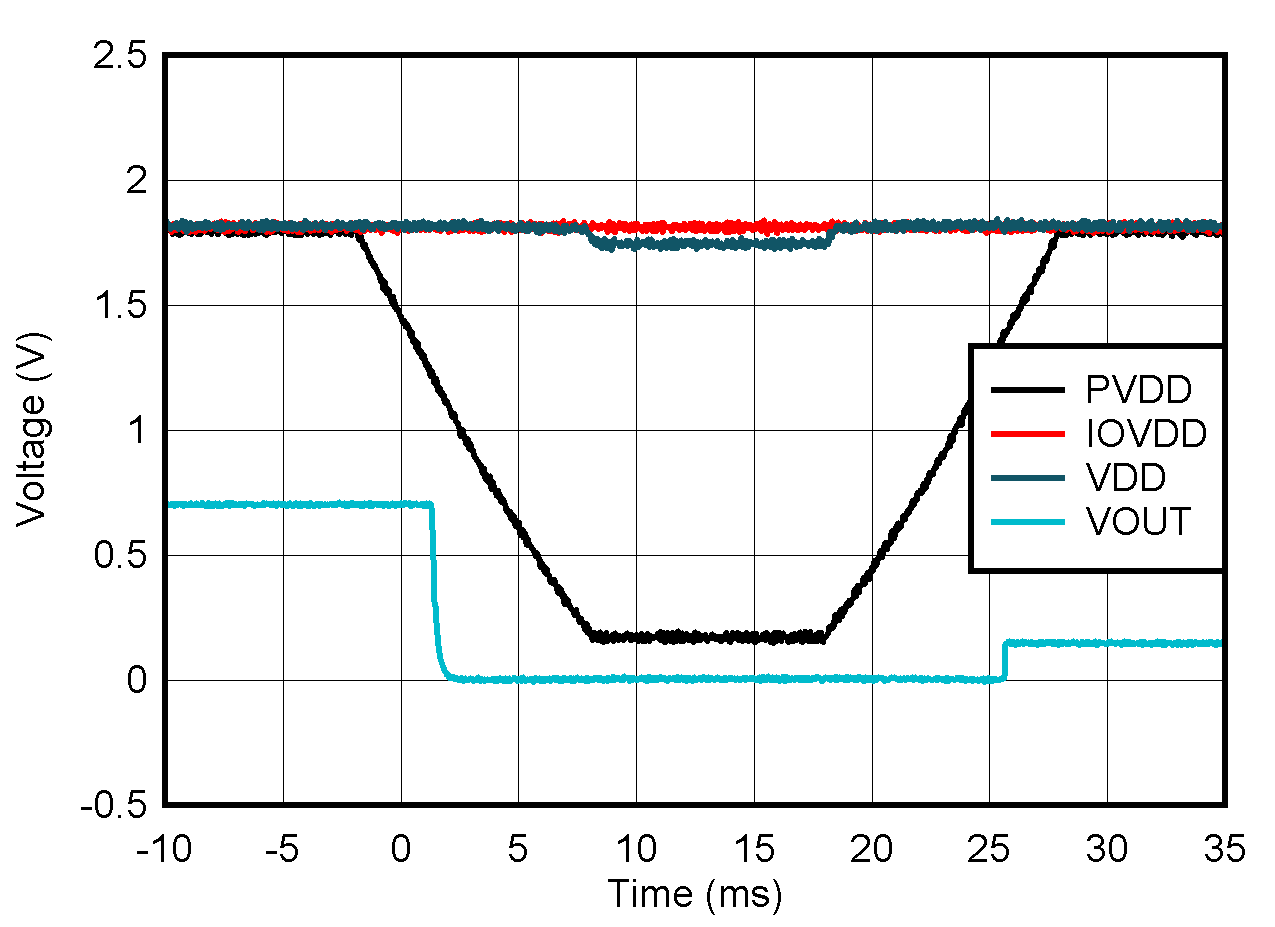

Figure 6-29 DAC

PVDD Supply Collapse Response, RANGE = 1

| 0.15-V

to 1.25-V range, midcode |

|

|

|

|

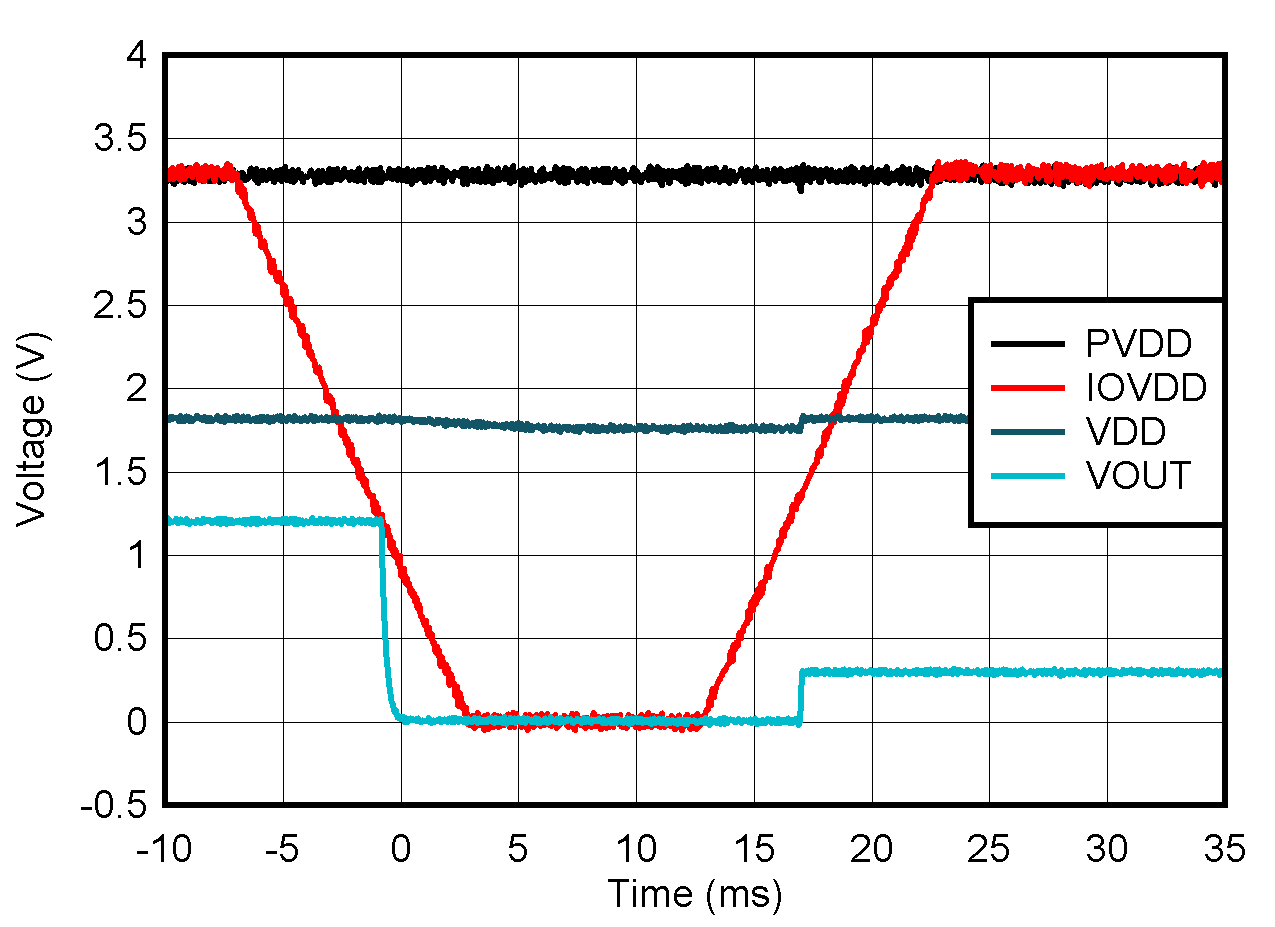

Figure 6-31 DAC

VDD Supply Collapse Response,

RANGE = 0 Figure 6-33 DAC

Output Voltage Long-Term Stability

Figure 6-33 DAC

Output Voltage Long-Term Stability Figure 6-4 DAC

DNL vs Digital Input Code

Figure 6-4 DAC

DNL vs Digital Input Code Figure 6-6 DAC

INL vs Digital Input Code

Figure 6-6 DAC

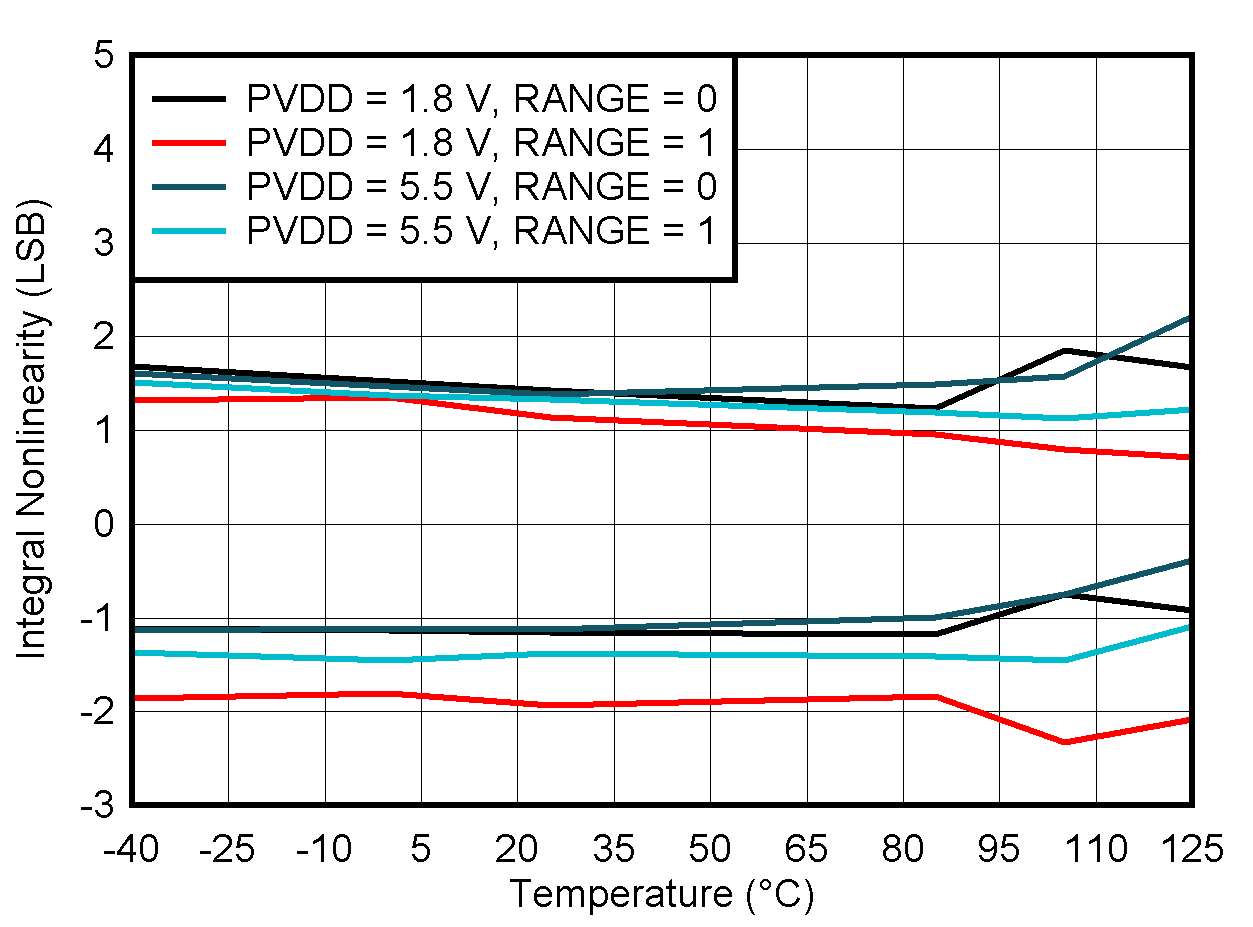

INL vs Digital Input Code Figure 6-8 MIN

and MAX DAC INL Range vs Temperature

Figure 6-8 MIN

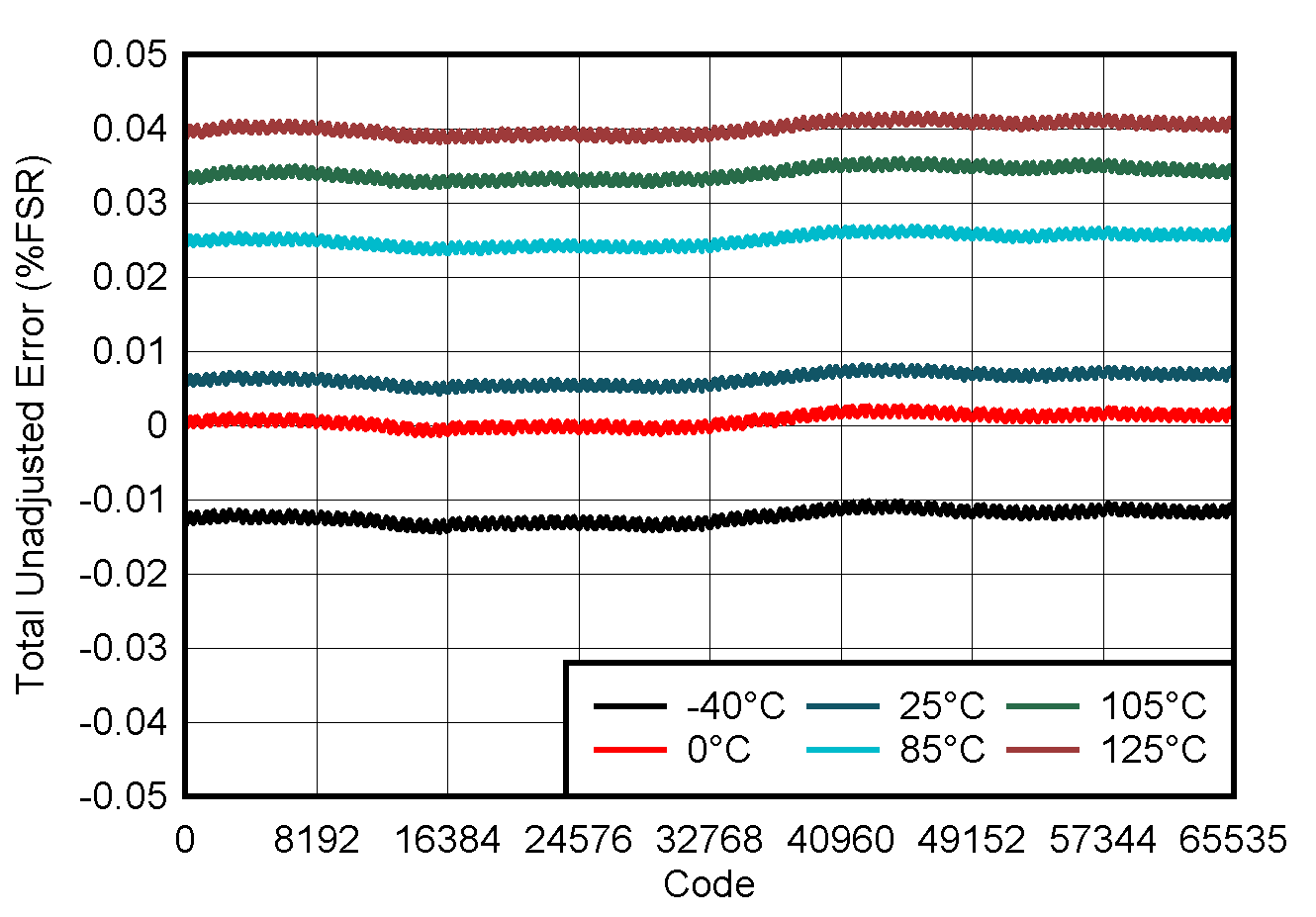

and MAX DAC INL Range vs Temperature Figure 6-10 DAC

TUE vs Digital Input Code

Figure 6-10 DAC

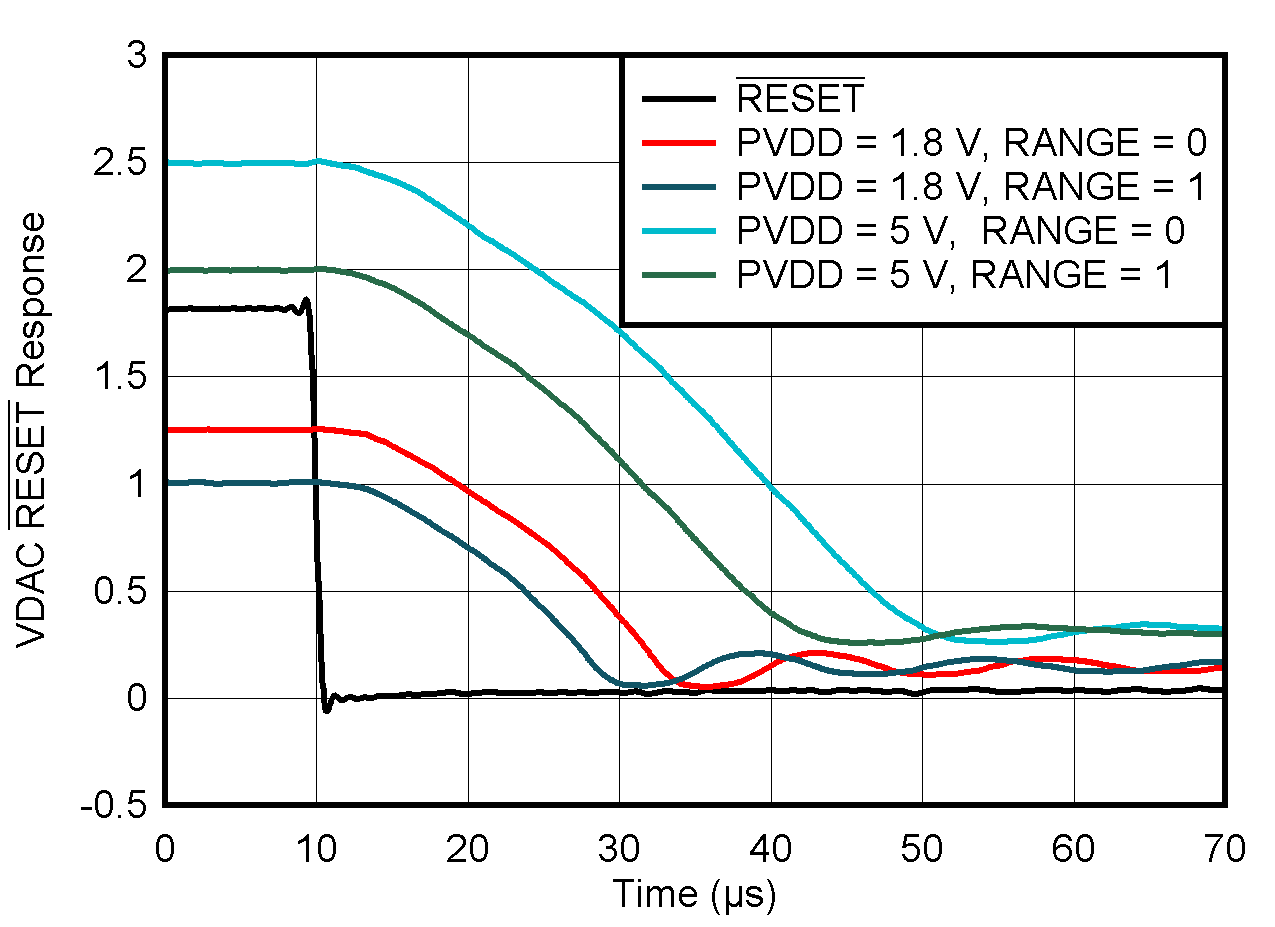

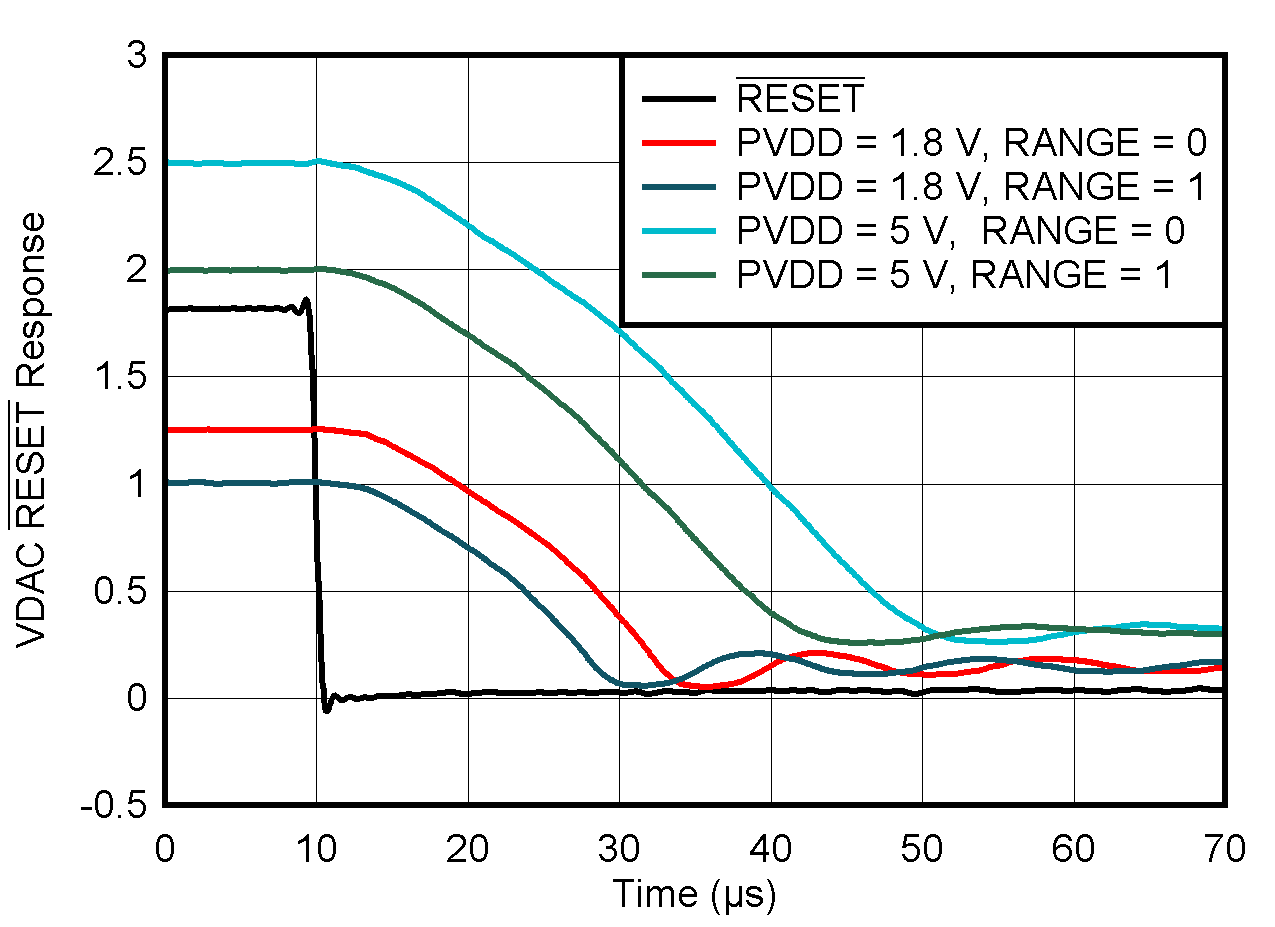

TUE vs Digital Input Code Figure 6-12 DAC

RESET Response

Figure 6-12 DAC

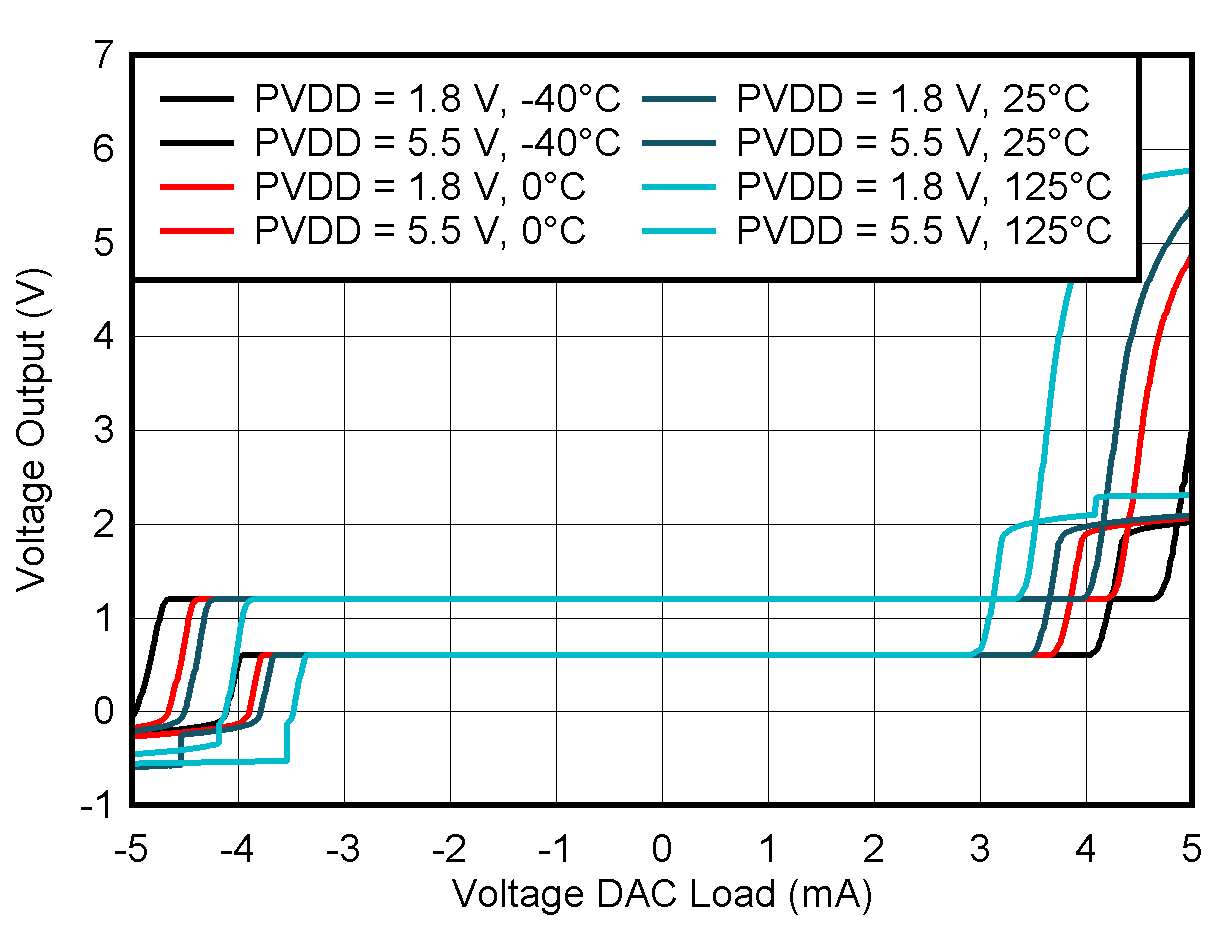

RESET Response Figure 6-14 DAC

Source and Sink Current Capability

Figure 6-14 DAC

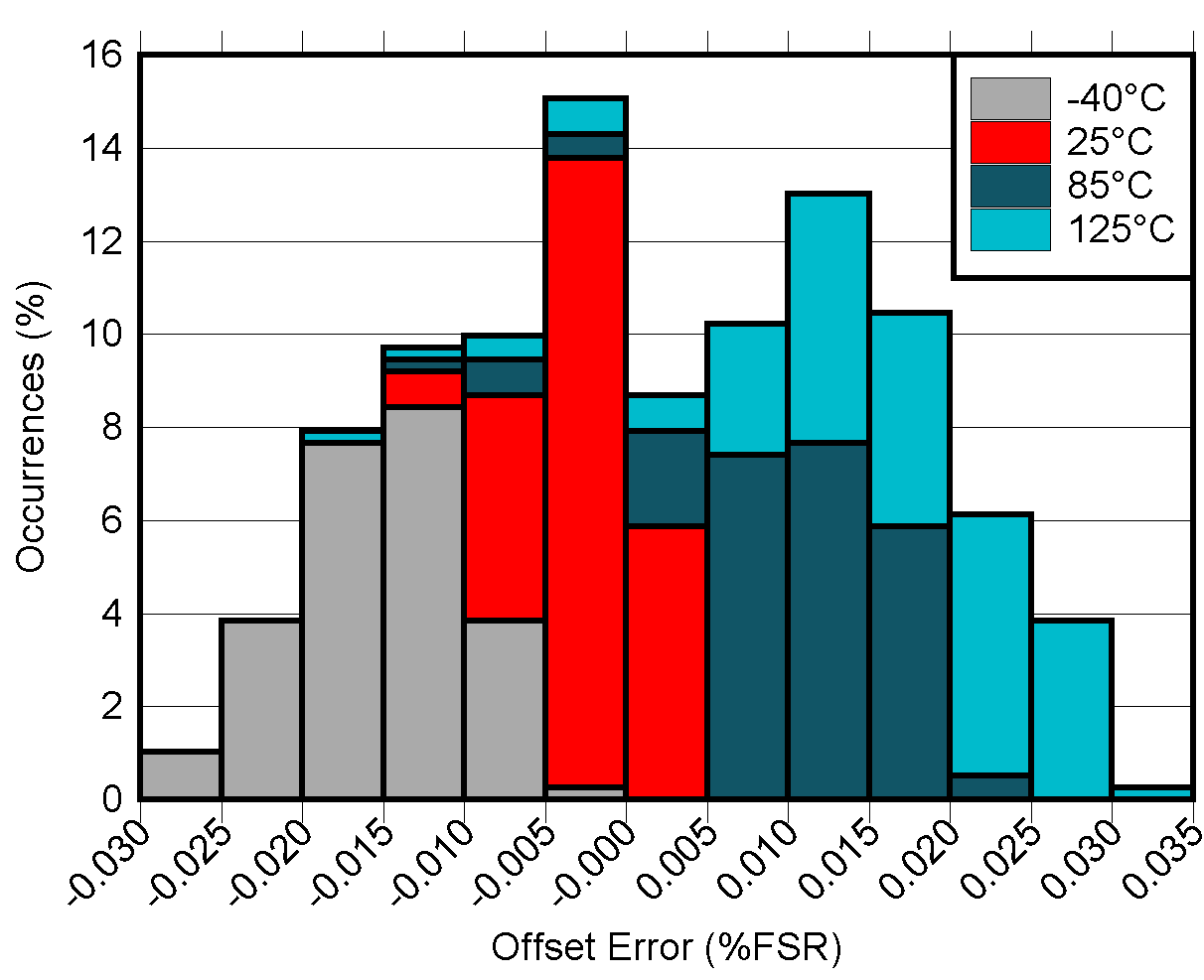

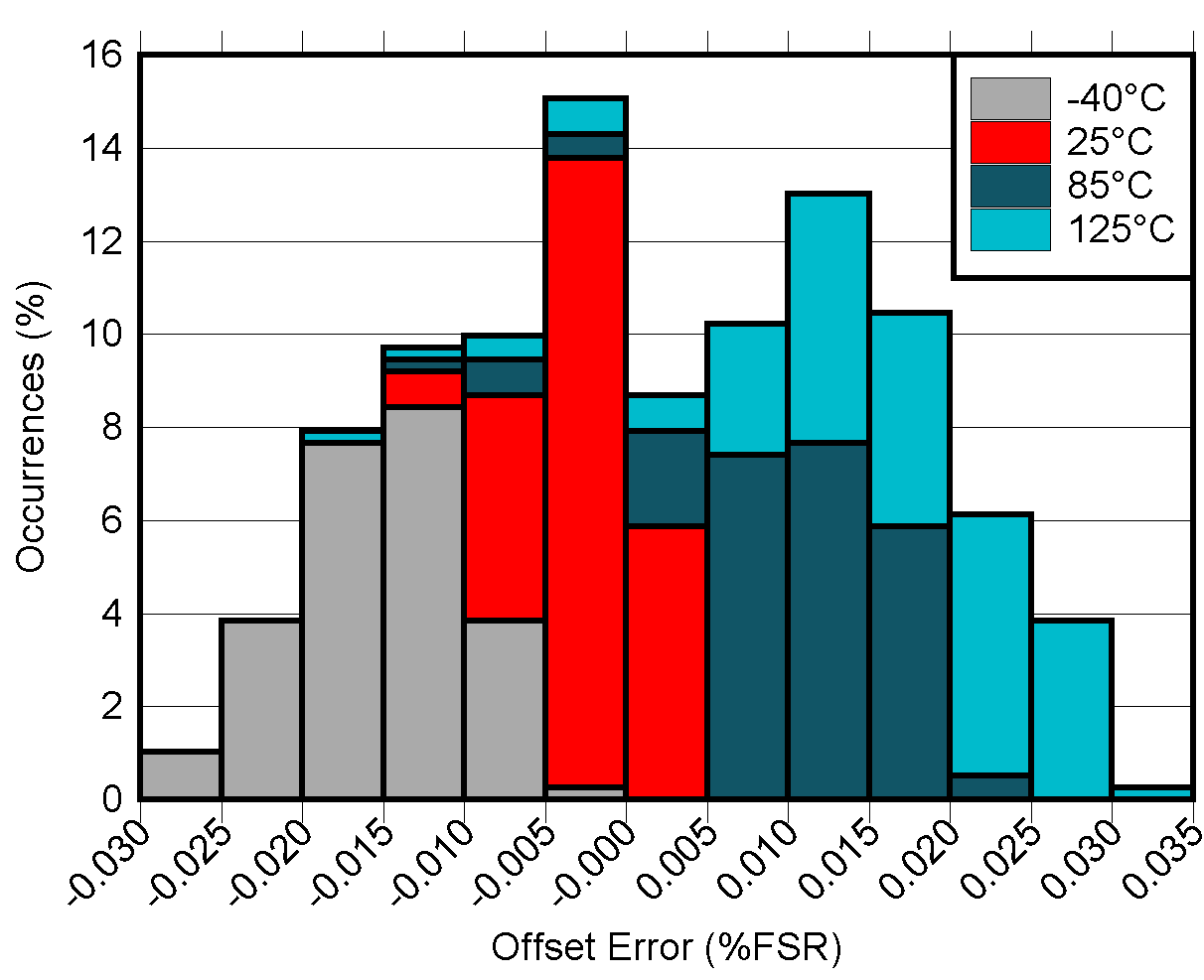

Source and Sink Current Capability Figure 6-16 DAC Offset Error vs Temperature

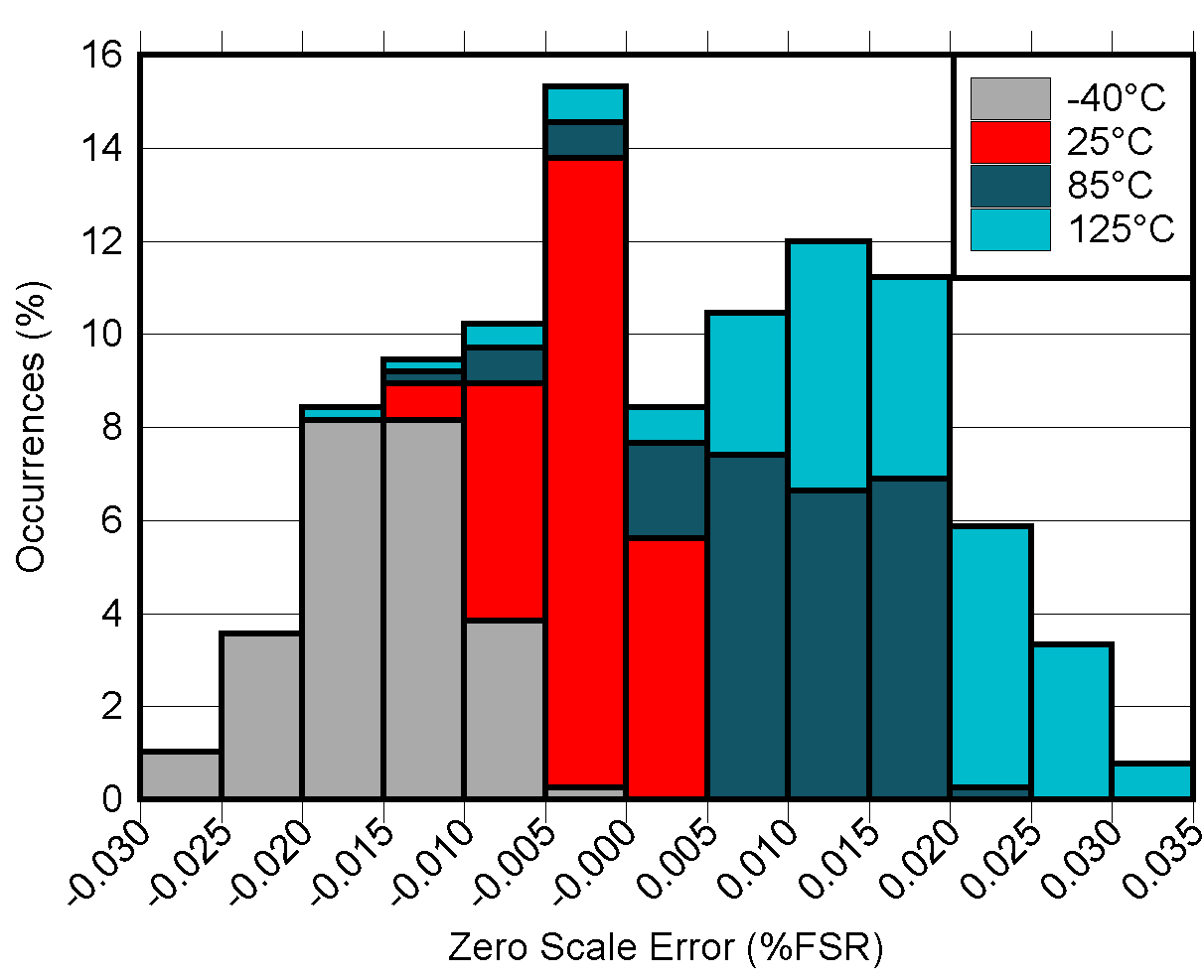

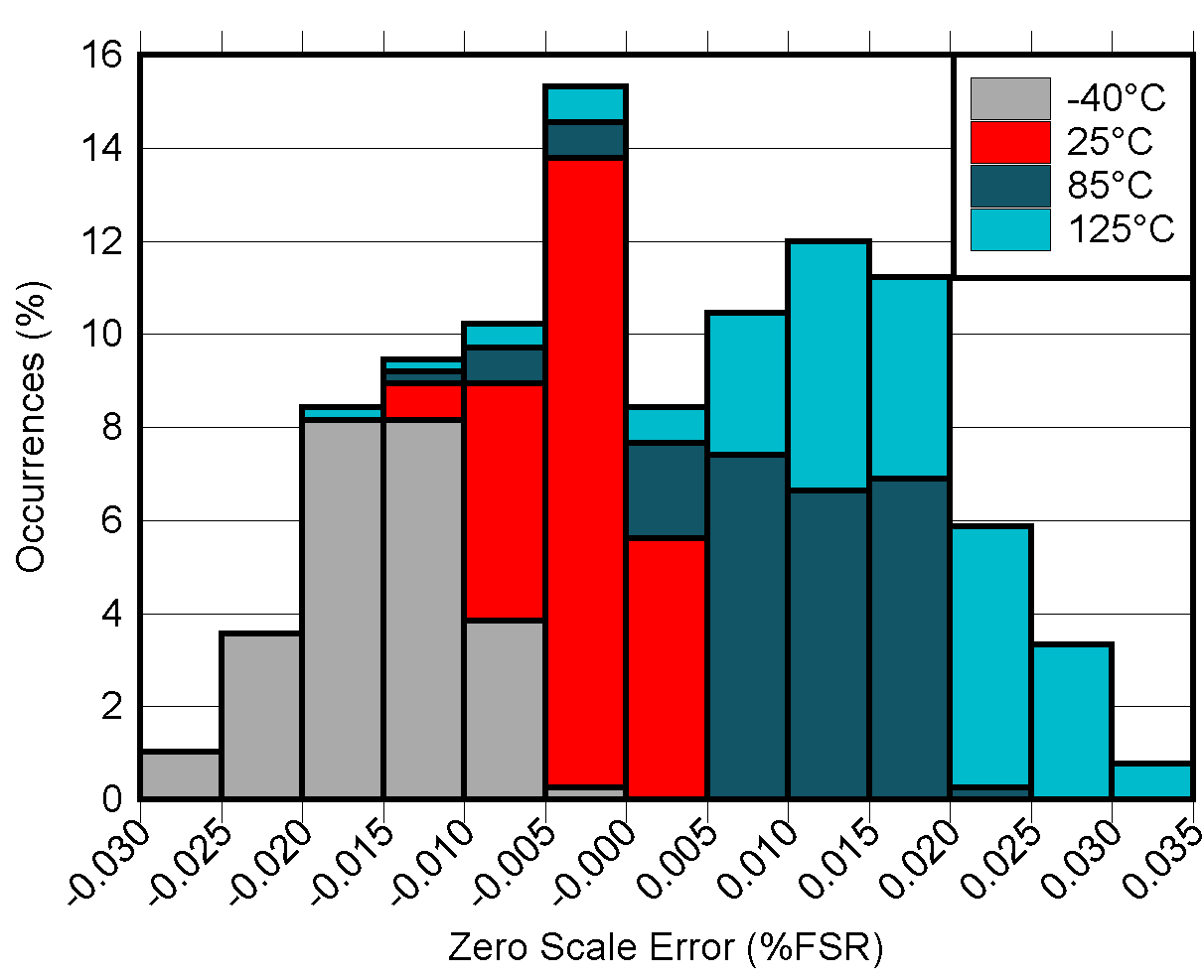

Figure 6-16 DAC Offset Error vs Temperature Figure 6-18 DAC Zero Scale Error vs Temperature

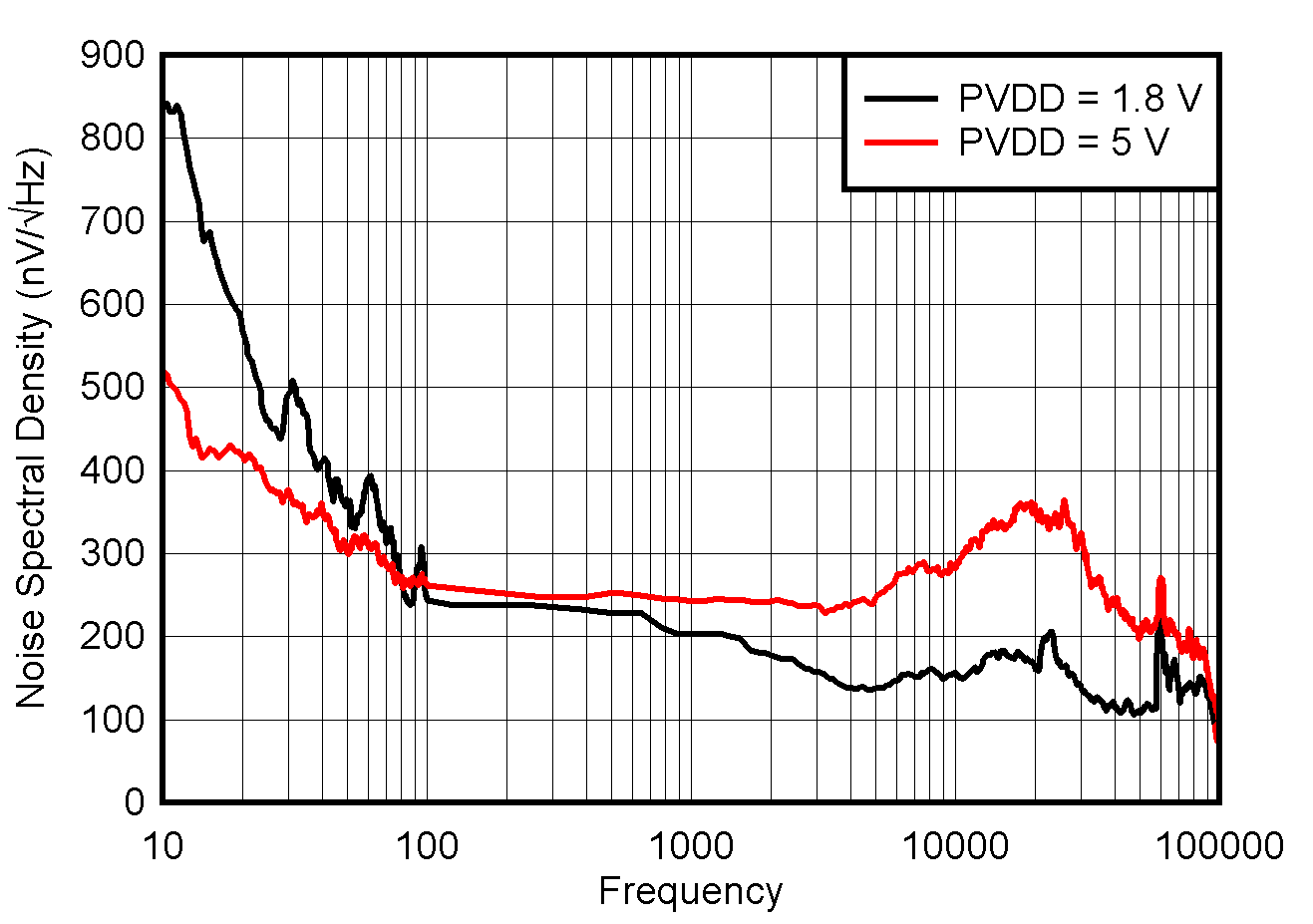

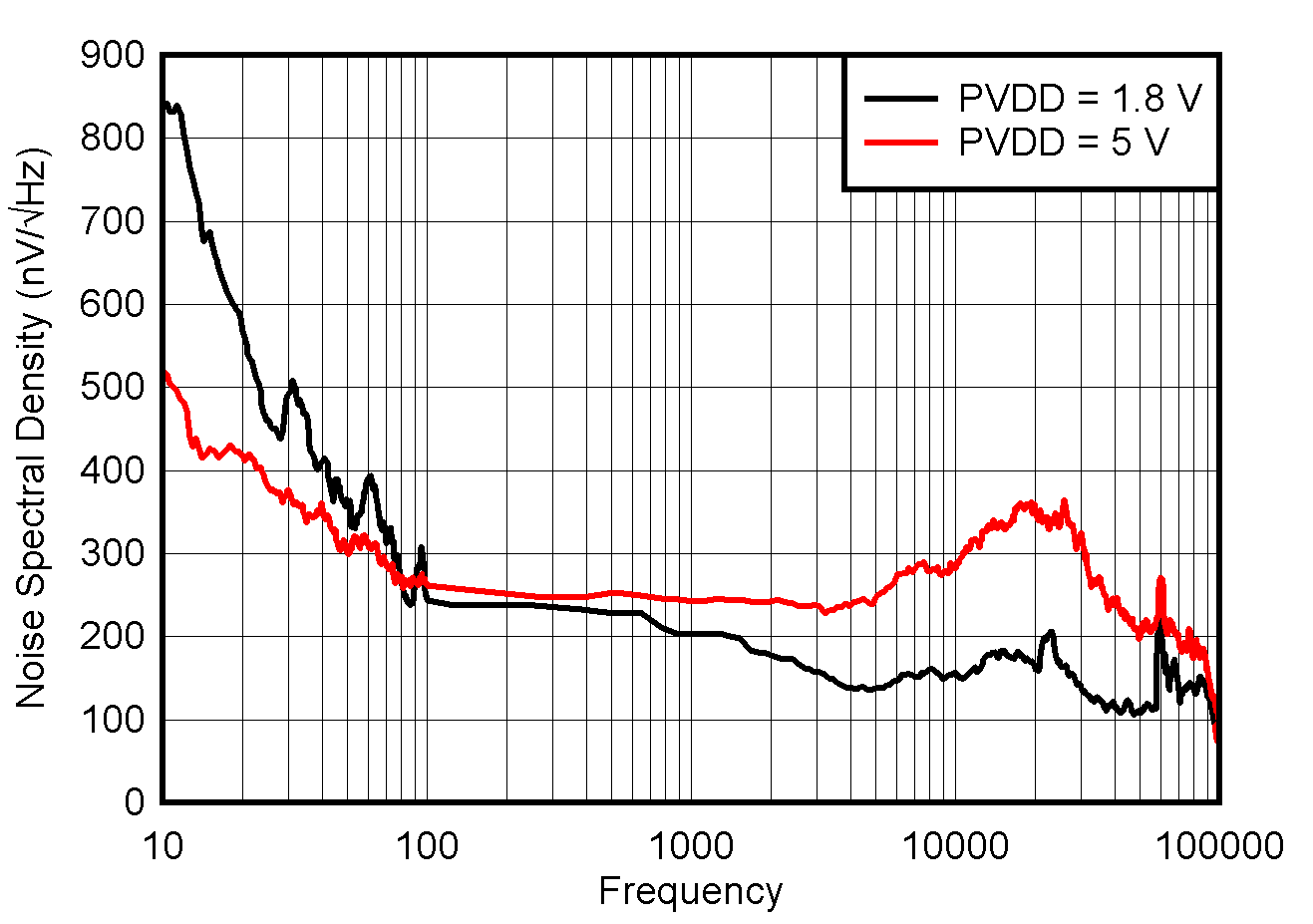

Figure 6-18 DAC Zero Scale Error vs Temperature Figure 6-20 DAC

Output Noise Density vs Frequency

Figure 6-20 DAC

Output Noise Density vs Frequency Figure 6-22 DAC

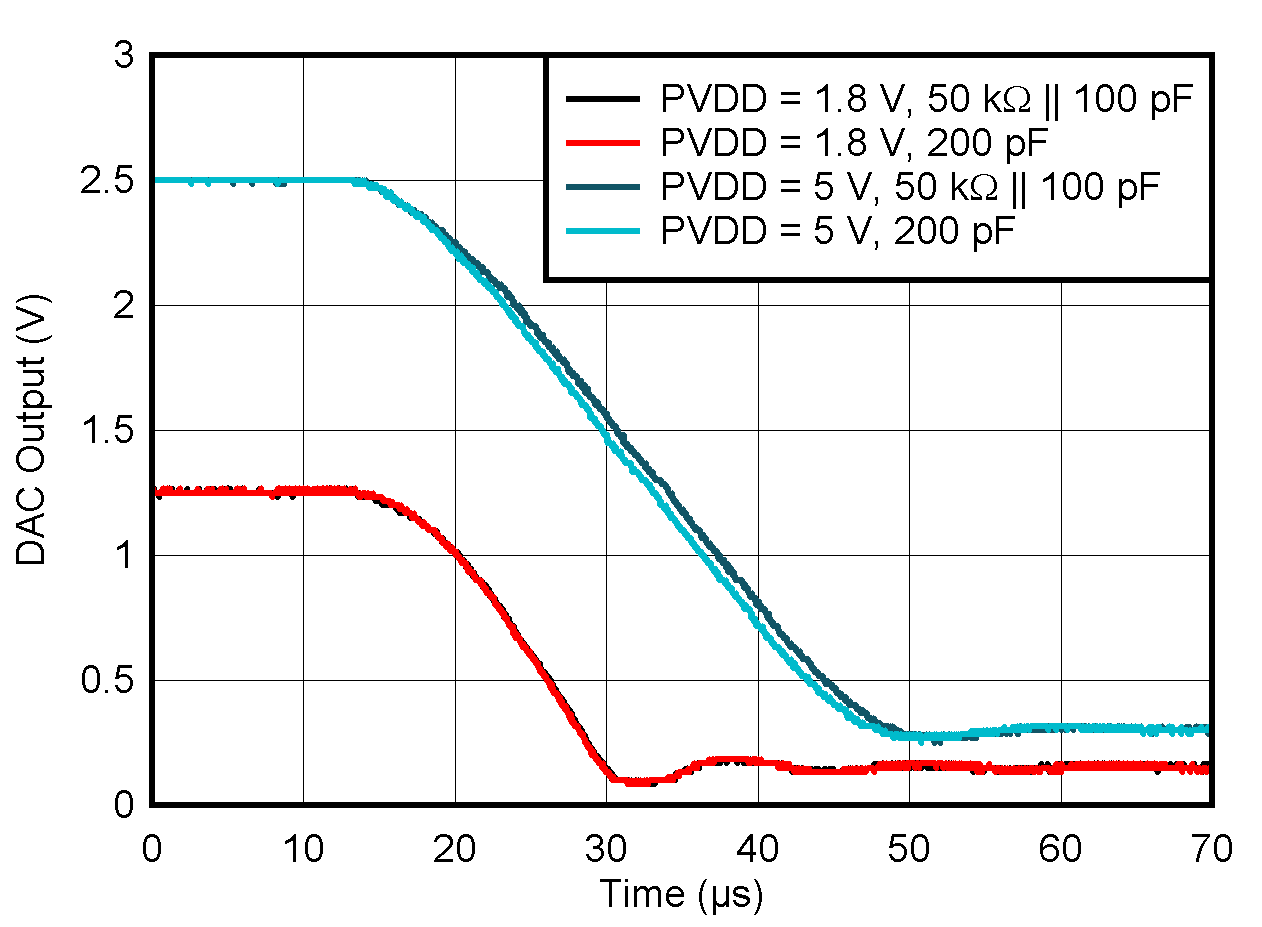

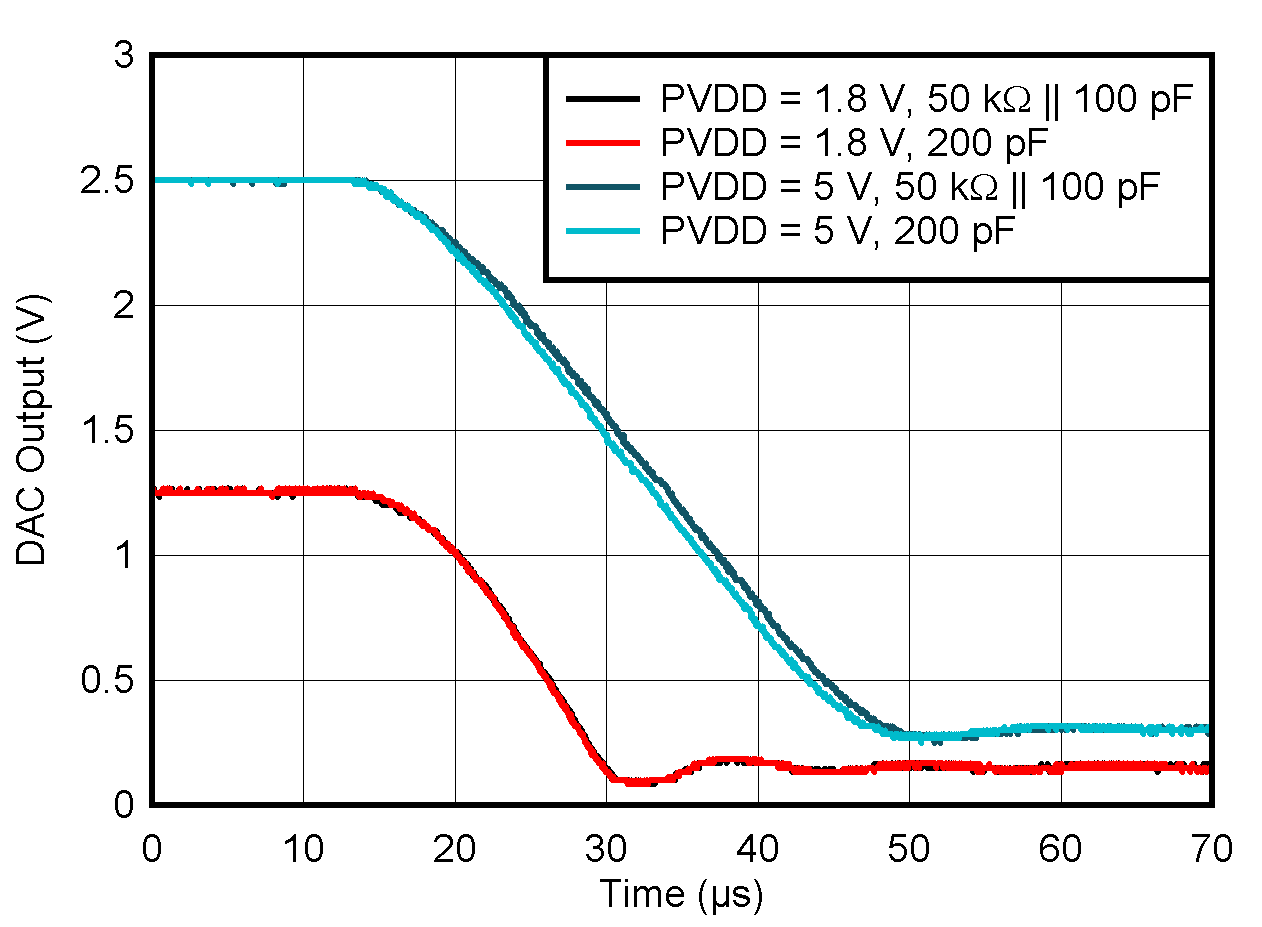

Settling Time vs Load (Falling Voltage Step)

Figure 6-22 DAC

Settling Time vs Load (Falling Voltage Step) Figure 6-24 DAC

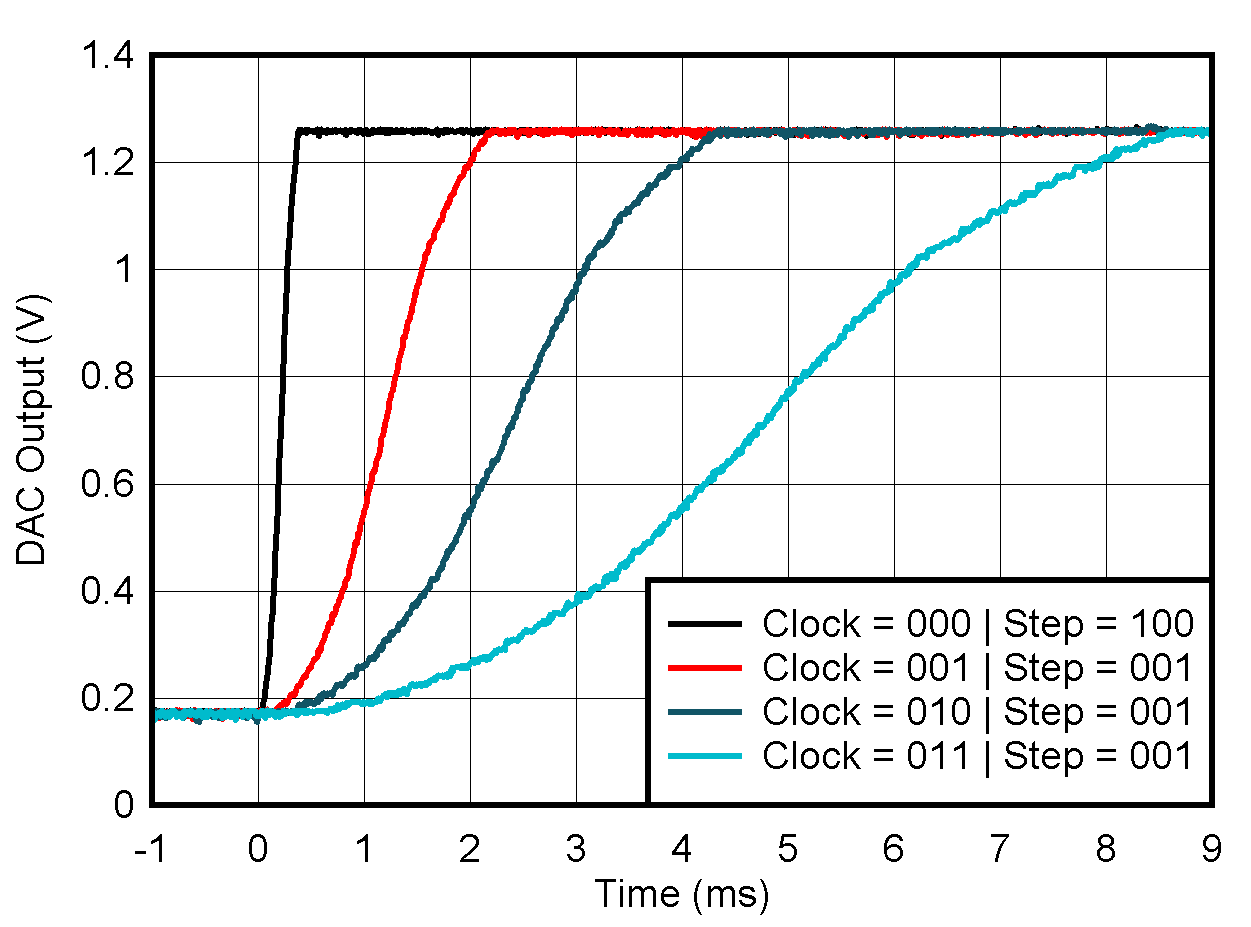

Settling Time With Sinusoidal Slew Rate Control

Figure 6-24 DAC

Settling Time With Sinusoidal Slew Rate Control Figure 6-26 DAC

Glitch Impulse Falling Edge

Figure 6-26 DAC

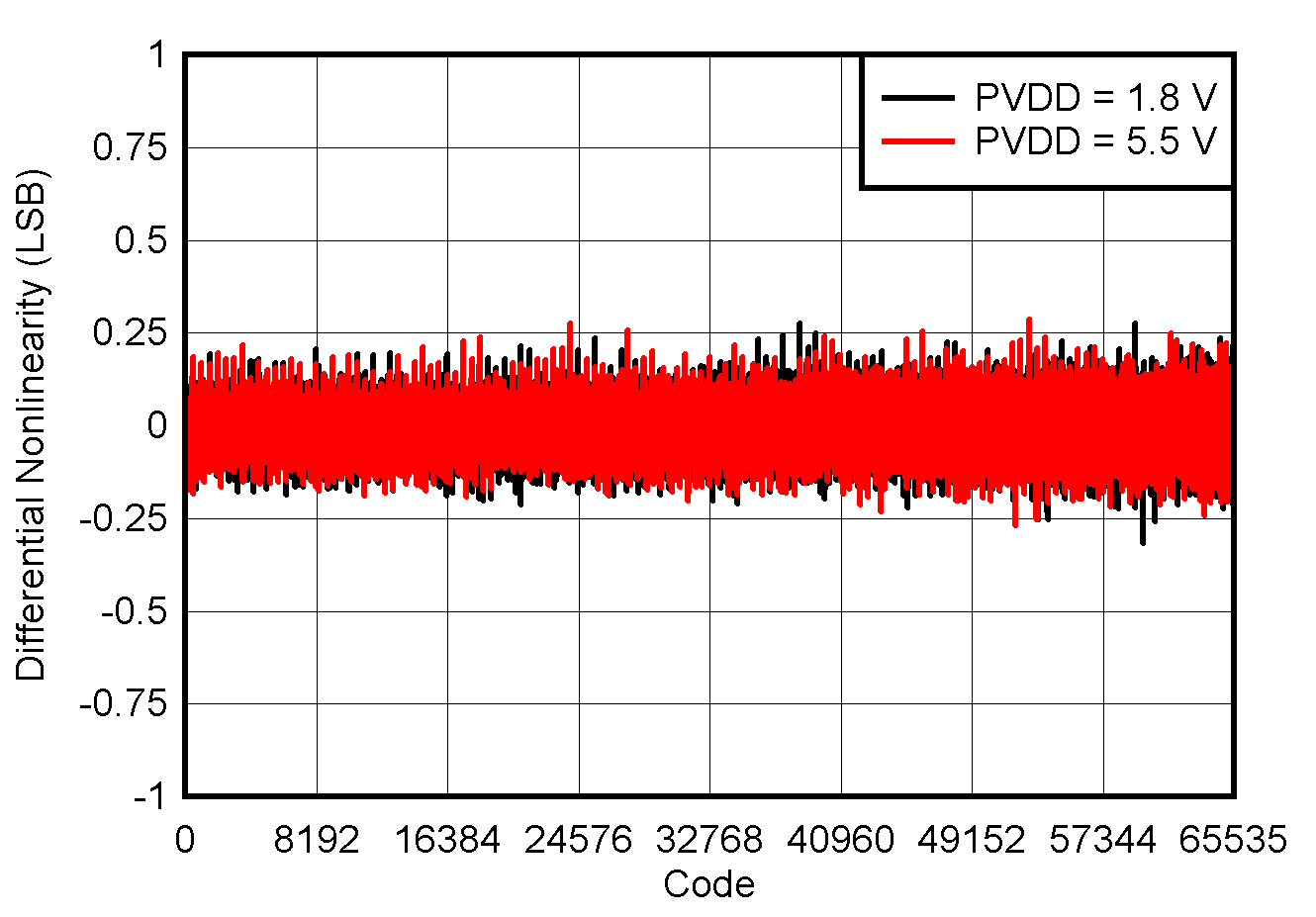

Glitch Impulse Falling Edge Figure 6-28 DAC

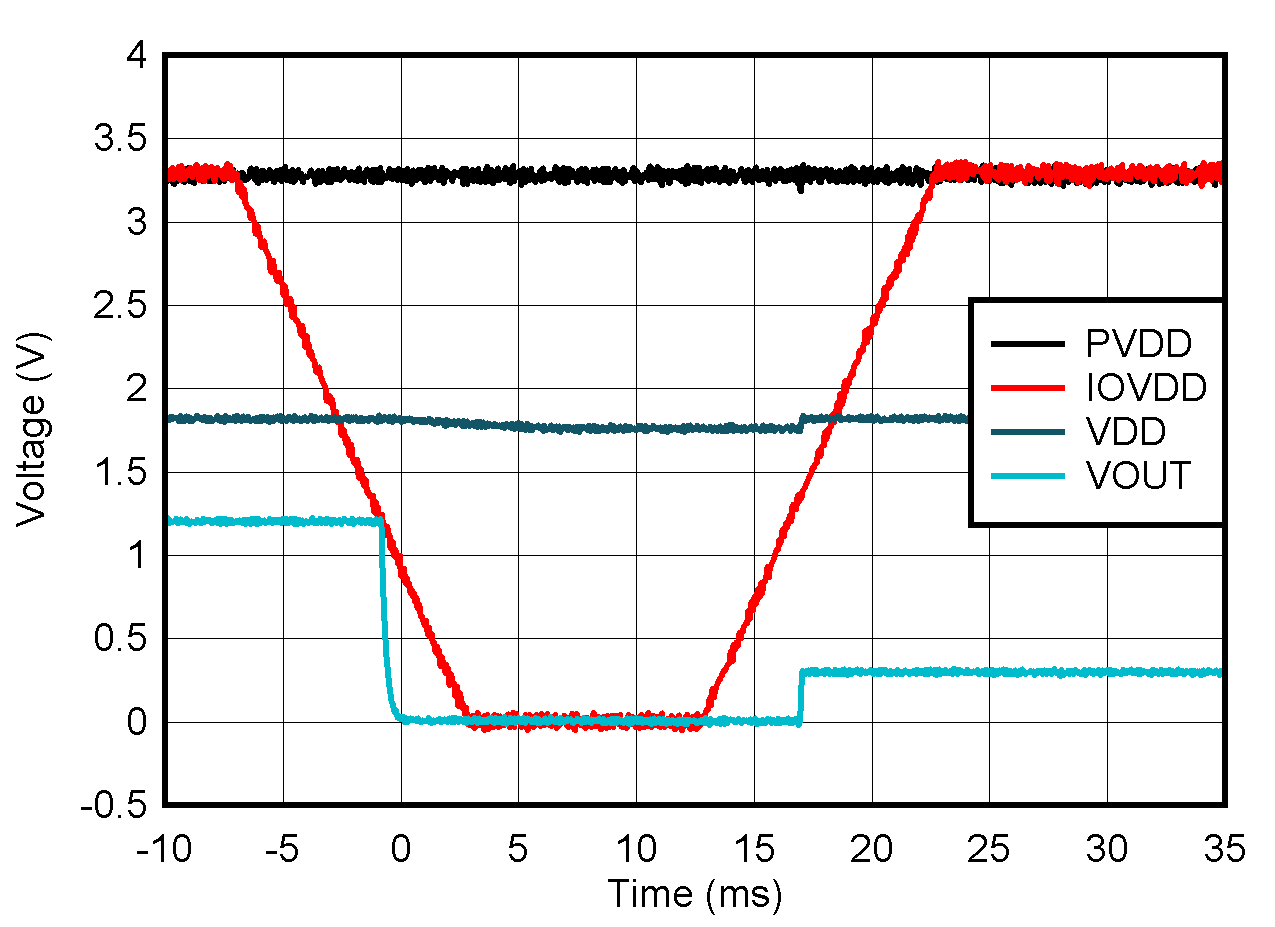

Supply Power On, PVDD = 3.3 V

Figure 6-28 DAC

Supply Power On, PVDD = 3.3 V

| 0.15-V

to 1.25-V range, midcode |

|

| |

|

|

Figure 6-30 DAC

PVDD Supply Collapse Response, RANGE = 0

| 0.4-V

to 2-V range, midcode |

|

|

|

|

Figure 6-32 DAC

IOVDD Supply Collapse Response, RANGE = 1 Figure 6-34 DAC AC PSRR vs Frequency

Figure 6-34 DAC AC PSRR vs Frequency

Figure 6-15 DAC Gain Error vs Temperature

Figure 6-15 DAC Gain Error vs Temperature Figure 6-17 DAC Full Scale Error vs Temperature

Figure 6-17 DAC Full Scale Error vs Temperature

Figure 6-27 DAC

Supply Power On, PVDD = 1.8 V

Figure 6-27 DAC

Supply Power On, PVDD = 1.8 V

Figure 6-16 DAC Offset Error vs Temperature

Figure 6-16 DAC Offset Error vs Temperature Figure 6-18 DAC Zero Scale Error vs Temperature

Figure 6-18 DAC Zero Scale Error vs Temperature

Figure 6-28 DAC

Supply Power On, PVDD = 3.3 V

Figure 6-28 DAC

Supply Power On, PVDD = 3.3 V