ZHCSU03 November 2023 BQ76905

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 器件比较表

- 5 引脚配置和功能

-

6 规格

- 6.1 绝对最大额定值

- 6.2 ESD 等级

- 6.3 建议运行条件

- 6.4 热性能信息

- 6.5 电源电流

- 6.6 数字 I/O

- 6.7 REGOUT LDO

- 6.8 电压基准

- 6.9 库仑计

- 6.10 库仑计数字滤波器

- 6.11 电流唤醒检测器

- 6.12 模数转换器

- 6.13 Cell Balancing

- 6.14 内部温度传感器

- 6.15 热敏电阻测量

- 6.16 硬件过热检测器

- 6.17 内部振荡器

- 6.18 充电和放电 FET 驱动器

- 6.19 基于比较器的保护子系统

- 6.20 时序要求 - I2C 接口,100kHz 模式

- 6.21 时序要求 - I2C 接口,400kHz 模式

- 6.22 时序图

- 6.23 典型特性

- 7 详细说明

- 8 应用和实施

- 9 器件和文档支持

- 10修订历史记录

- 11机械、封装和可订购信息

8.2.6 FET 驱动器关断

当低侧 CHG 和 DSG FET 驱动器被触发而关闭其各自的 FET 时,它们的工作方式有所不同。DSG 驱动器包含一个内部开关,当驱动器被禁用时,该开关会将 DSG 引脚驱动至 VSS 引脚电平。该驱动器指定为在具有 20nF 容性负载且 DSG 引脚和 DSG 栅极之间具有 100Ω 串联电阻时下降时间最大。如果将驱动器与较大的容性负载一起使用,下降时间通常会增加。系统设计人员可以根据使用的电路板组件和 DSG FET 来优化串联电阻值。

DSG 引脚和 DSG FET 栅极之间的外部串联栅极电阻用于调整关断瞬态的速度。低电阻(如 100Ω)可在短路事件期间提供快速关断,但这可能会在 FET 禁用时导致电池组顶部的电感尖峰过大。较大的电阻值(例如 1kΩ 或 4.7kΩ)会降低此速度和相应的电感尖峰水平。

CHG FET 驱动器会将 CHG 引脚放电至 VSS 引脚电平,但它包括一个额外的串联 PFET 以支持低于 VSS 的电压。当电池包深度放电时,通常需要这样做,例如,如果 5 节串联电池包中每节电芯的电压为 2.5V,则相对于器件 VSS,PACK+ = 12.5V。然后,如果在 CHG FET 被禁用时连接了充电器,并相对于 PACK– 在 PACK+ 上施加完全充电电压,例如每节电池 4.3V 或 5 节电池包 21.5V,这会导致 PACK– 相对于 VSS 降至大约 –9V。要使 CHG FET 保持禁用状态,其栅极电压必须降至接近此 –9V 电平。

为了支持这种情况,BQ76905 中的 CHG FET 驱动器设计为通过在该引脚上包含一个串联 PFET 且其栅极连接到 VSS,能够承受相对于 VSS 引脚电压低至 –25V(推荐)的电压。当 CHG 驱动器被禁用时,该驱动器会将引脚电压拉低。当引脚电压接近 VSS 时,PFET 被禁用,从而使该引脚变为高阻抗。此时,CHG FET 上的外部栅源电阻器会将引脚电压拉低至 PACK– 电平,使 CHG FET 保持禁用状态。

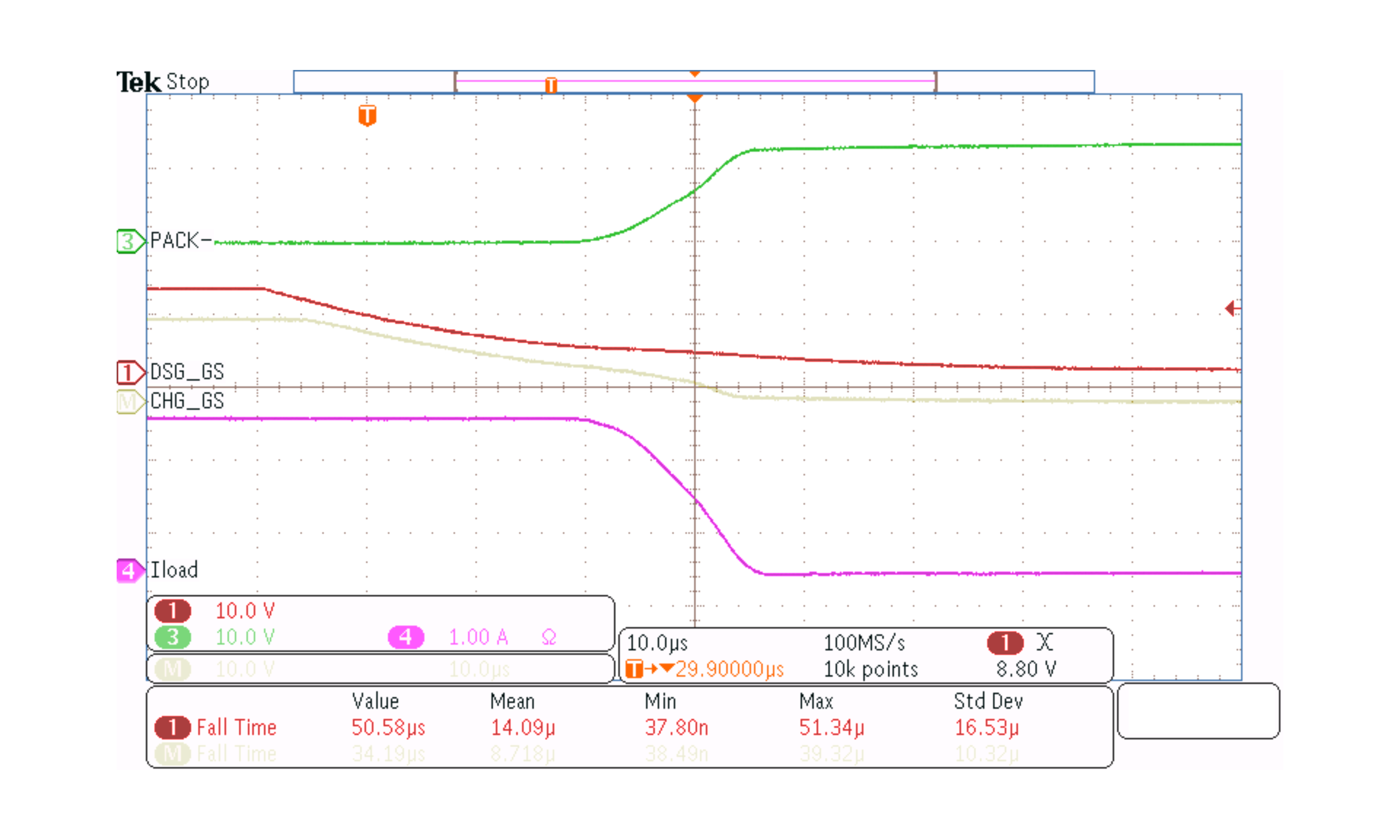

下面展示了 CHG 和 DSG 驱动器关断情况下示波器捕获的波形,其中相应引脚驱动 CSD18532Q5B NFET 栅极,其典型 Ciss 为 3900pF。图 8-12 展示了在 DSG 引脚和 FET 栅极之间使用 1.35kΩ 串联栅极电阻器以及在 PACK+ 和 PACK– 之间连接 2A 负载时的信号。

图 8-6 中速 DSG FET 关断,使用一个 1.35kΩ 串联栅极电阻,并且 PACK+ 和 PACK– 之间具有 2A 负载。

图 8-6 中速 DSG FET 关断,使用一个 1.35kΩ 串联栅极电阻,并且 PACK+ 和 PACK– 之间具有 2A 负载。图 8-7 展示了一个较慢的关断情况,其中使用一个 4.5kΩ 串联栅极电阻器且 PACK+ 和 PACK– 之间具有 2A 负载。

图 8-7 使用 4.5kΩ 串联栅极电阻器时的较慢关断情况

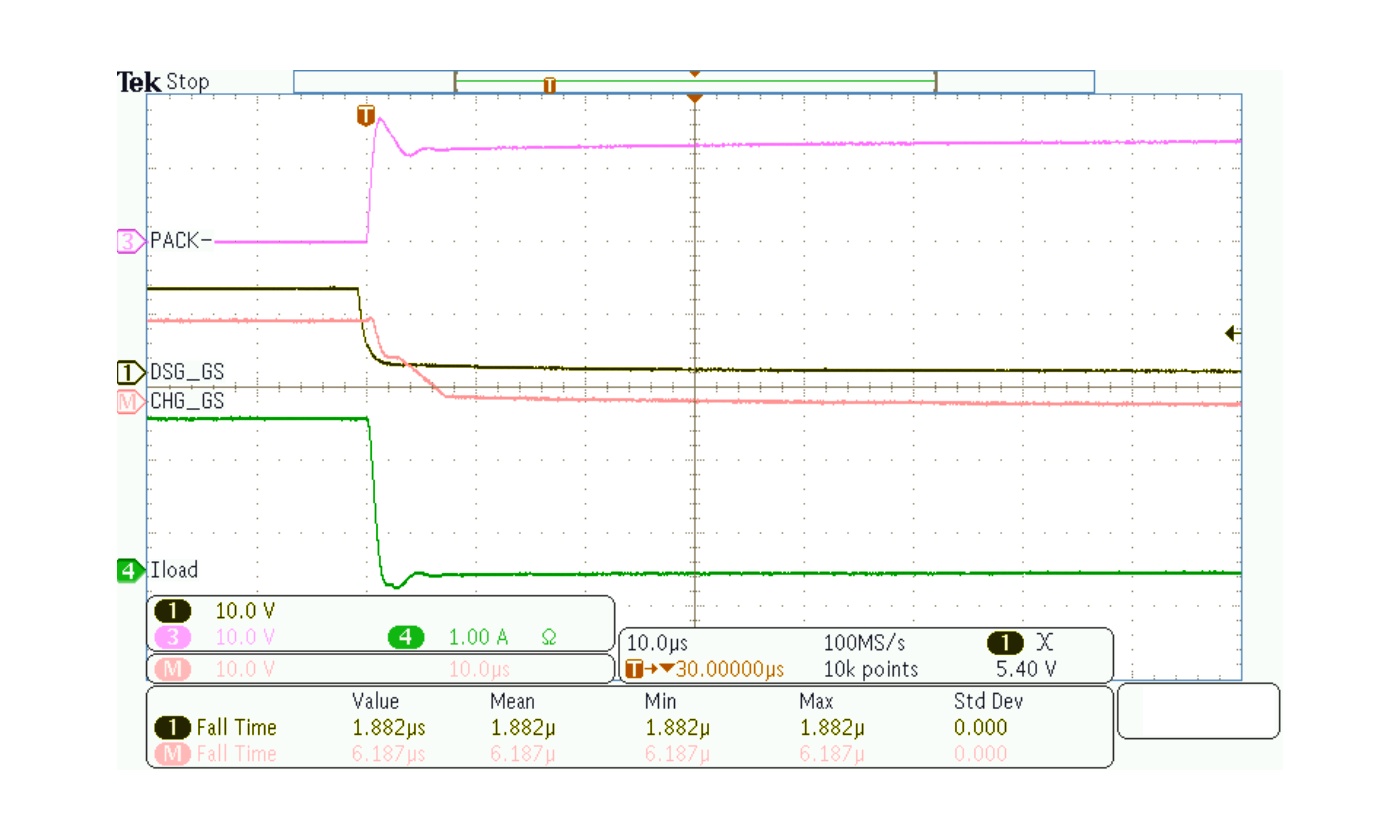

图 8-7 使用 4.5kΩ 串联栅极电阻器时的较慢关断情况图 8-8 展示了快速关断情况,其中在 DSG 引脚和 FET 栅极之间使用了一个 100Ω 串联栅极电阻器。

图 8-8 使用 100Ω 串联栅极电阻时的快速关断情况

图 8-8 使用 100Ω 串联栅极电阻时的快速关断情况