ZHCSU48 December 2023 BQ76972

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 器件比较表

- 5 引脚配置和功能

-

6 规格

- 6.1 绝对最大额定值

- 6.2 ESD 等级

- 6.3 建议运行条件

- 6.4 热性能信息 BQ76952

- 6.5 电源电流

- 6.6 数字 I/O

- 6.7 LD 引脚

- 6.8 预充电 (PCHG) 和预放电 (PDSG) FET 驱动器

- 6.9 FUSE 引脚功能

- 6.10 REG18 LDO

- 6.11 REG0 前置稳压器

- 6.12 REG1 LDO

- 6.13 REG2 LDO

- 6.14 电压基准

- 6.15 库仑计

- 6.16 库仑计数字滤波器 (CC1)

- 6.17 电流测量数字滤波器 (CC2)

- 6.18 电流唤醒检测器

- 6.19 模数转换器

- 6.20 电芯电压测量精度

- 6.21 Cell Balancing

- 6.22 电芯开路保护器

- 6.23 内部温度传感器

- 6.24 热敏电阻测量

- 6.25 内部振荡器

- 6.26 高侧 NFET 驱动器

- 6.27 基于比较器的保护子系统

- 6.28 时序要求 - I2C 接口,100kHz 模式

- 6.29 时序要求 - I2C 接口,400kHz 模式

- 6.30 时序要求 - HDQ 接口

- 6.31 时序要求 - SPI 接口

- 6.32 接口时序图

- 6.33 典型特性

- 7 详细说明

- 8 应用和实施

- 9 器件和文档支持

- 10修订历史记录

- 11机械、封装和可订购信息

8.5 FET 驱动器关断

当高侧 CHG 和 DSG FET 驱动器被触发而关闭其各自的 FET 时,它们的工作方式有所不同。CHG 驱动器包含一个内部开关,该开关将 CHG 引脚放电至 BAT 引脚电平。DSG FET 驱动器会将 DSG 引脚向 LD 引脚电平放电,但它包含比开关更复杂的结构,以支持更快的关断。

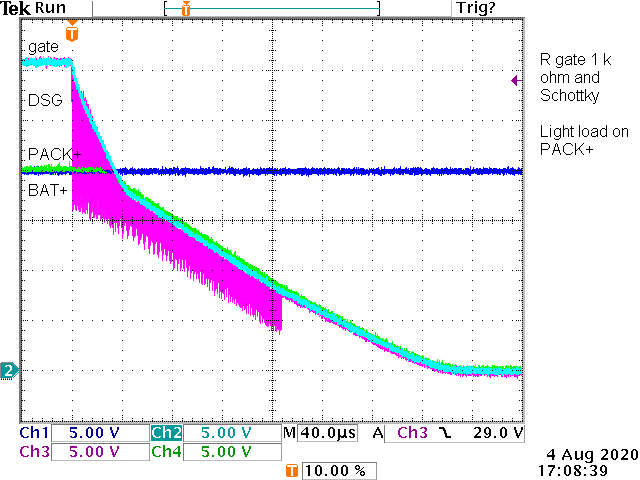

当 DSG 驱动器被触发关断时,该器件将最先开始向 VSS 对 DSG 引脚放电。但是,由于 PACK+ 端子可能不会很快下降到接近 VSS 的电压,因此不应将 DSG FET 栅极驱动到显著低于 PACK+ 的电压,否则 DSG FET 可能会因栅极-源极负电压过高而受损。因此,器件监控 LD 引脚(通过外部串联电阻器连接到 PACK+)上的电压,并在 DSG 引脚电压低于 LD 引脚电压时停止放电。当放电停止时,DSG 引脚电压可能会放松回到 LD 引脚电压以上,此时器件将再次向 VSS 对 DSG 引脚放电,直到 DSG 栅极电压再次降至 LD 引脚电压以下。此过程在一系列脉冲中重复,这些脉冲随着时间的推移将 DSG 栅极放电至 LD 引脚的电压。该脉冲持续约 100μs 至 200μs,之后如果处于 LD 引脚电压的约 500mV 以内,驱动器将保持高阻抗状态。然后,DSG 栅极和源极之间的外部电阻器释放剩余 FET VGS 电压,使 FET 保持关断。

DSG 引脚和 DSG FET 栅极之间的外部串联栅极电阻用于调整关断瞬态的速度。低电阻(如 100Ω)可在短路事件期间提供快速关断,但这可能会在 FET 禁用时导致电池组顶部的电感尖峰过大。较大的电阻值(例如 1kΩ 或 4.7kΩ)会降低此速度和相应的电感尖峰水平。

下面展示了 DSG 驱动器关断情况下示波器捕获的波形,其中 DSG 引脚驱动 CSD19536KCS NFET 栅极,其典型 Ciss 为 9250pF。图 8-6 展示了在 DSG 引脚和 FET 栅极之间使用 1kΩ 串联栅极电阻器以及在 PACK+ 上连接轻负载(从而使 PACK+ 上的电压在 FET 禁用时缓慢下降)时的信号。DSG 引脚上的脉冲持续约 170μs。

图 8-6 中速 DSG FET 关断,使用 1kΩ 串联栅极电阻器,在 PACK+ 上连接轻负载

图 8-7 显示了 DSG 引脚生成的脉冲的放大视图,此次 PACK+ 短接至电池组顶部。

图 8-7 FET 关断期间 DSG 引脚上的脉冲的放大视图

图 8-8 展示了一个较慢的关断情况,其中使用一个 4.7kΩ 串联栅极电阻器并且 PACK+ 连接器短接至电池组顶部。

图 8-8 A 使用 4.7kΩ 串联栅极电阻器且 PACK+ 连接器短接至电池组顶部的较慢关断情况

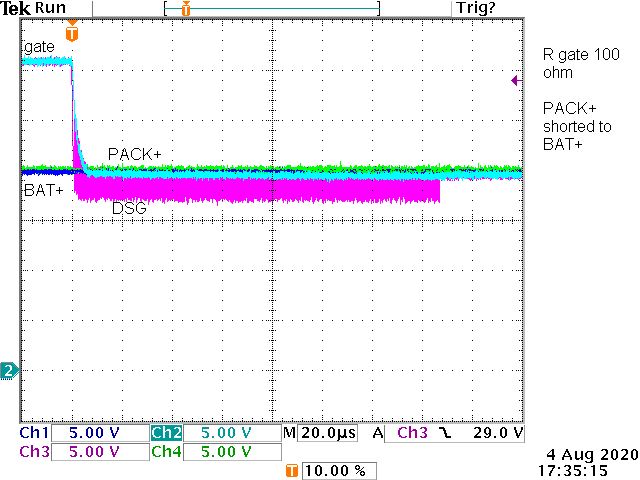

图 8-9 展示了快速关断情况,其中在 DSG 引脚和 FET 栅极之间使用了一个 100Ω 串联栅极电阻器。

图 8-9 使用 100Ω 串联栅极电阻器时的快速关断情况