ZHCSPQ4E January 1998 – October 2022 CD54HC540 , CD54HC541 , CD54HCT541 , CD74HC540 , CD74HC541 , CD74HCT540 , CD74HCT541

PRODUCTION DATA

2 说明

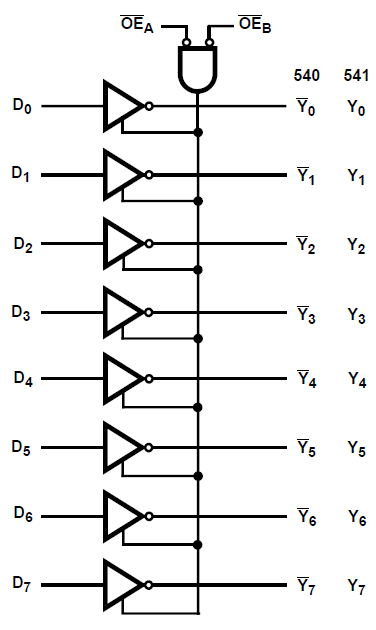

’HC540 和 CD74HCT540 是具有三态输出的反相八路缓冲器和线路驱动器,能够驱动 15 个 LSTTL 负载。’HC541 和 ’HCT541 是具有三态输出的同相八路缓冲器和线路驱动器,能够驱动 15 个 LSTTL 负载。输出使能 (OE1) 和 (OE2) 控制三态输出。如果 OE1 或 OE2 为高电平,则输出处于高阻抗状态。对于数据输出,OE1 和 OE2 都必须为低电平。

封装信息

| 器件型号 | 封装(1) | 封装尺寸(标称值) |

|---|---|---|

| CD74HC540M | SOIC (20) | 12.80mm × 7.50mm |

| CD74HC540E | PDIP (20) | 25.40mm × 6.35mm |

| CD54HC540F3A | CDIP (20) | 26.92mm × 6.92mm |

| CD74HC541M | SOIC (20) | 12.80mm × 7.50mm |

| CD74HC541E | PDIP (20) | 25.40mm × 6.35mm |

| CD54HC541F | CDIP (20) | 26.92mm × 6.92mm |

| CD74HCT540M | SOIC (20) | 12.80mm × 7.50mm |

| CD74HCT540E | PDIP (20) | 25.40mm × 6.35mm |

| CD74HCT541M | SOIC (20) | 12.80mm × 7.50mm |

| CD74HCT541E | PDIP (20) | 25.40mm × 6.35mm |

| CD54HCT541F | CDIP (20) | 26.92mm × 6.92mm |

| CD74HCT541PW | TSSOP (20) | 6.50mm × 4.40mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购米6体育平台手机版_好二三四附录。

功能图

功能图