SNAS363F May 2006 – March 2016 DAC084S085

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

- DSC|10

订购信息

7 Specifications

7.1 Absolute Maximum Ratings(1)(2)(3)

| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Supply voltage, VA | 6.5 | V | ||

| Voltage on any input pin | −0.3 | 6.5 | V | |

| Input current at any pin(4) | 10 | mA | ||

| Package input current(4) | 20 | mA | ||

| Power consumption at TA = 25°C | See(5) | |||

| Junction temperature | 150 | °C | ||

| Storage temperature, Tstg | −65 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are measured with respect to GND = 0 V, unless otherwise specified.

(3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Semiconductor Sales Office/Distributors for availability and specifications.

(4) When the input voltage at any pin exceeds 5.5 V or is less than GND, the current at that pin must be limited to 10 mA. The 20 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of

10 mA to two.

10 mA to two.

(5) The absolute maximum junction temperature (TJmax) for this device is 150°C. The maximum allowable power dissipation is dictated by TJmax, the junction-to-ambient thermal resistance (θJA), and the ambient temperature (TA), and can be calculated using the formula PDMAX = (TJmax − TA) / θJA. The values for maximum power dissipation is reached only when the device is operated in a severe fault condition (that is, when input or output pins are driven beyond the operating ratings, or the power supply polarity is reversed).

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001(1)(2) | ±2500 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(3) | ±250 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) Human body model is 100-pF capacitor discharged through a 1.5-kΩ resistor. Machine model is 220 pF discharged through 0 Ω.

(3) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

See (1)| MIN | MAX | UNIT | |

|---|---|---|---|

| Operating temperature | −40 | 105 | °C |

| Supply voltage, VA | 2.7 | 5.5 | V |

| Reference voltage, VREFIN | 1 | VA | V |

| Digital input voltage (2) | 0 | 5.5 | V |

| Output load | 0 | 1500 | pF |

| SCLK frequency | 40 | MHz |

(1) All voltages are measured with respect to GND = 0 V, unless otherwise specified.

(2) The inputs are protected as shown below. Input voltage magnitudes up to 5.5 V, regardless of VA, does not cause errors in the conversion result. For example, if VA is 3 V, the digital input pins can be driven with a 5-V logic device.

7.4 Thermal Information

| THERMAL METRIC(1)(2) | DAC084S085 | UNIT | ||

|---|---|---|---|---|

| DGS (VSSOP) | DSC (WSON) | |||

| 10 PINS | 10 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 240 | 250 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 53.3 | 40.7 | °C/W |

| RθJB | Junction-to-board thermal resistance | 78.9 | 23.7 | °C/W |

| ψJT | Junction-to-top characterization parameter | 4.8 | 0.4 | °C/W |

| ψJB | Junction-to-board characterization parameter | 77.6 | 23.8 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | N/A | 4.7 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

(2) Reflow temperature profiles are different for lead-free packages..

7.5 Electrical Characteristics

The following specifications apply for VA = 2.7 V to 5.5 V, VREFIN = VA, CL = 200 pF to GND, fSCLK = 30 MHz, input code range 3 to 252. All limits are at TA = 25°C, unless otherwise specified.| PARAMETER | TEST CONDITIONS | MIN(1) | TYP(1) | MAX(1) | UNIT | |||

|---|---|---|---|---|---|---|---|---|

| STATIC PERFORMANCE | ||||||||

| Resolution | TMIN ≤ TA ≤ TMAX | 8 | Bits | |||||

| Monotonicity | TMIN ≤ TA ≤ TMAX | 8 | Bits | |||||

| INL | Integral non-linearity | TA = 25°C | ±0.14 | LSB | ||||

| TMIN ≤ TA ≤ TMAX | ±0.5 | |||||||

| DNL | Differential non-linearity | VA = 2.7 V to 5.5 V | TA = 25°C | −0.02 | +0.04 | LSB | ||

| TMIN ≤ TA ≤ TMAX | −0.13 | +0.18 | ||||||

| ZE | Zero code error | IOUT = 0 mA | TA = 25°C | +4 | mV | |||

| TMIN ≤ TA ≤ TMAX | +15 | |||||||

| FSE | Full-scale error | IOUT = 0 mA | TA = 25°C | −0.1 | %FSR | |||

| TMIN ≤ TA ≤ TMAX | −0.75 | |||||||

| GE | Gain error | All ones Loaded to DAC register | TA = 25°C | −0.2 | %FSR | |||

| TMIN ≤ TA ≤ TMAX | −1 | |||||||

| ZCED | Zero code error drift | −20 | µV/°C | |||||

| TC GE | Gain error tempco | VA = 3 V | −0.7 | ppm/°C | ||||

| VA = 5 V | −1 | |||||||

| OUTPUT CHARACTERISTICS | ||||||||

| Output voltage range | See (2), TMIN ≤ TA ≤ TMAX | 0 | VREFIN | V | ||||

| IOZ | High-impedance output leakage current(2) | TMIN ≤ TA ≤ TMAX | ±1 | µA | ||||

| ZCO | Zero code output | VA = 3 V, IOUT = 200 µA | 1.3 | mV | ||||

| VA = 3 V, IOUT = 1 mA | 6 | |||||||

| VA = 5 V, IOUT = 200 µA | 7 | |||||||

| VA = 5 V, IOUT = 1 mA | 10 | |||||||

| FSO | Full scale output | VA = 3 V, IOUT = 200 µA | 2.984 | V | ||||

| VA = 3 V, IOUT = 1 mA | 2.934 | |||||||

| VA = 5 V, IOUT = 200 µA | 4.989 | |||||||

| VA = 5 V, IOUT = 1 mA | 4.958 | |||||||

| IOS | Output short-circuit current (source) | VA = 3 V, VOUT = 0 V, Input Code = FFh |

–56 | mA | ||||

| VA = 5 V, VOUT = 0 V, Input Code = FFh |

–69 | |||||||

| IOS | Output short-circuit current (sink) | VA = 3 V, VOUT = 3 V, Input Code = 00h |

52 | mA | ||||

| VA = 5 V, VOUT = 5 V, Input Code = 00h |

75 | |||||||

| IO | Continuous output current(2) |

Avaliable on each DAC output, TMIN ≤ TA ≤ TMAX | 11 | mA | ||||

| CL | Maximum load capacitance | RL = ∞ | 1500 | pF | ||||

| RL = 2 kΩ | 1500 | |||||||

| ZOUT | DC output impedance | 7.5 | Ω | |||||

| REFERENCE INPUT CHARACTERISTICS | ||||||||

| VREFIN | Input range minimum | 0.2 | V | |||||

| TMIN ≤ TA ≤ TMAX | 1 | |||||||

| Input range maximum | TMIN ≤ TA ≤ TMAX | VA | V | |||||

| Input impedance | 30 | kΩ | ||||||

| LOGIC INPUT CHARACTERISTICS | ||||||||

| IIN | Input current(2) | TMIN ≤ TA ≤ TMAX | ±1 | µA | ||||

| VIL | Input low voltage(2) | VA = 3 V | TA = 25°C | 0.9 | V | |||

| TMIN ≤ TA ≤ TMAX | 0.6 | |||||||

| VA = 5 V | TA = 25°C | 1.5 | V | |||||

| TMIN ≤ TA ≤ TMAX | 0.8 | |||||||

| VIH | Input high voltage(2) | VA = 3 V | TA = 25°C | 1.4 | V | |||

| TMIN ≤ TA ≤ TMAX | 2.1 | |||||||

| VA = 5 V | TA = 25°C | 2.1 | V | |||||

| TMIN ≤ TA ≤ TMAX | 2.4 | |||||||

| CIN | Input capacitance(2) | TMIN ≤ TA ≤ TMAX | 3 | pF | ||||

| POWER REQUIREMENTS | ||||||||

| VA | Supply voltage minimum | TMIN ≤ TA ≤ TMAX | 2.7 | V | ||||

| Supply voltage maximum | TMIN ≤ TA ≤ TMAX | 5.5 | V | |||||

| IN | Normal supply current (output unloaded) | fSCLK = 30 MHz | VA = 2.7 V to 3.6 V |

TA = 25°C | 370 | µA | ||

| TMIN ≤ TA ≤ TMAX | 485 | |||||||

| VA = 4.5 V to 5.5 V |

TA = 25°C | 500 | µA | |||||

| TMIN ≤ TA ≤ TMAX | 650 | |||||||

| fSCLK = 0 MHz | VA = 2.7 V to 3.6 V |

350 | µA | |||||

| VA = 4.5 V to 5.5 V |

460 | µA | ||||||

| IPD | Power-down supply current (output unloaded, SYNC = DIN = 0 V after PD mode loaded) | All PD Modes(2) | VA = 2.7 V to 3.6 V |

TA = 25°C | 0.1 | µA | ||

| TMIN ≤ TA ≤ TMAX | 1 | |||||||

| VA = 4.5 V to 5.5 V |

TA = 25°C | 0.15 | µA | |||||

| TMIN ≤ TA ≤ TMAX | 1 | |||||||

| PN | Normal supply power (output unloaded) | fSCLK = 30 MHz | VA = 2.7 V to 3.6 V |

TA = 25°C | 1.1 | mW | ||

| TMIN ≤ TA ≤ TMAX | 1.7 | |||||||

| VA = 4.5 V to 5.5 V |

TA = 25°C | 2.5 | mW | |||||

| TMIN ≤ TA ≤ TMAX | 3.6 | |||||||

| fSCLK = 0 MHz | VA = 2.7 V to 3.6 V |

1.1 | mW | |||||

| VA = 4.5 V to 5.5 V |

2.3 | mW | ||||||

| PPD | Power-down supply power (output unloaded, SYNC = DIN = 0 V after PD mode loaded) | All PD Modes(2) | VA = 2.7 V to 3.6 V |

TA = 25°C | 0.3 | µW | ||

| TMIN ≤ TA ≤ TMAX | 3.6 | |||||||

| VA = 4.5 V to 5.5 V |

TA = 25°C | 0.8 | µW | |||||

| TMIN ≤ TA ≤ TMAX | 5.5 | |||||||

(1) Typical figures are at TJ = 25°C, and represent most likely parametric norms. Test limits are specified to AOQL (Average Outgoing Quality Level).

(2) This parameter is specified by design and/or characterization and is not tested in production.

7.6 Timing Requirements

Values shown in this table are design targets and are subject to change before product release.The following specifications apply for VA = 2.7 V to 5.5 V, VREFIN = VA, CL = 200 pF to GND, fSCLK = 30 MHz, input code range 3 to 252. All limits are at TA = 25°C, unless otherwise specified.

| MIN(1) | TYP(1) | MAX(1) | UNIT | ||||

|---|---|---|---|---|---|---|---|

| fSCLK | SCLK frequency | TA = 25°C | 40 | MHz | |||

| TMIN ≤ TA ≤ TMAX | 30 | ||||||

| ts | Output voltage settling time(2) | 40h to C0h code change RL = 2 kΩ, CL = 200 pF |

TA = 25°C | 3 | µs | ||

| TMIN ≤ TA ≤ TMAX | 4.5 | ||||||

| SR | Output slew rate | 1 | V/µs | ||||

| Glitch impulse | Code change from 80h to 7Fh | 12 | nV-sec | ||||

| Digital feedthrough | 0.5 | nV-sec | |||||

| Digital crosstalk | 1 | nV-sec | |||||

| DAC-to-DAC crosstalk | 3 | nV-sec | |||||

| Multiplying bandwidth | VREFIN = 2.5 V ± 0.1 Vpp | 160 | kHz | ||||

| Total harmonic distortion | VREFIN = 2.5 V ± 0.1 Vpp input frequency = 10 kHz |

70 | dB | ||||

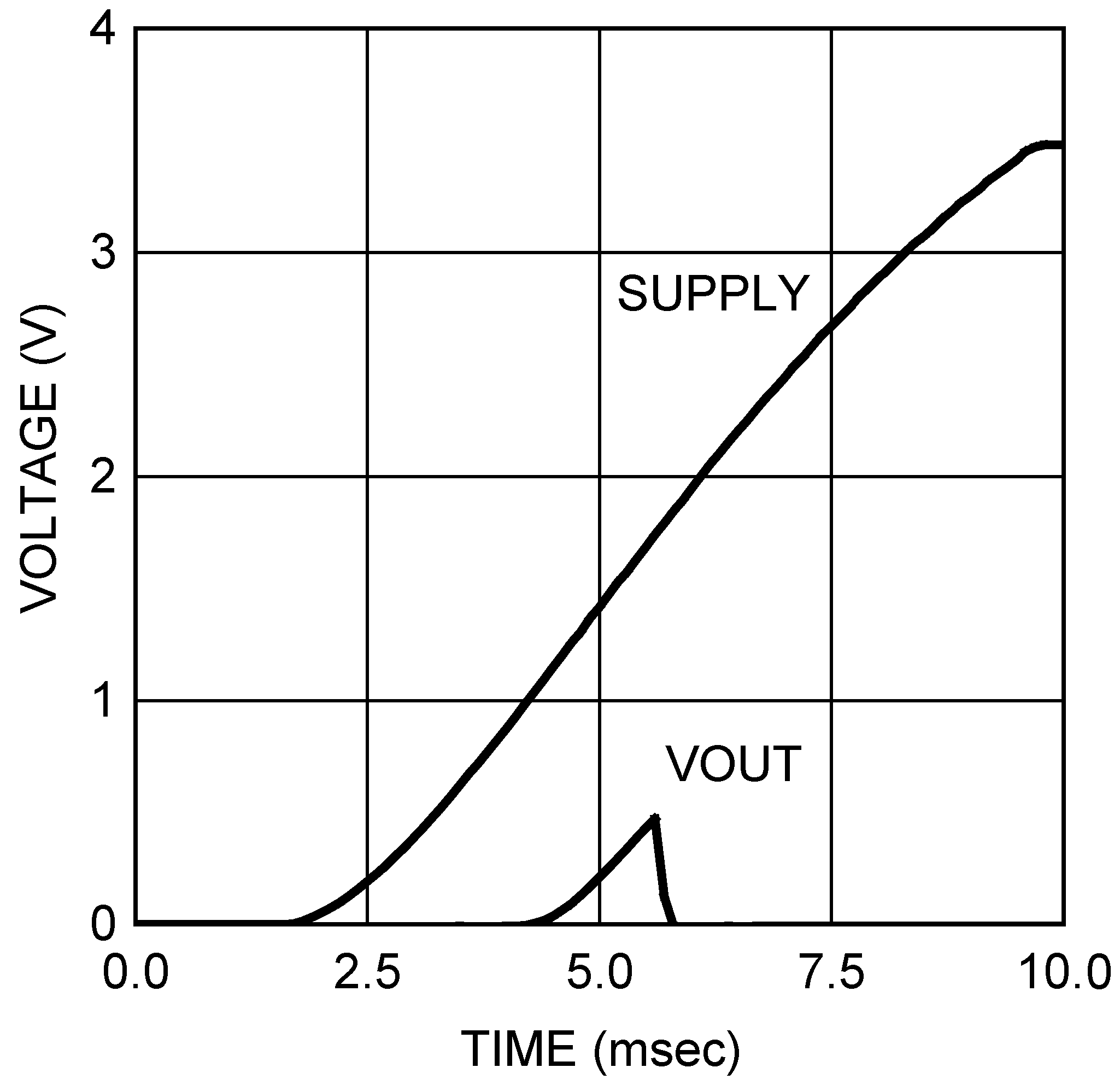

| tWU | Wake-up time | VA = 3 V | 6 | µsec | |||

| VA = 5 V | 39 | µsec | |||||

| 1/fSCLK | SCLK cycle time | TA = 25°C | 25 | ns | |||

| TMIN ≤ TA ≤ TMAX | 33 | ||||||

| tCH | SCLK high time | TA = 25°C | 7 | ns | |||

| TMIN ≤ TA ≤ TMAX | 10 | ||||||

| tCL | SCLK low Time | TA = 25°C | 7 | ns | |||

| TMIN ≤ TA ≤ TMAX | 10 | ||||||

| tSS | SYNC set-up time prior to SCLK falling edge | TA = 25°C | 4 | ns | |||

| TMIN ≤ TA ≤ TMAX | 10 | ||||||

| tDS | Data set-up time prior to SCLK falling edge | TA = 25°C | 1.5 | ns | |||

| TMIN ≤ TA ≤ TMAX | 3.5 | ||||||

| tDH | Data hold time after SCLK falling edge | TA = 25°C | 1.5 | ns | |||

| TMIN ≤ TA ≤ TMAX | 3.5 | ||||||

| tCFSR | SCLK fall prior to rise of SYNC | TA = 25°C | 0 | ns | |||

| TMIN ≤ TA ≤ TMAX | 3 | ||||||

| tSYNC | SYNC high time | TA = 25°C | 6 | ns | |||

| TMIN ≤ TA ≤ TMAX | 10 | ||||||

(1) Typical figures are at TJ = 25°C, and represent most likely parametric norms. Test limits are specified to AOQL (Average Outgoing Quality Level).

(2) This parameter is specified by design and/or characterization and is not tested in production.

Figure 1. Serial Timing Diagram

Figure 1. Serial Timing Diagram

Figure 2. Input / Output Transfer Characteristic

Figure 2. Input / Output Transfer Characteristic

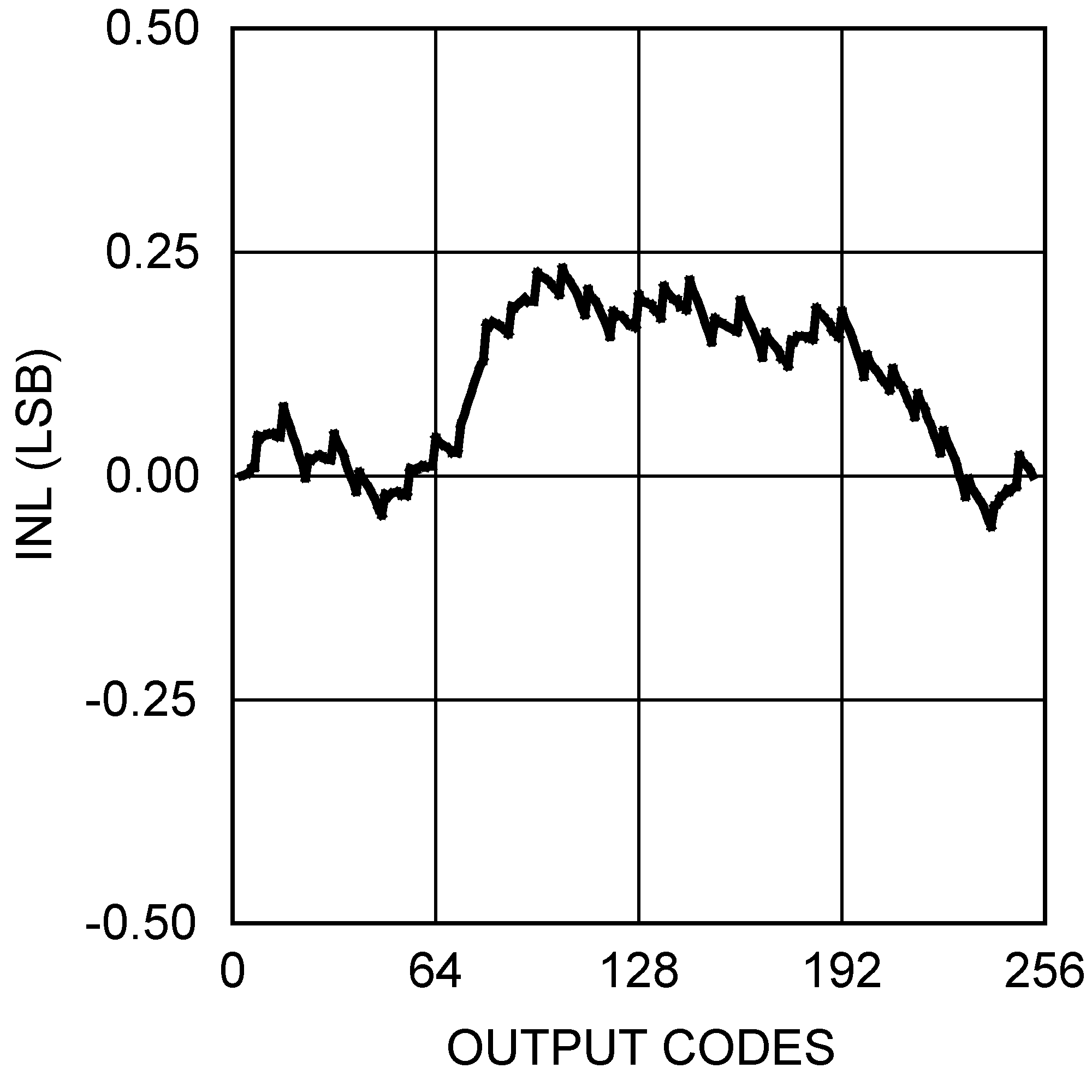

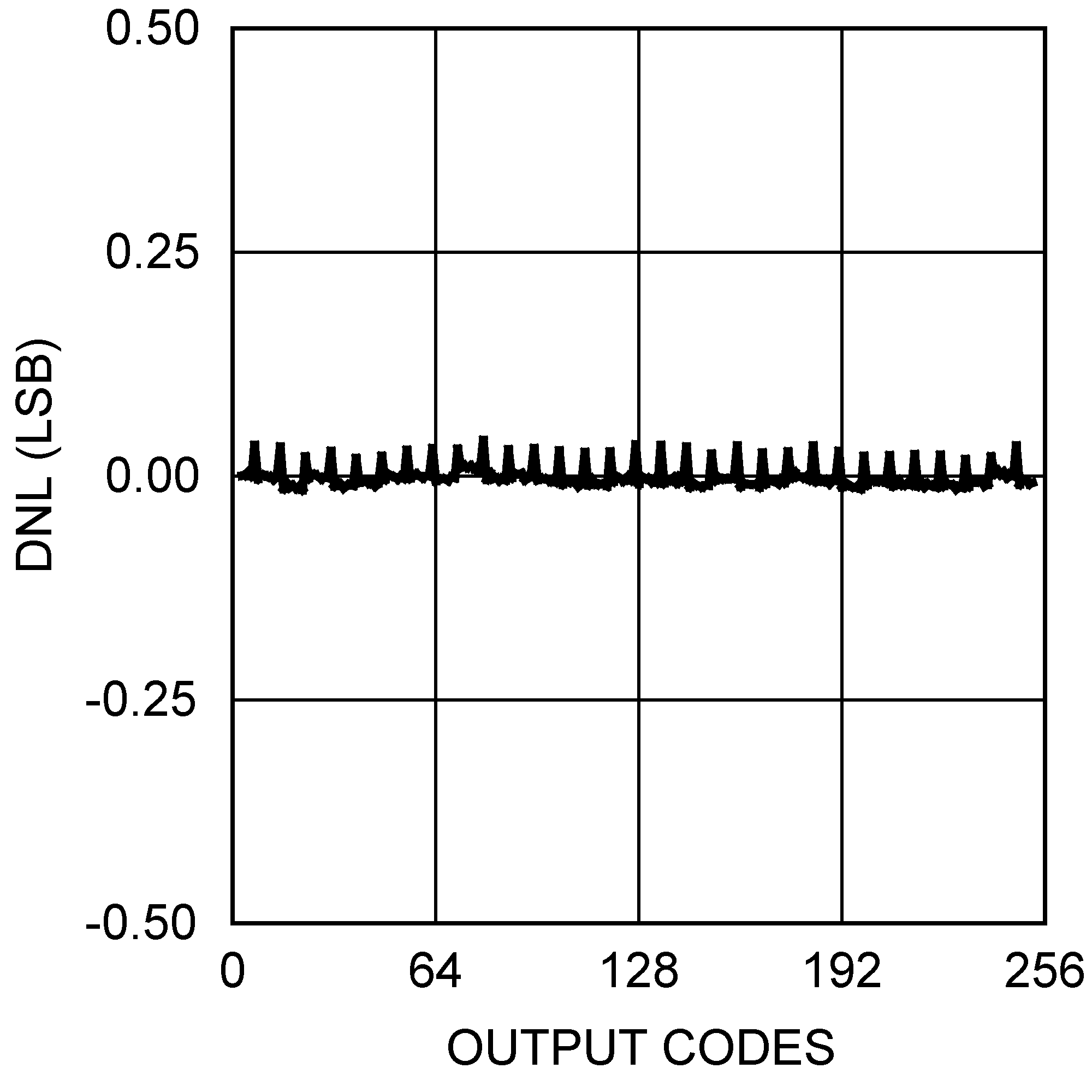

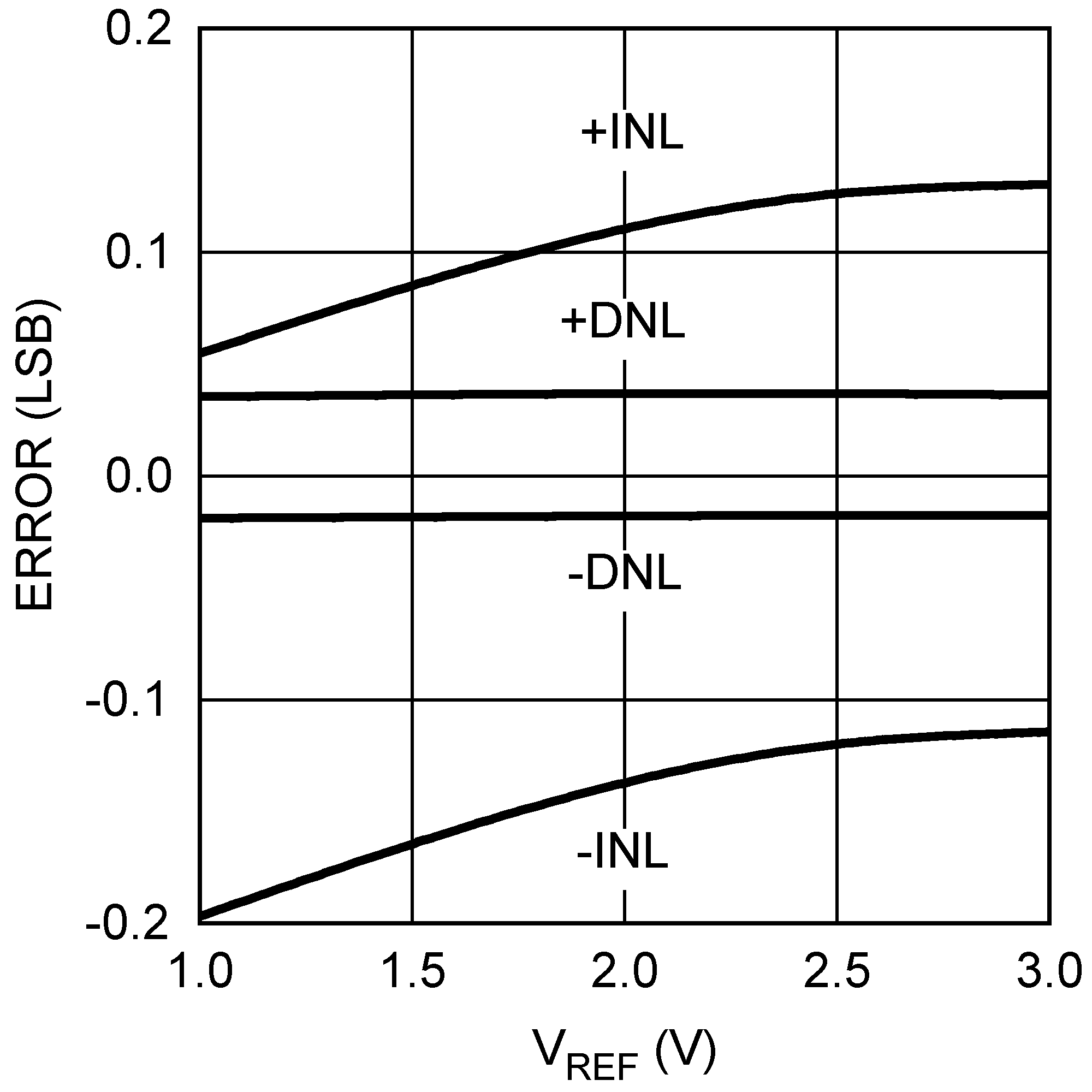

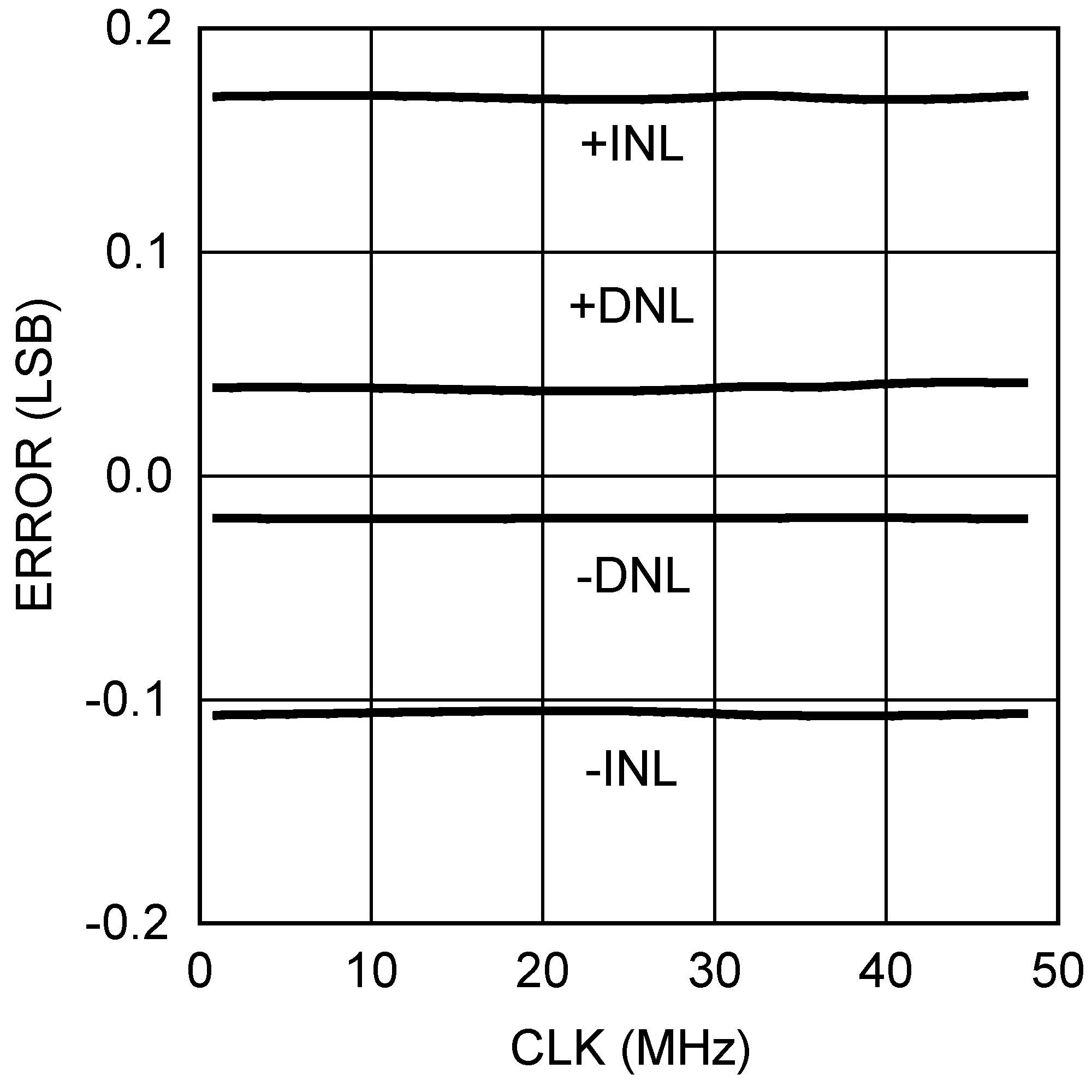

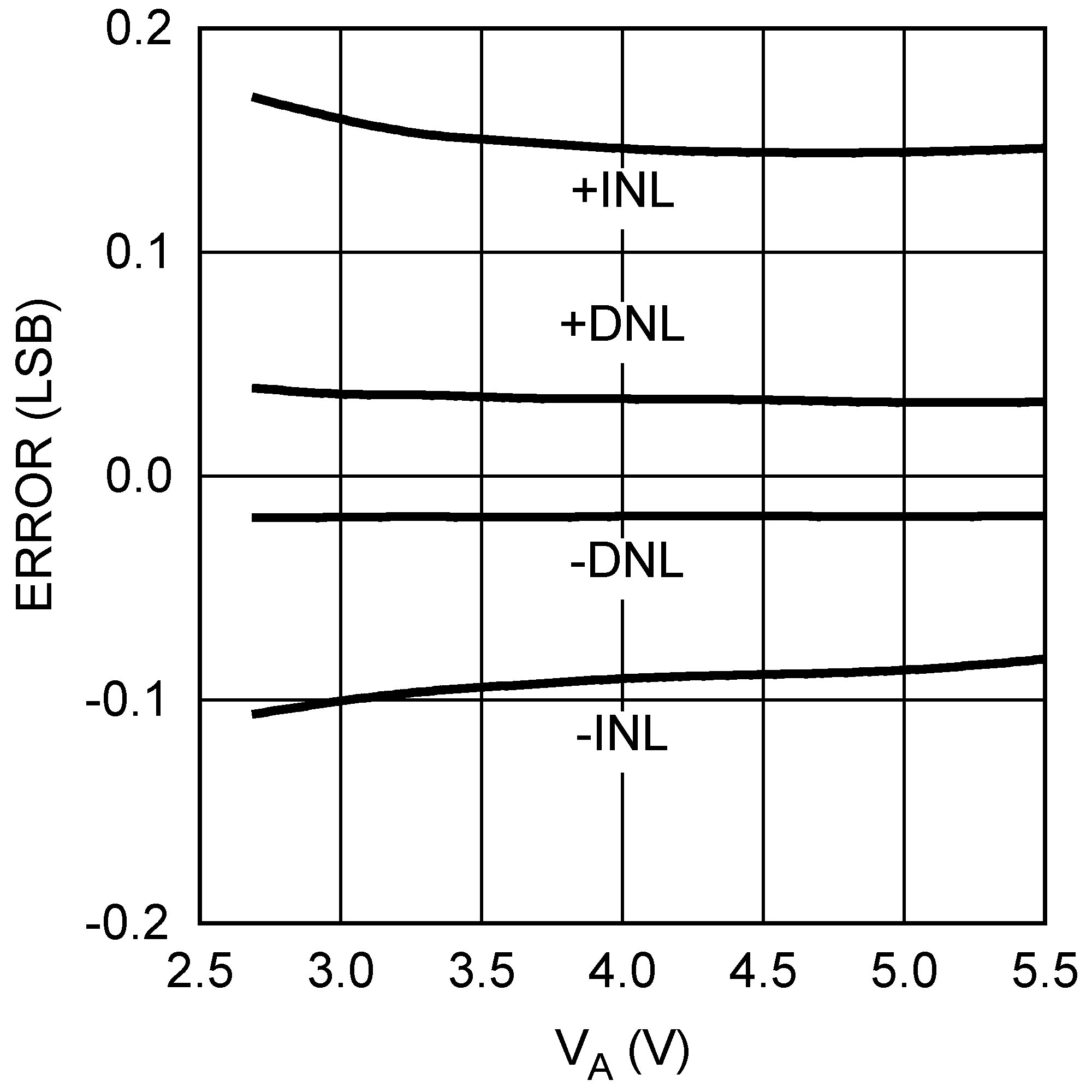

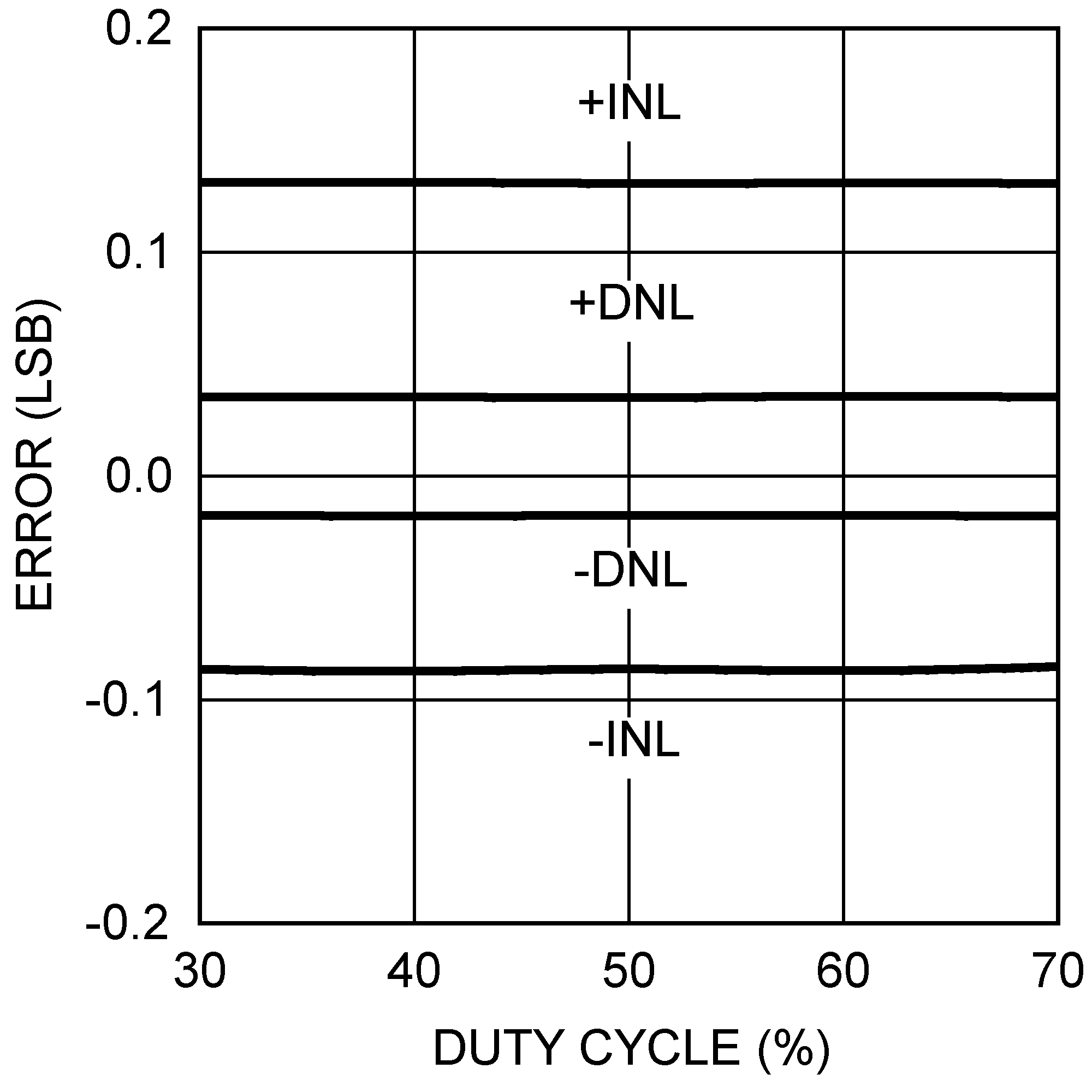

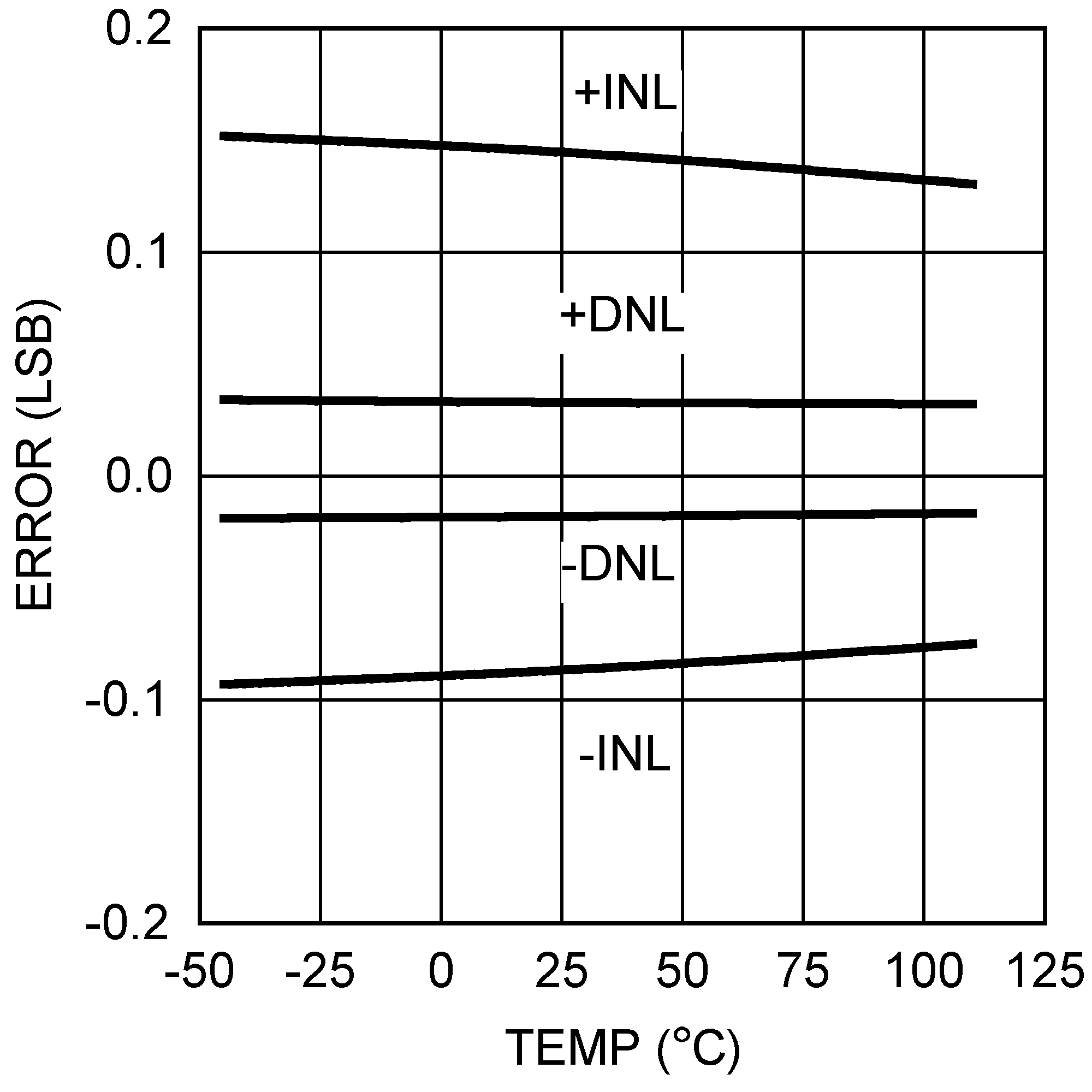

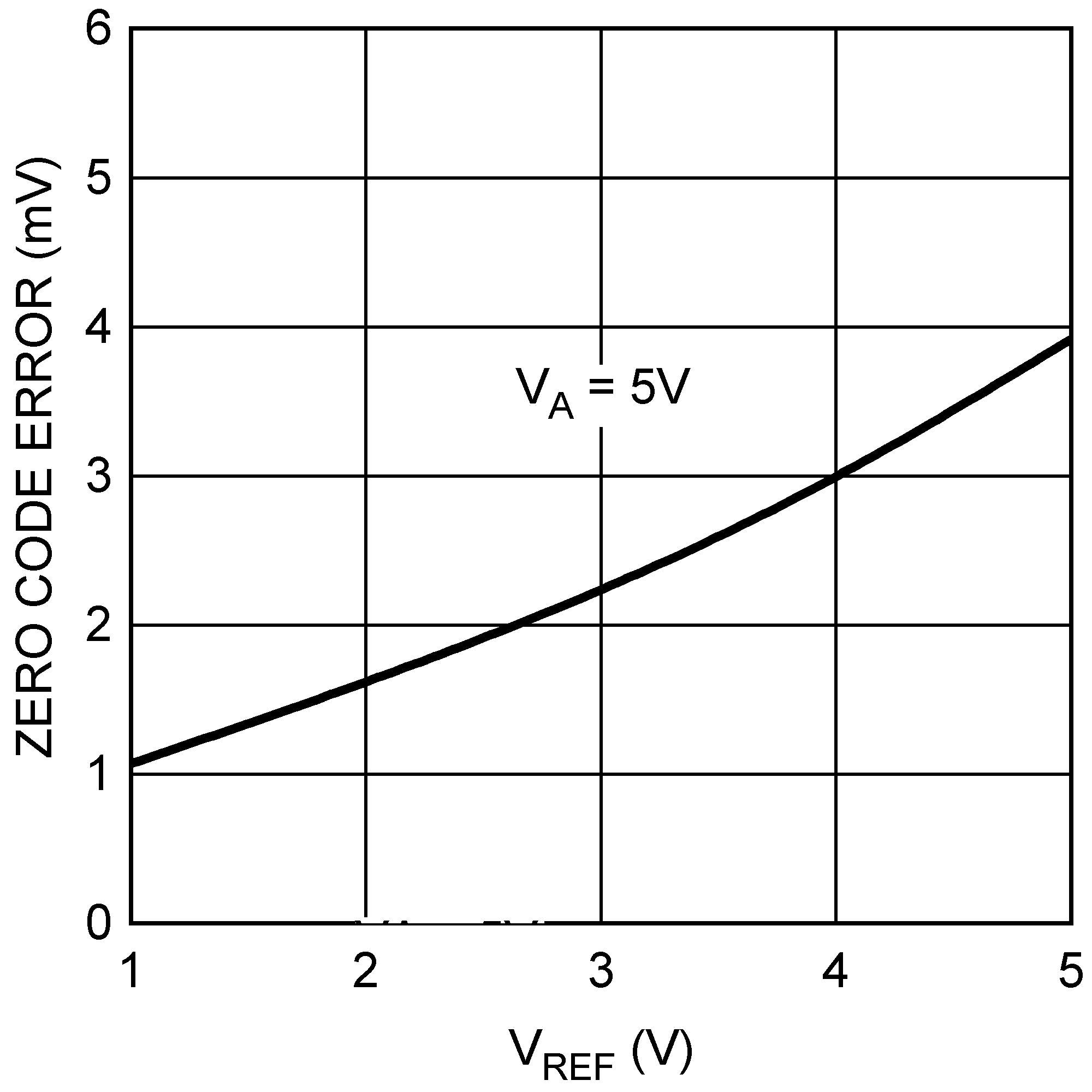

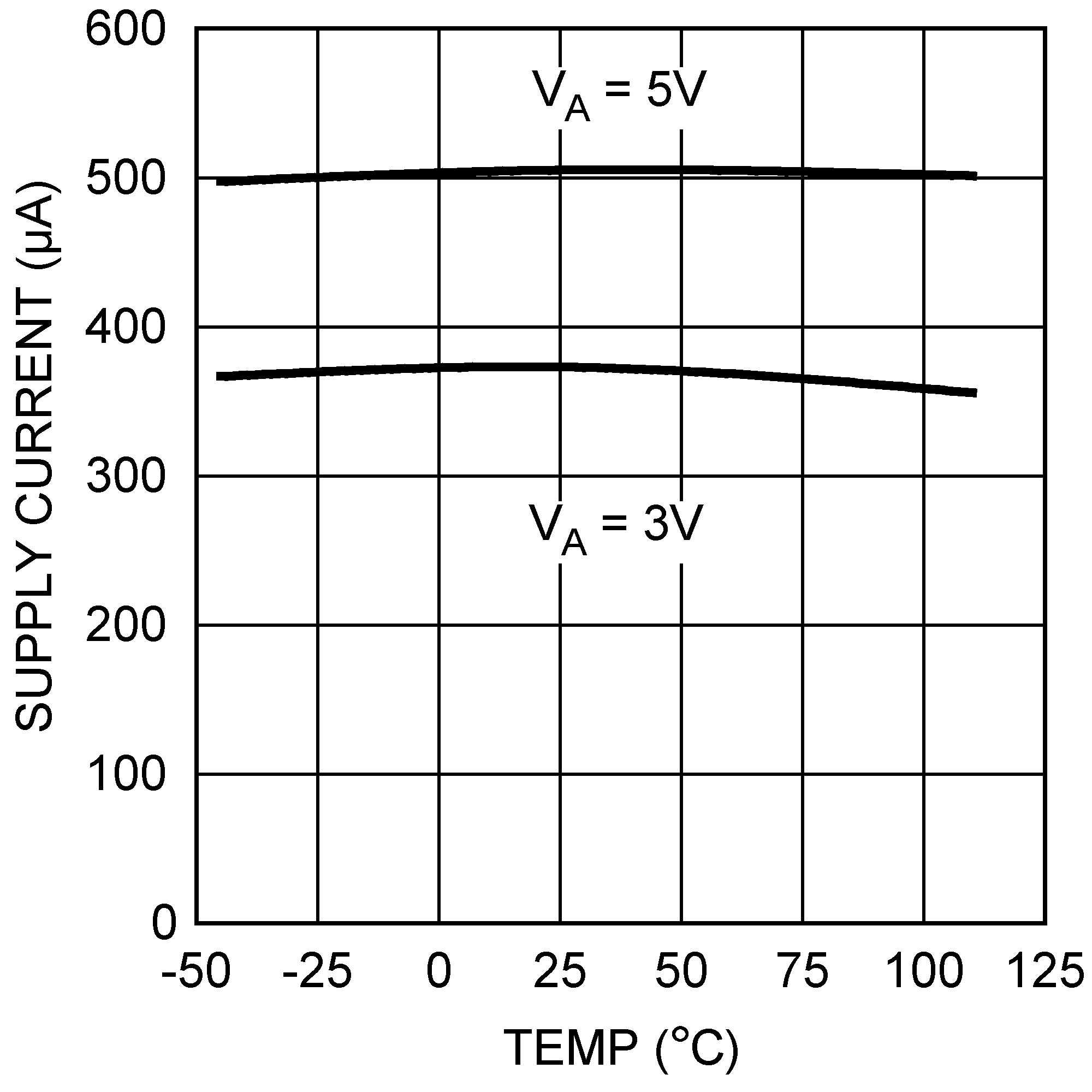

7.7 Typical Characteristics

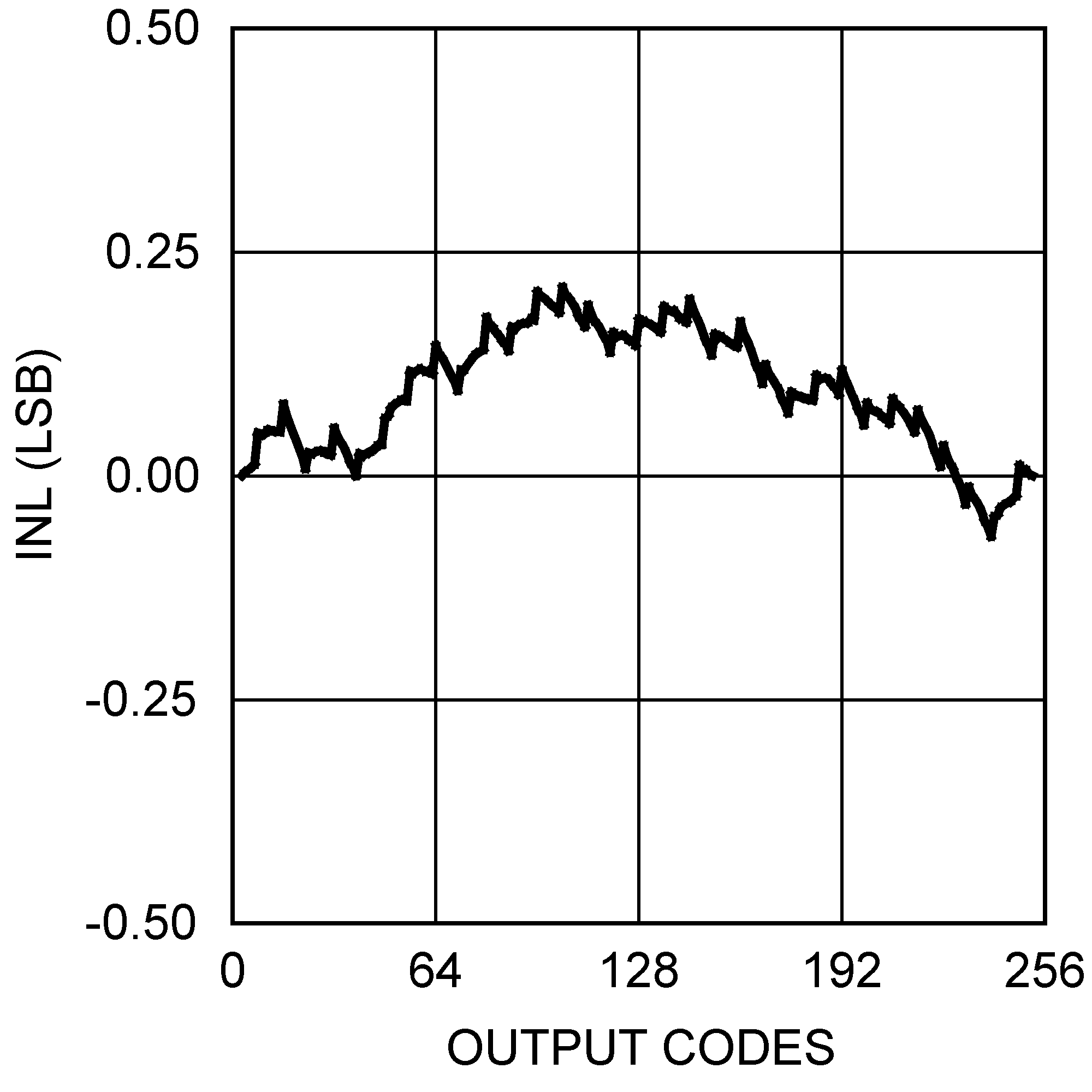

VREF = VA, fSCLK = 30 MHz, TA = 25°C, Input Code Range 3 to 252, unless otherwise stated Figure 3. INL at VA = 3 V

Figure 3. INL at VA = 3 V

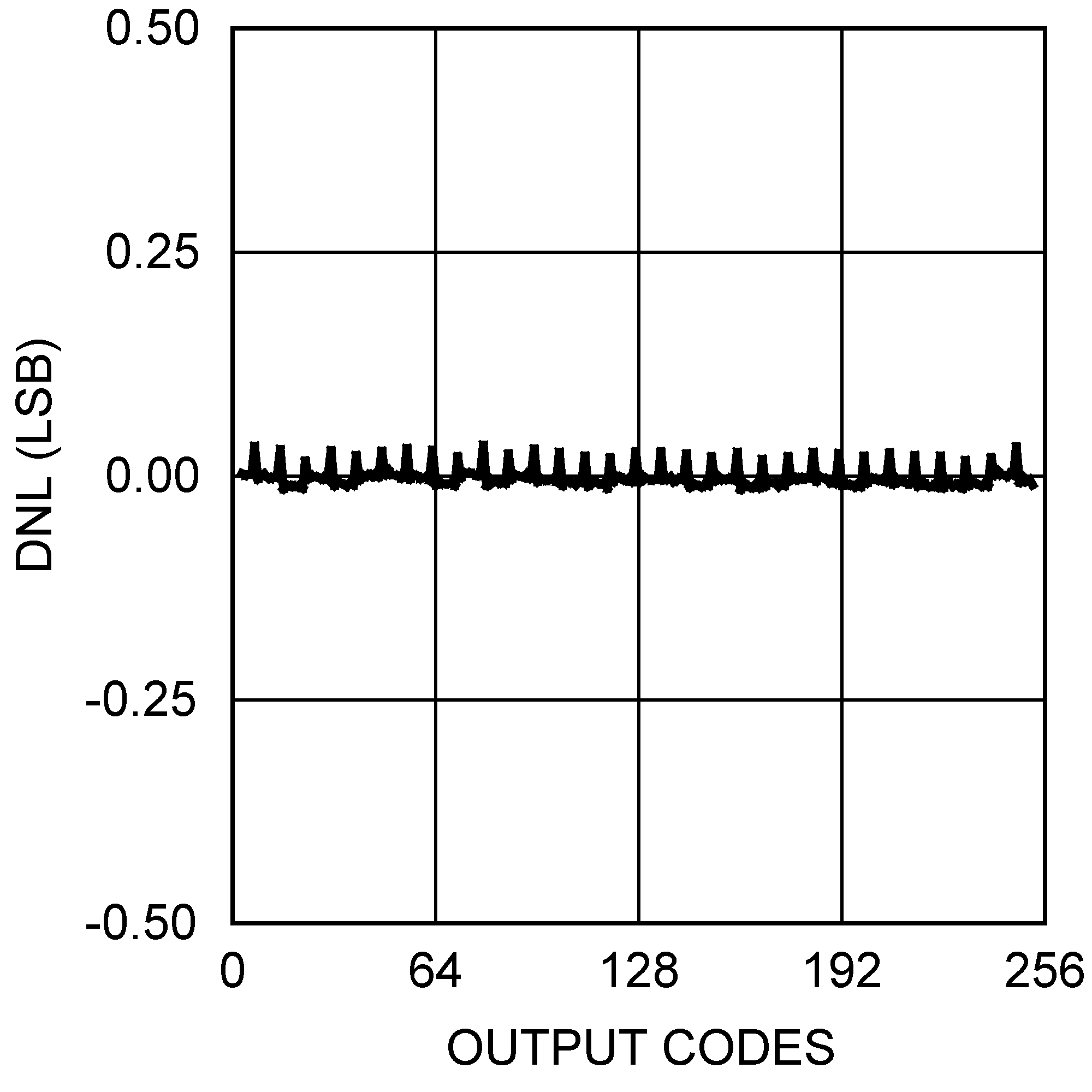

Figure 5. DNL at VA = 3 V

Figure 5. DNL at VA = 3 V

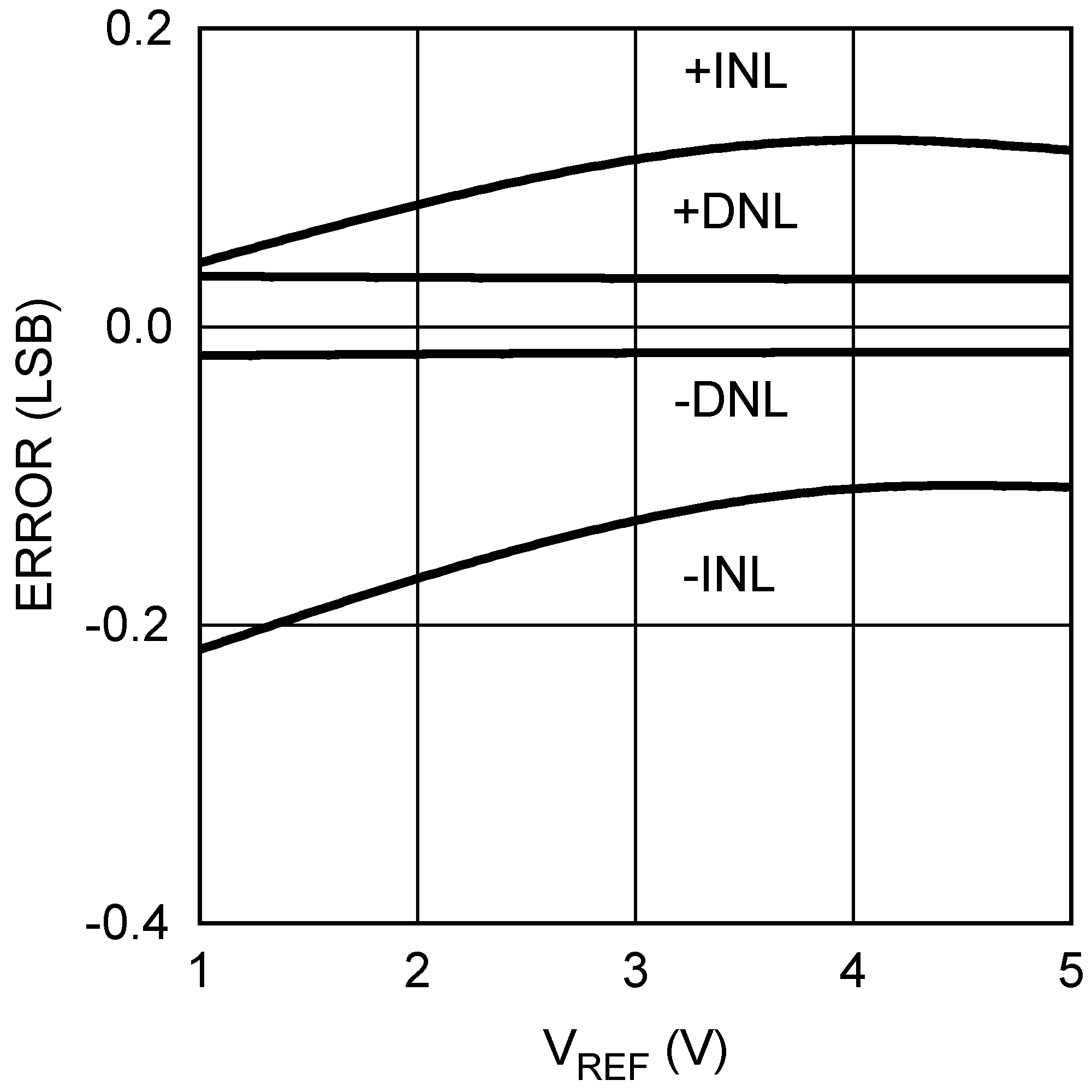

Figure 7. INL/DNL vs VREFIN at VA = 3 V

Figure 7. INL/DNL vs VREFIN at VA = 3 V

Figure 9. INL/DNL vs fSCLK at VA = 2.7 V

Figure 9. INL/DNL vs fSCLK at VA = 2.7 V

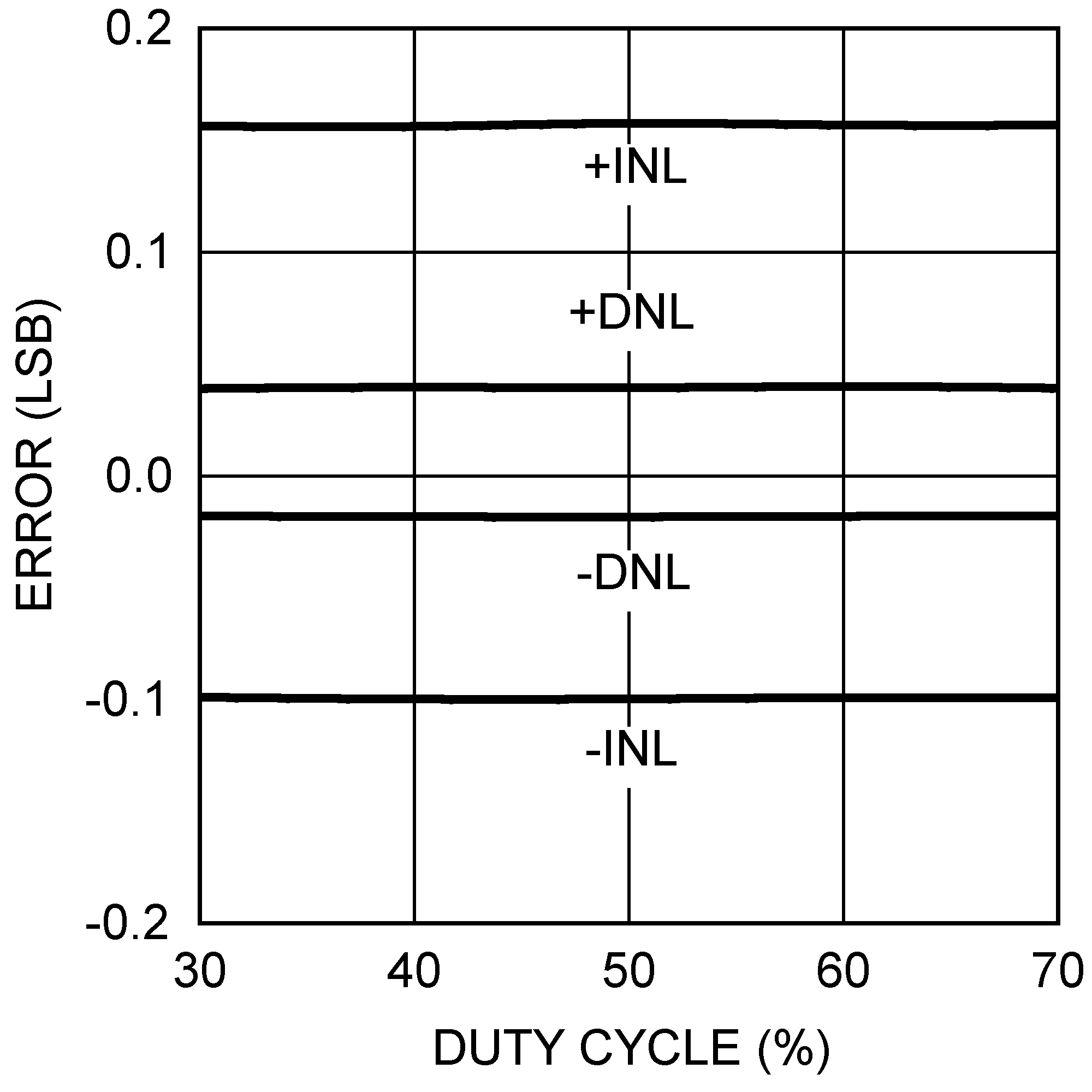

Figure 11. INL/DNL vs Clock Duty Cycle at VA = 3 V

Figure 11. INL/DNL vs Clock Duty Cycle at VA = 3 V

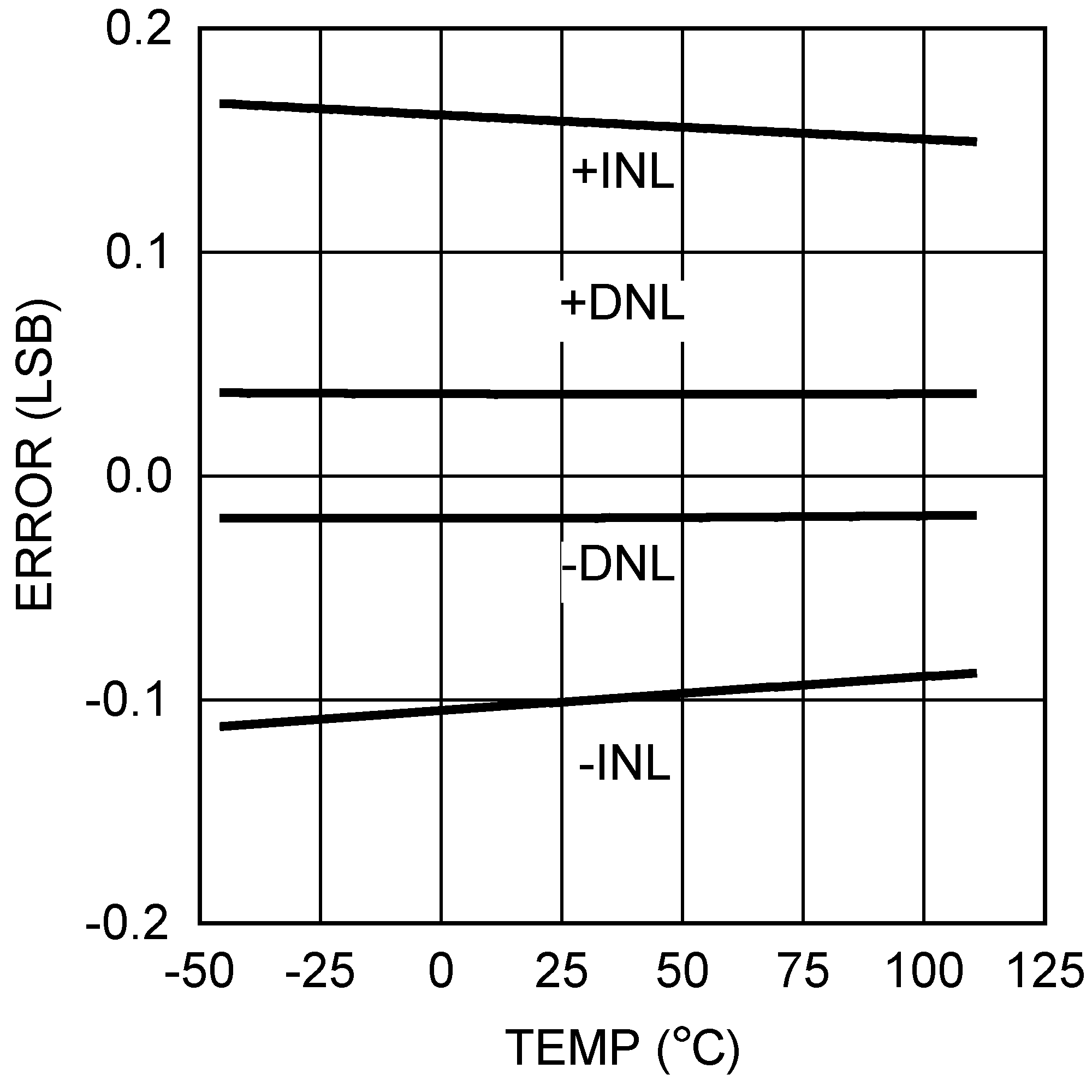

Figure 13. INL/DNL vs Temperature at VA = 3 V

Figure 13. INL/DNL vs Temperature at VA = 3 V

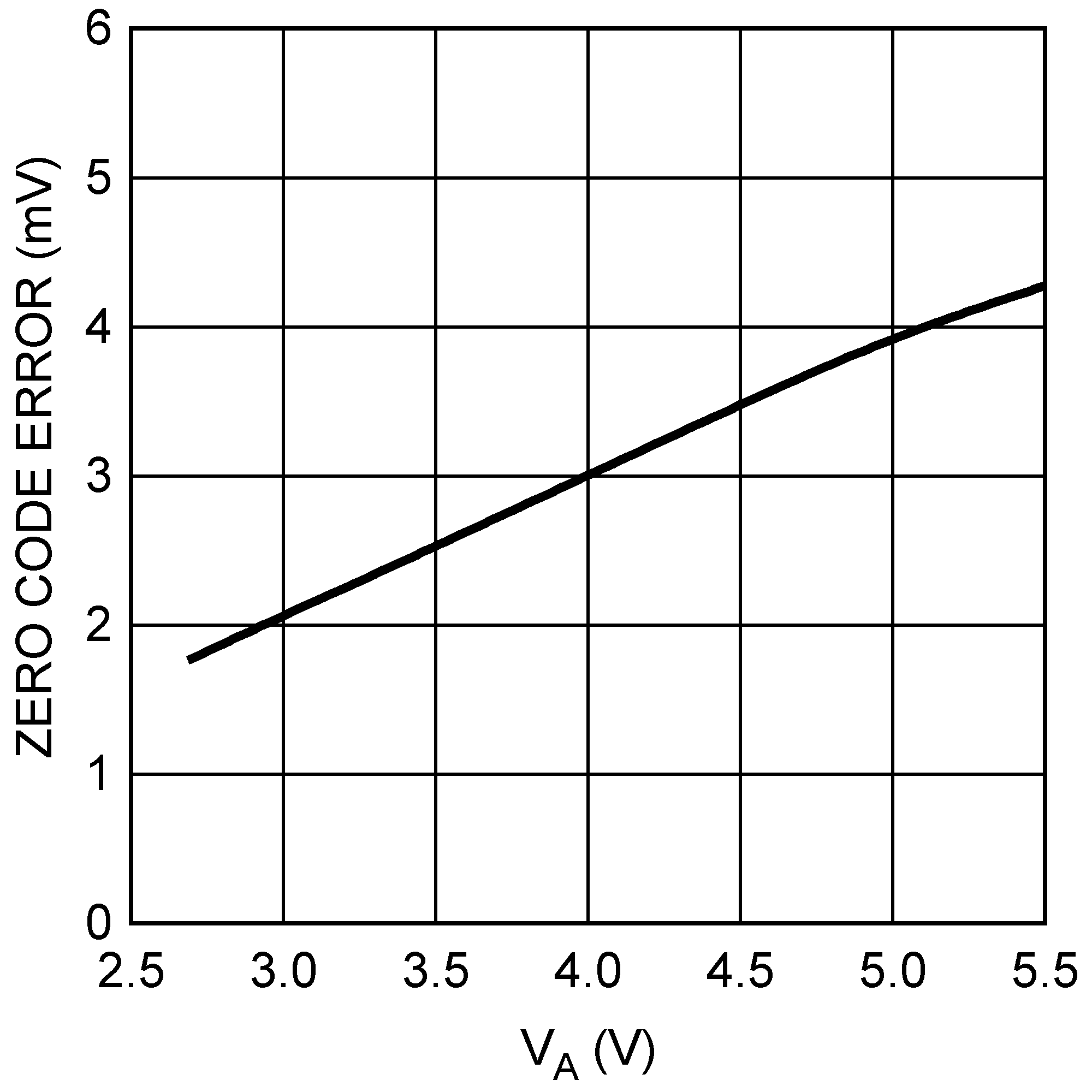

Figure 15. Zero Code Error vs VA

Figure 15. Zero Code Error vs VA

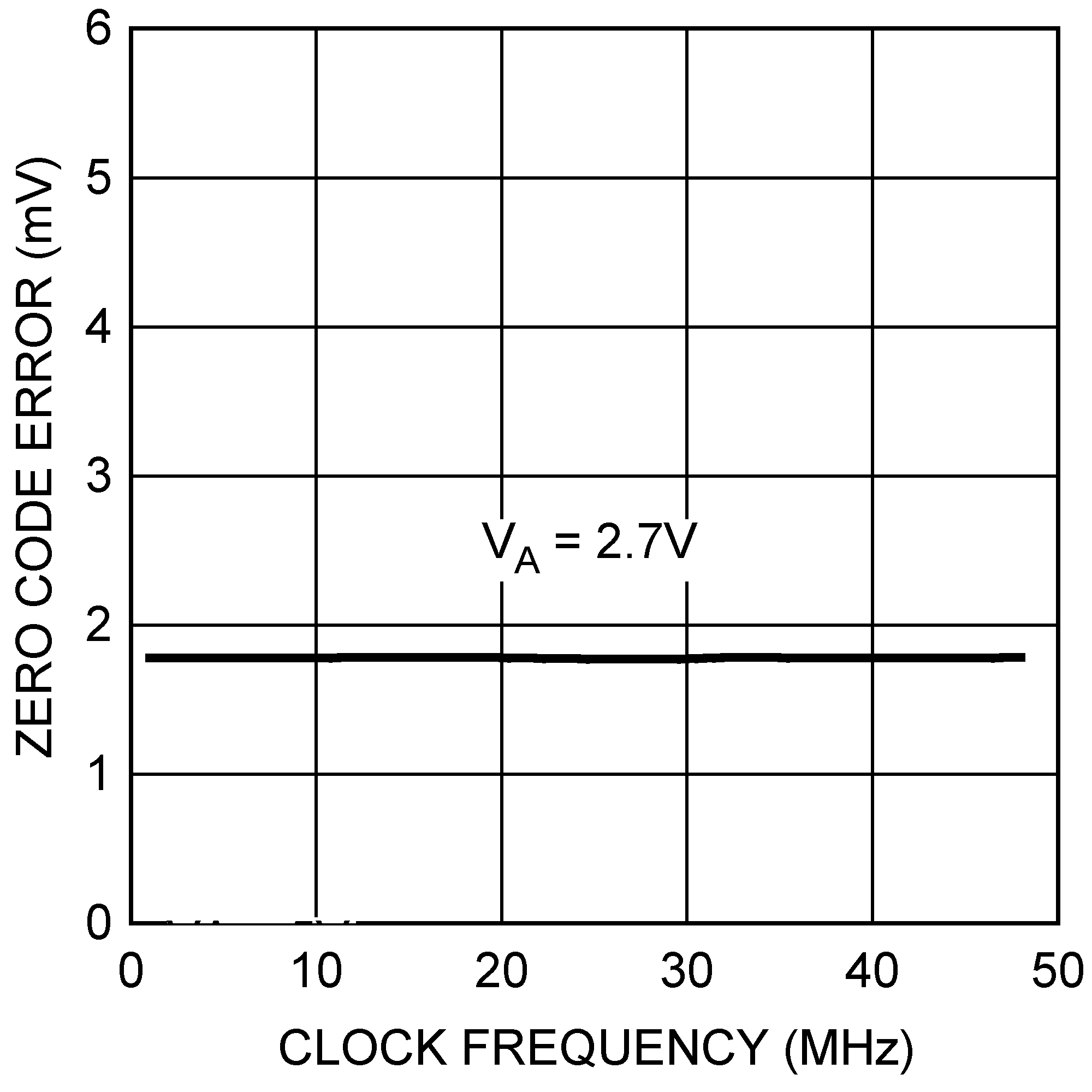

Figure 17. Zero Code Error vs fSCLK

Figure 17. Zero Code Error vs fSCLK

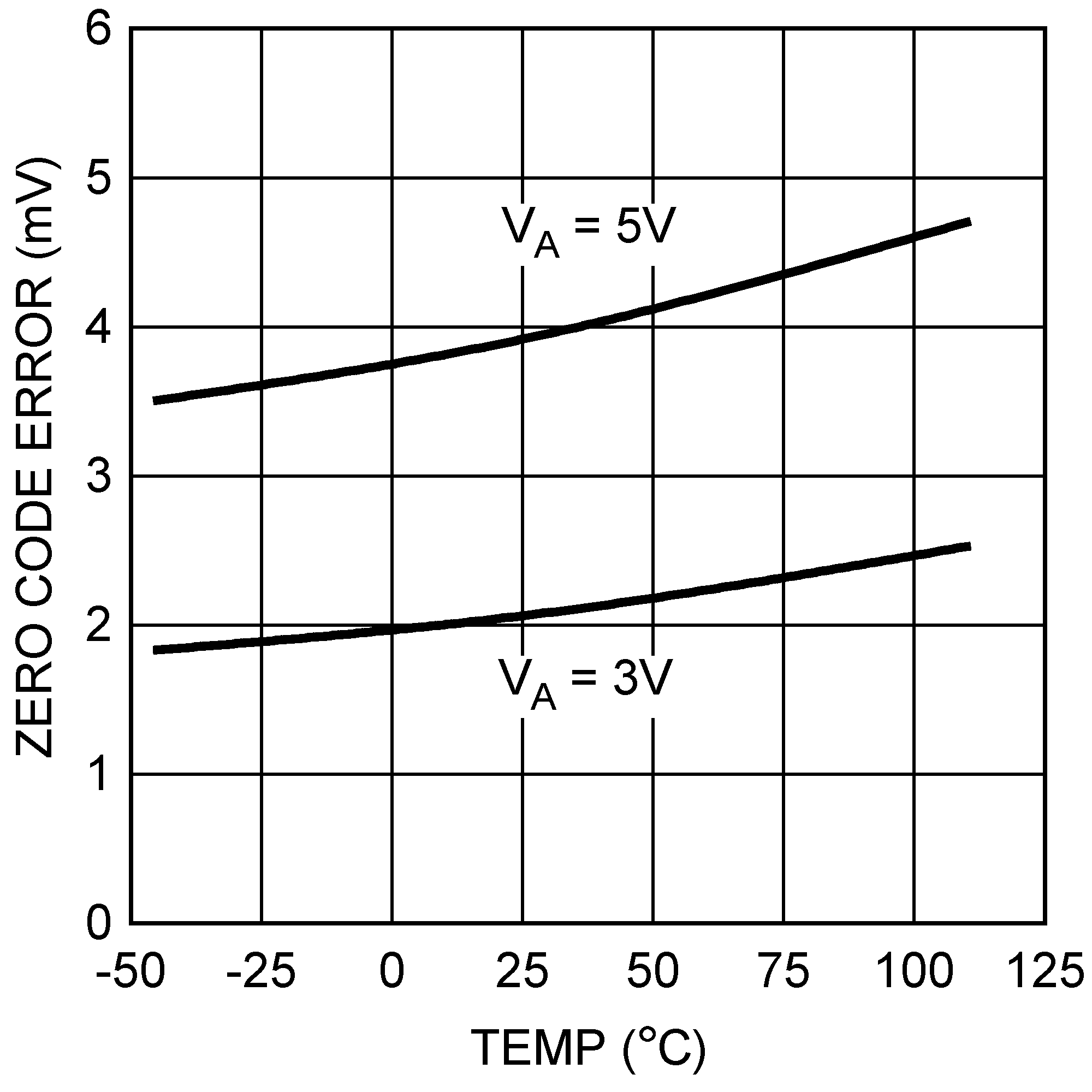

Figure 19. Zero Code Error vs Temperature

Figure 19. Zero Code Error vs Temperature

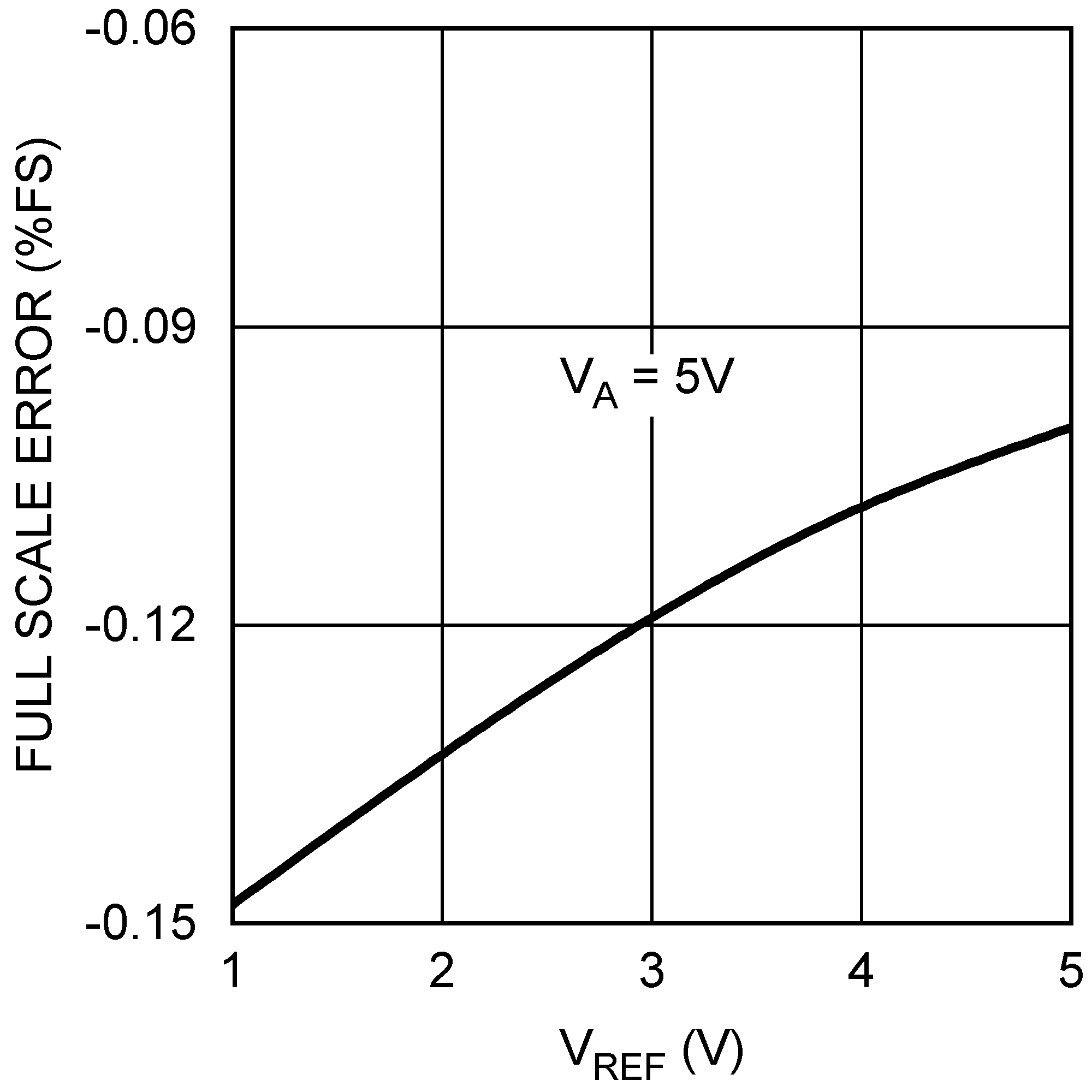

Figure 21. Full-Scale Error vs VREFIN

Figure 21. Full-Scale Error vs VREFIN

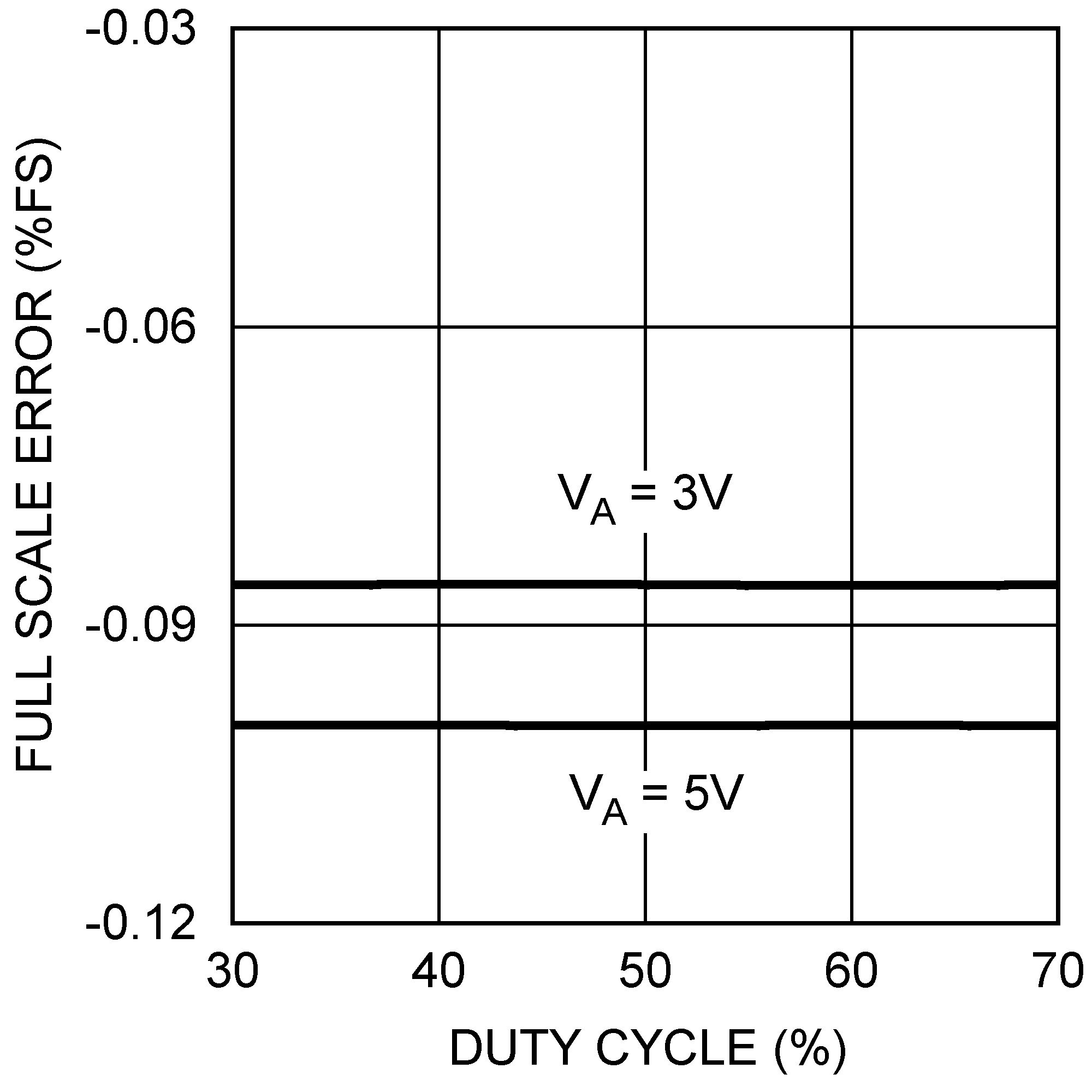

Figure 23. Full-Scale Error vs Clock Duty Cycle

Figure 23. Full-Scale Error vs Clock Duty Cycle

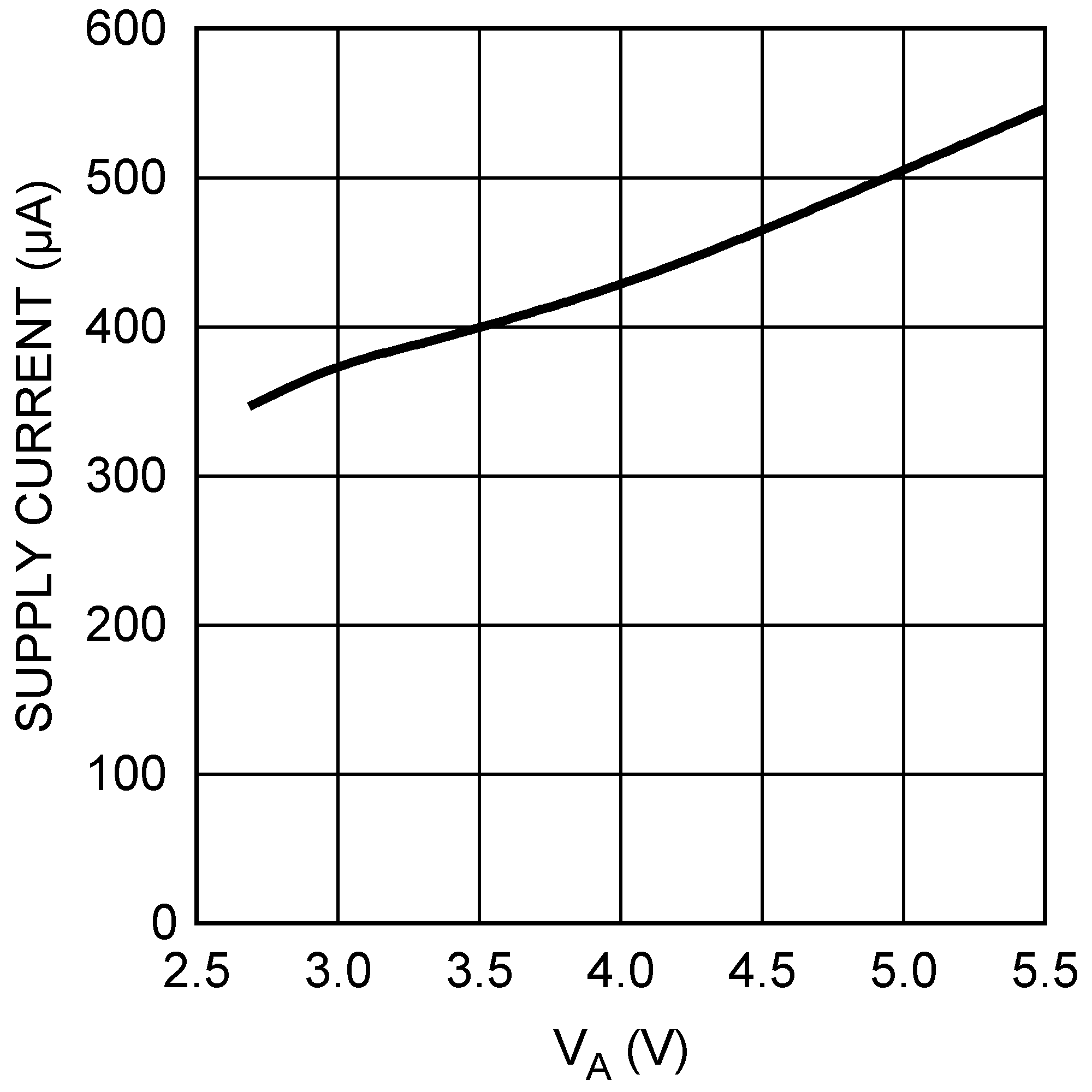

Figure 25. Supply Current vs VA

Figure 25. Supply Current vs VA

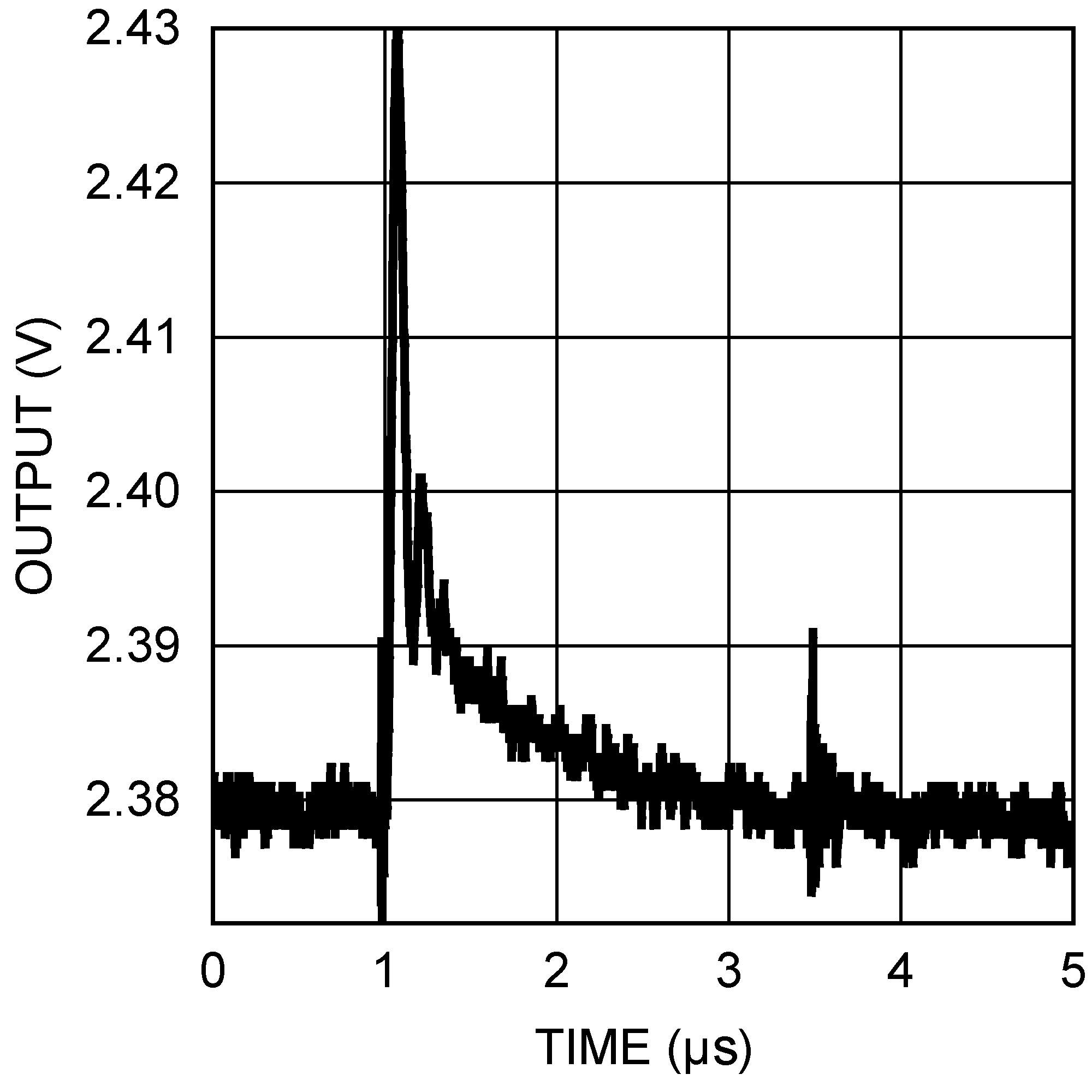

Figure 27. 5V Glitch Response

Figure 27. 5V Glitch Response

Figure 4. INL at VA = 5 V

Figure 4. INL at VA = 5 V

Figure 6. DNL at VA = 5 V

Figure 6. DNL at VA = 5 V

Figure 8. INL/DNL vs VREFIN at VA = 5 V

Figure 8. INL/DNL vs VREFIN at VA = 5 V

Figure 10. INL/DNL vs VA

Figure 10. INL/DNL vs VA

Figure 12. INL/DNL vs Clock Duty Cycle at VA = 5 V

Figure 12. INL/DNL vs Clock Duty Cycle at VA = 5 V

Figure 14. INL/DNL vs Temperature at VA = 5 V

Figure 14. INL/DNL vs Temperature at VA = 5 V

Figure 16. Zero Code Error vs VREFIN

Figure 16. Zero Code Error vs VREFIN

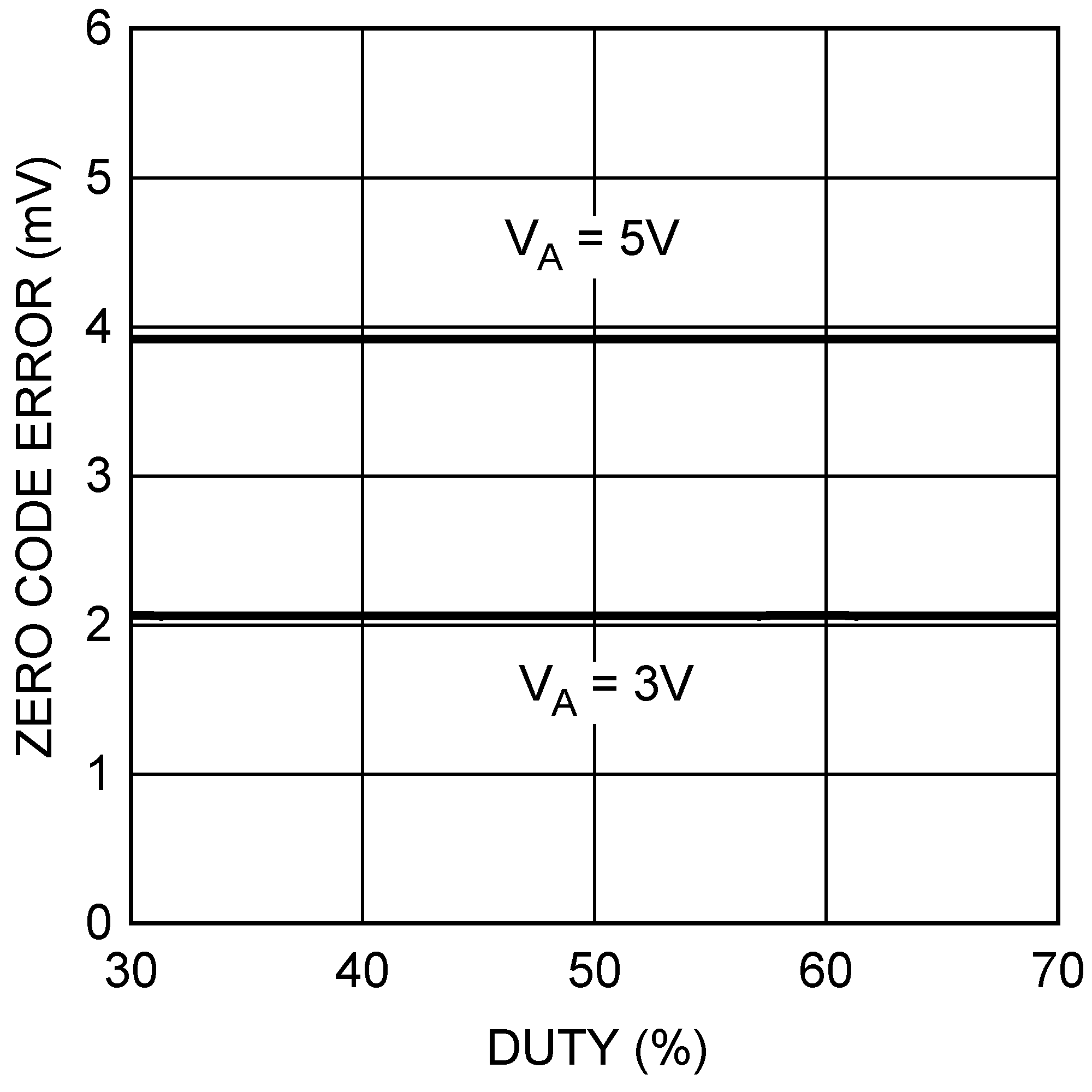

Figure 18. Zero Code Error vs Clock Duty Cycle

Figure 18. Zero Code Error vs Clock Duty Cycle

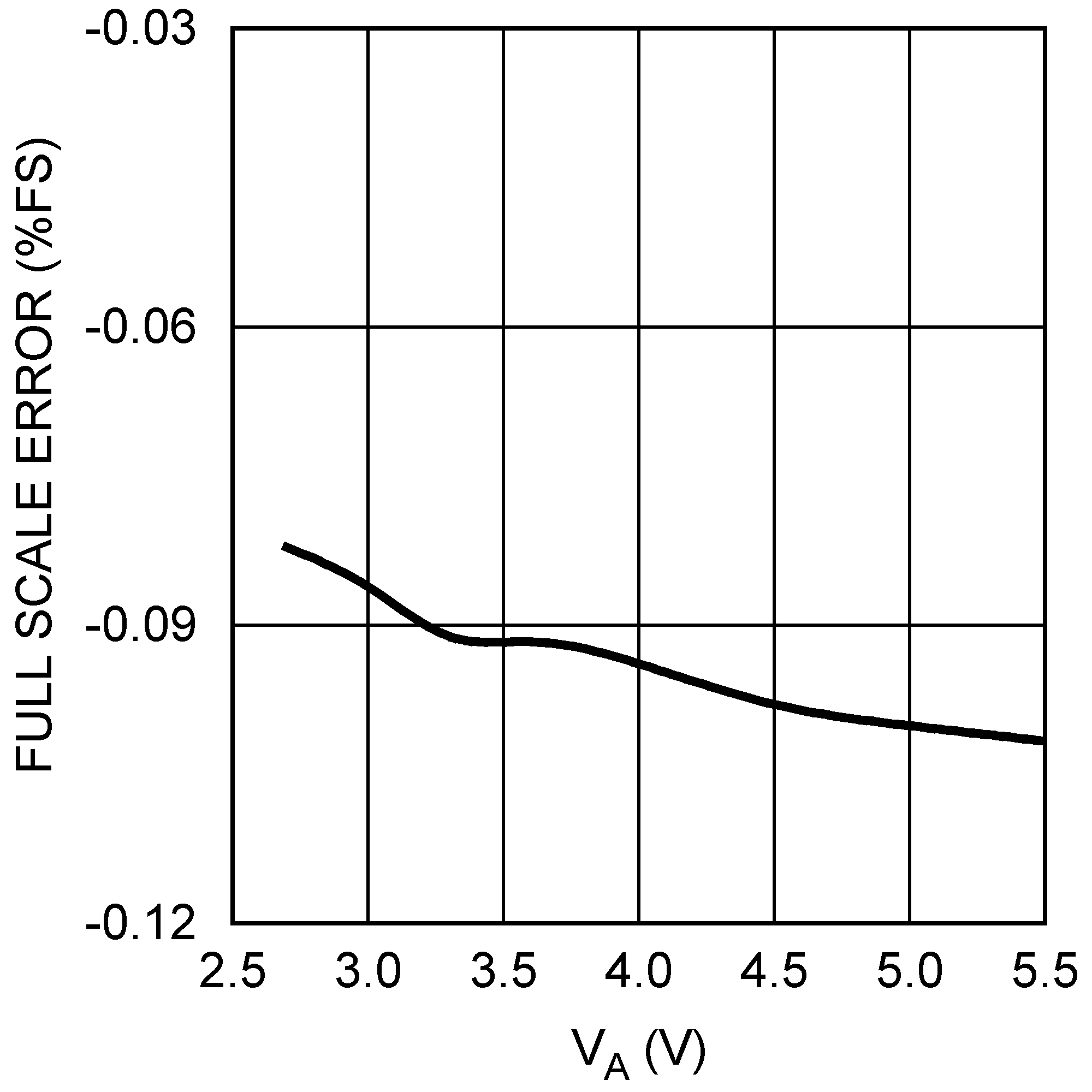

Figure 20. Full-Scale Error vs VA

Figure 20. Full-Scale Error vs VA

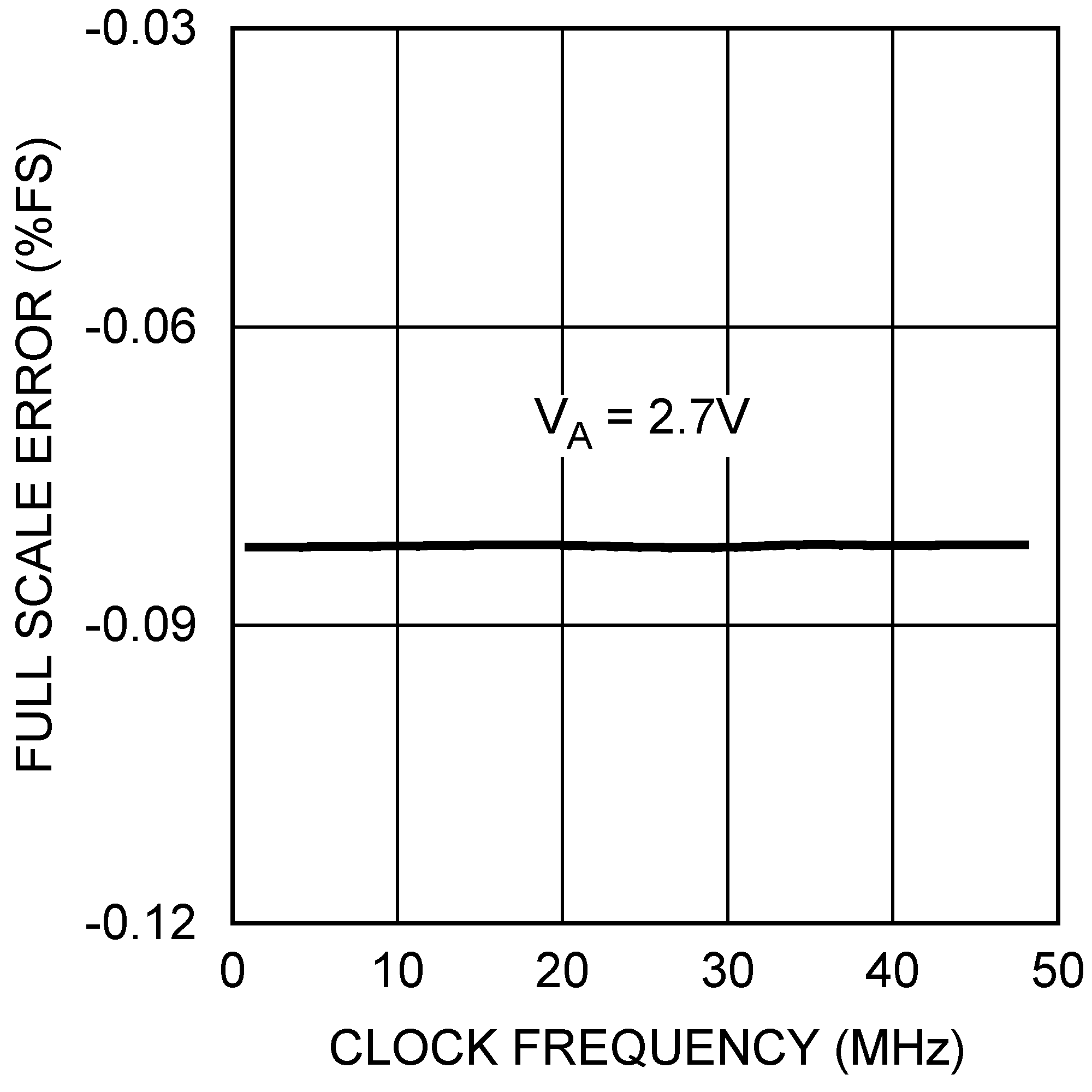

Figure 22. Full-Scale Error vs fSCLK

Figure 22. Full-Scale Error vs fSCLK

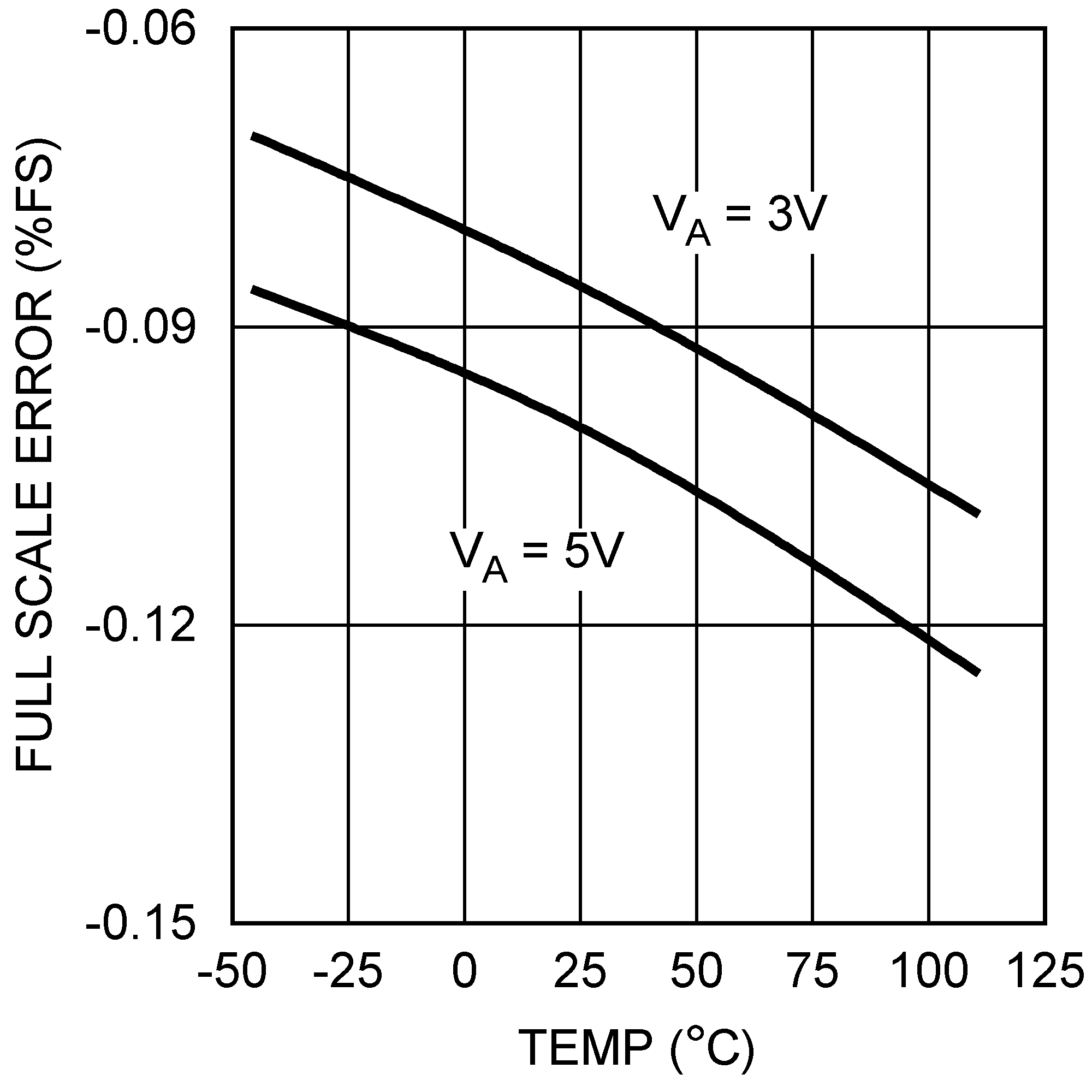

Figure 24. Full-Scale Error vs Temperature

Figure 24. Full-Scale Error vs Temperature

Figure 26. Supply Current vs Temperature

Figure 26. Supply Current vs Temperature

Figure 28. Power-On Reset

Figure 28. Power-On Reset