ZHCSNV9B May 2023 – March 2024 DAC39RF10 , DAC39RFS10

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 器件比较

- 5 引脚配置和功能

- 6 规格

- 7 详细说明

- 8 应用和实施

- 9 器件和文档支持

- 10修订历史记录

- 11机械、封装和可订购信息

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

订购信息

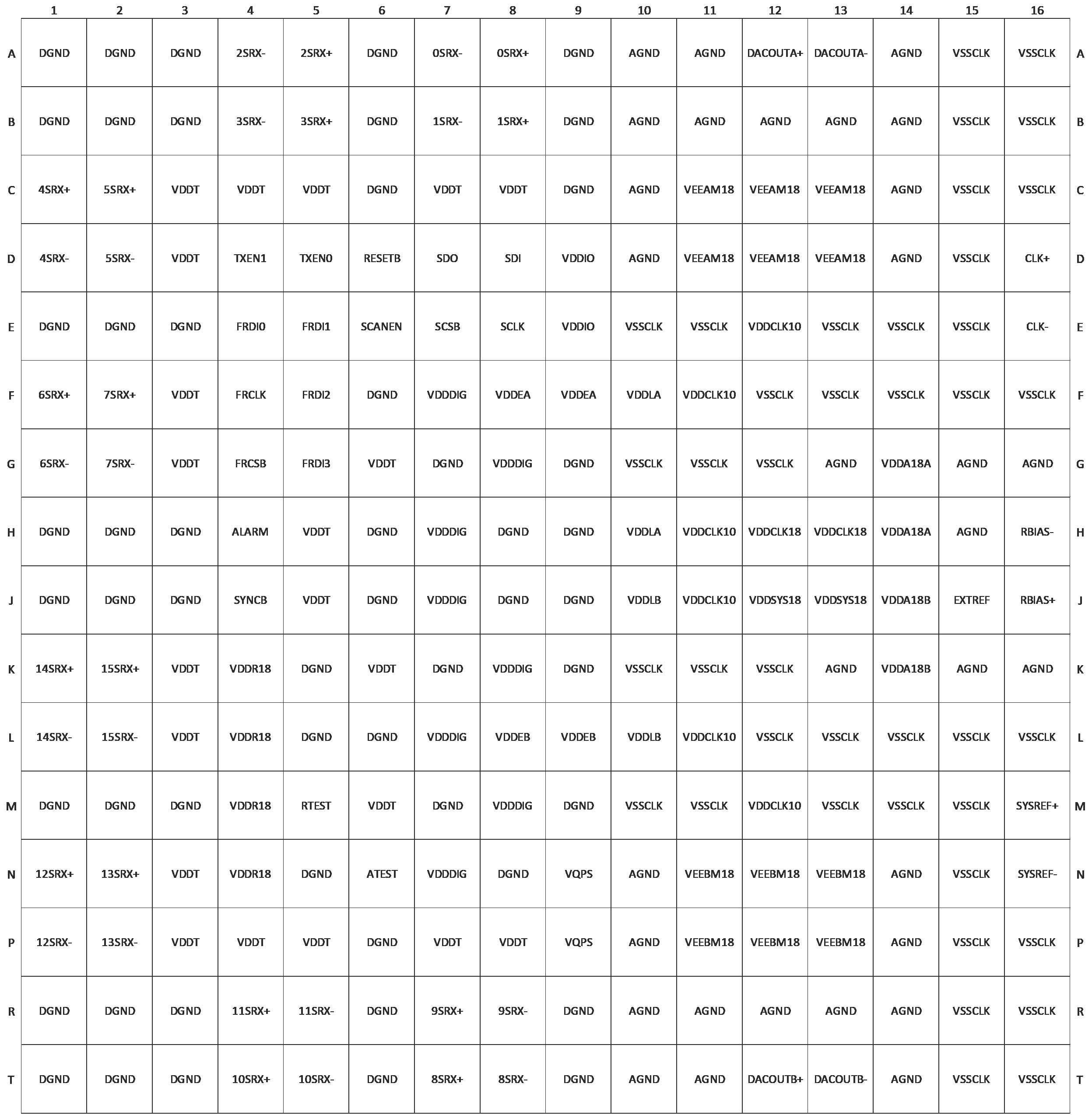

5 引脚配置和功能

图 5-1 ACK 封装,间距为 1mm 的 256 焊球覆晶 BGA,顶视图

图 5-1 ACK 封装,间距为 1mm 的 256 焊球覆晶 BGA,顶视图表 5-1 引脚功能

| 引脚 | I/O | 说明 | |

|---|---|---|---|

| 名称 | COORD | ||

| DAC 输出 | |||

| DACOUTA- | A13 | O | DAC 通道 A 模拟输出负极端子。输出电压必须符合 DAC 合规电压才能保持指定的性能。 |

| DACOUTA+ | A12 | O | DAC 通道 A 模拟输出正极端子。输出电压必须符合 DAC 合规电压才能保持指定的性能。 |

| DACOUTB- | T13 | O | DAC 通道 B 模拟输出负极端子。输出电压必须符合 DAC 合规电压才能保持指定的性能。在单通道器件中不可用。 |

| DACOUTB+ | T12 | O | DAC 通道 B 模拟输出正极端子。输出电压必须符合 DAC 合规电压才能保持指定的性能。在单通道器件中不可用。 |

| 差分时钟和 SYSREF 输入 | |||

| CLK- | E16 | I | 器件时钟输入负极端子。CLK+ 和 CLK- 之间有一个内部 100Ω 差分端接。该输入为自偏置输入,应与时钟源进行交流耦合。 |

| CLK+ | D16 | I | 器件时钟输入正极端子。CLK+ 和 CLK- 之间有一个内部 100Ω 差分端接。该输入为自偏置输入,应与时钟源进行交流耦合。 |

| SYSREF- | N16 | I | 差分 JESD204C SYSREF 输入负极端子。SYSREF+ 和 SYSREF– 之间有一个内部 100Ω 差分端接。 |

| SYSREF+ | M16 | I | 差分 JESD204C SYSREF 输入负极端子。SYSREF+ 和 SYSREF– 之间有一个内部 100Ω 差分端接。 |

| 串行器/解串器接口 | |||

| 0SRX- | A7 | I | 串行器/解串器通道 0 负输入。包括封装中交流耦合串联电容器和到 0SRX+ 的 100Ω 内部端接。 |

| 0SRX+ | A8 | I | 串行器/解串器通道 0 正输入。包括封装中交流耦合串联电容器和到 0SRX- 的 100Ω 内部端接。 |

| 1SRX- | B7 | I | 串行器/解串器通道 1 负输入。包括封装中交流耦合串联电容器和到 1SRX+ 的 100Ω 内部端接。 |

| 1SRX+ | B8 | I | 串行器/解串器通道 1 正输入。包括封装中交流耦合串联电容器和到 1SRX- 的 100Ω 内部端接。 |

| 2SRX- | A4 | I | 串行器/解串器通道 2 负输入。包括封装中交流耦合串联电容器和到 2SRX+ 的 100Ω 内部端接。 |

| 2SRX+ | A5 | I | 串行器/解串器通道 2 正输入。包括封装中交流耦合串联电容器和到 2SRX- 的 100Ω 内部端接。 |

| 3SRX- | B4 | I | 串行器/解串器通道 3 负输入。包括封装中交流耦合串联电容器和到 3SRX+ 的 100Ω 内部端接。 |

| 3SRX+ | B5 | I | 串行器/解串器通道 3 正输入。包括封装中交流耦合串联电容器和到 3SRX- 的 100Ω 内部端接。 |

| 4SRX- | D1 | I | 串行器/解串器通道 4 负输入。包括封装中交流耦合串联电容器和到 4SRX+ 的 100Ω 内部端接。 |

| 4SRX+ | C1 | I | 串行器/解串器通道 4 正输入。包括封装中交流耦合串联电容器和到 4SRX- 的 100Ω 内部端接。 |

| 5SRX- | D2 | I | 串行器/解串器通道 5 负输入。包括封装中交流耦合串联电容器和到 5SRX+ 的 100Ω 内部端接。 |

| 5SRX+ | C2 | I | 串行器/解串器通道 5 正输入。包括封装中交流耦合串联电容器和到 5SRX- 的 100Ω 内部端接。 |

| 6SRX- | G1 | I | 串行器/解串器通道 6 负输入。包括封装中交流耦合串联电容器和到 6SRX+ 的 100Ω 内部端接。 |

| 6SRX+ | F1 | I | 串行器/解串器通道 6 正输入。包括封装中交流耦合串联电容器和到 6SRX- 的 100Ω 内部端接。 |

| 7SRX- | G2 | I | 串行器/解串器通道 7 负输入。包括封装中交流耦合串联电容器和到 7SRX+ 的 100Ω 内部端接。 |

| 7SRX+ | F2 | I | 串行器/解串器通道 7 正输入。包括封装中交流耦合串联电容器和到 7SRX- 的 100Ω 内部端接。 |

| 8SRX- | T8 | I | 串行器/解串器通道 8 负输入。包括封装中交流耦合串联电容器和到 8SRX+ 的 100Ω 内部端接。 |

| 8SRX+ | T7 | I | 串行器/解串器通道 8 正输入。包括封装中交流耦合串联电容器和到 8SRX- 的 100Ω 内部端接。 |

| 9SRX- | R8 | I | 串行器/解串器通道 9 负输入。包括封装中交流耦合串联电容器和到 9SRX+ 的 100Ω 内部端接。 |

| 9SRX+ | R7 | I | 串行器/解串器通道 9 正输入。包括封装中交流耦合串联电容器和到 9SRX- 的 100Ω 内部端接。 |

| 10SRX- | T5 | I | 串行器/解串器通道 10 负输入。包括封装中交流耦合串联电容器和到 10SRX+ 的 100Ω 内部端接。 |

| 10SRX+ | T4 | I | 串行器/解串器通道 10 正输入。包括封装中交流耦合串联电容器和到 10SRX- 的 100Ω 内部端接。 |

| 11SRX- | R5 | I | 串行器/解串器通道 11 负输入。包括封装中交流耦合串联电容器和到 11SRX+ 的 100Ω 内部端接。 |

| 11SRX+ | R4 | I | 串行器/解串器通道 11 正输入。包括封装中交流耦合串联电容器和到 11SRX- 的 100Ω 内部端接。 |

| 12SRX- | P1 | I | 串行器/解串器通道 12 负输入。包括封装中交流耦合串联电容器和到 12SRX+ 的 100Ω 内部端接。 |

| 12SRX+ | N1 | I | 串行器/解串器通道 12 正输入。包括封装中交流耦合串联电容器和到 12SRX- 的 100Ω 内部端接。 |

| 13SRX- | P2 | I | 串行器/解串器通道 13 负输入。包括封装中交流耦合串联电容器和到 13SRX+ 的 100Ω 内部端接。 |

| 13SRX+ | N2 | I | 串行器/解串器通道 13 正输入。包括封装中交流耦合串联电容器和到 13SRX- 的 100Ω 内部端接。 |

| 14SRX- | L1 | I | 串行器/解串器通道 14 负输入。包括封装中交流耦合串联电容器和到 14SRX+ 的 100Ω 内部端接。 |

| 14SRX+ | K1 | I | 串行器/解串器通道 14 正输入。包括封装中交流耦合串联电容器和到 14SRX- 的 100Ω 内部端接。 |

| 15SRX- | L2 | I | 串行器/解串器通道 15 负输入。包括封装中交流耦合串联电容器和到 15SRX+ 的 100Ω 内部端接。 |

| 15SRX+ | K2 | I | 串行器/解串器通道 15 正输入。包括封装中交流耦合串联电容器和到 15SRX- 的 100Ω 内部端接。 |

| GPIO 函数 | |||

| ALARM | H4 | O | 当检测到内部未屏蔽警报时,ALARM 引脚有效。报警屏蔽由 ALM_MASK 寄存器设置。 |

| FRCLK | F4 | I | 快速重新配置接口时钟。 |

| FRCS | G4 | I | 快速重新配置接口芯片选择。内部上拉。 |

| FRDI0 | E4 | I | 快速重新配置接口数据位 0。 |

| FRDI1 | E5 | I | 快速重新配置接口数据位 1。 |

| FRDI2 | F5 | I | 快速重新配置接口数据位 2。 |

| FRDI3 | G5 | I | 快速重新配置接口数据位 3。 |

| RESET | D6 | I | 器件复位输入,低电平有效。必须在加电后切换。内部上拉。 |

| SCANEN | E6 | I |

仅供 TI 使用,可以保持未连接状态。内部下拉电阻。 |

| SCLK | E8 | I | 串行编程接口 (SPI) 时钟输入。 |

| SCS | E7 | I | 串行编程接口 (SPI) 器件选择输入,低电平有效。内部上拉。 |

| SDI | D8 | I |

串行编程接口 (SPI) 数据输入。 |

| SDO | D7 | O | 串行编程接口 (SPI) 数据输出。不读取 SPI 数据时具有高阻抗。 |

| SYNC | J4 | O | JESD204C SYNC 输出,低电平有效。 |

| TXEN0 | D5 | I |

通道 A 高电平有效输入的发送使能。必须使用寄存器 USE_TX_EN0 启用此引脚。当传输被禁用时,DAC 输出被强制为中间码(二进制补码为 0x0000)。内部上拉。 |

| TXEN1 | D4 | I |

通道 B 高电平有效输入的发送使能。必须使用寄存器 USE_TX_EN1 启用此引脚。当传输被禁用时,DAC 输出被强制为中间码(二进制补码为 0x0000)。内部上拉。 |

| 模拟功能 | |||

| ATEST | N6 | O | 模拟测试引脚。可在不使用时保持断开。 |

| EXTREF | J15 | I/O | 基准电压输出或输入,由 EXTREF_EN 寄存器字段确定。如果使用内部基准,则应将焊球通过 0.1uF 连接至 AGND。 |

| RBIAS- | H16 | O | 满量程输出电流偏置由从该端子连接到 RBIAS+ 的电阻器设置。 |

| RBIAS+ | J16 | O | 满量程输出电流偏置由从该端子连接到 RBIAS- 的电阻器设置。 |

| RTEST | M5 | O | 仅供 TI 使用。连接至 AGND。 |

| 电源 | |||

| VDDA18A | G14 H14 | I |

DAC 通道 A 的电源电压为 1.8V。可与 VDDA18B 搭配使用,但可能会降低通道间抗串扰 (XTALK) 性能。 |

| VDDA18B | J14 K14 | I | DAC 通道 A 的电源电压为 1.8V。可与 VDDA18A 搭配使用,但可能会降低通道间抗串扰 (XTALK) 性能。 |

| VDDCLK10 | F11 H11 J11 L11 E12 M12 | I | 内部采样时钟分配路径的 1.0V 电源电压。该电源上的噪声或杂散可能会降低相位噪声性能。为了获得出色性能,建议将 VDDDIG 和 VDDA 分开。 |

| VDDCLK18 | H12 H13 | I | 时钟 (CLK+/-) 输入缓冲器的 1.8V 电源电压。该电源上的噪声或杂散可能会降低相位噪声性能。 |

| VDDDIG | F7 H7 J7 L7 N7 G8 K8 M8 | I | 数字块的 1.0V 电源电压。为了获得出色性能,建议将 VDDA 和 VDDCLK 分开。 |

| VDDEA | F8 F9 | I | 通道 A DAC 编码器的 1.0V 电源电压。为了获得出色性能,建议与 VDDDIG 分开。可以与 VDDEB 结合使用。 |

| VDDEB | L8 L9 | I | 通道 B DAC 编码器使用的 1.0V 电源电压。为了获得出色性能,建议与 VDDDIG 分开。可以与 VDDEA 结合使用。 |

| VDDIO | D9 E9 | I | CMOS 输入和输出端子使用的 1.8V 电源。 |

| VDDLA | F10 H10 | I | 通道 A 的 DAC 模拟锁存器采用 1.0V 电源,独立于 VDDLB 以实现更理想的通道间串扰 (XTALK)。必须与 VDDDIG 分开以获得出色性能。 |

| VDDLB | J10 L10 | I | 通道 B 的 DAC 模拟锁存器采用 1.0V 电源,独立于 VDDLA 以实现更理想的通道间串扰 (XTALK)。必须与 VDDDIG 分开以获得出色性能。 |

| VDDR18 | K4 L4 M4 N4 | I | 串行器/解串器接收器使用的 1.8V 电源电压。 |

| VDDSYS18 | J12 J13 | I | SYSREF (SYSREF+/-) 输入缓冲器使用的 1.8V 电源电压。当 SYSREF 在正常运行期间被禁用时,可与 VDDCLK18 组合使用。当 SYSREF 在工作期间持续运行时,该电源应与 VDDCLK18 分离,以避免噪声和杂散耦合并降低相位噪声性能。 |

| VDDT | C3 D3 F3 G3 K3 L3 N3 P3 C4 P4 C5 H5 J5 P5 G6 K6 M6 C7 P7 C8 P8 | I | 串行器/解串器终端使用的 1.0V 电源电压。 |

| VEEAM18 | C11 D11 C12 D12 C13 D13 | I | 通道 A 的 DAC 电流源偏置使用 –1.8V 电源电压。可与 VEEBM18 搭配使用,但可能会降低通道间抗串扰 (XTALK) 性能。 |

| VEEBM18 | N11 P11 N12 P12 N13 P13 | I | 通道 B 的 DAC 电流源偏置使用 –1.8V 电源电压。可与 VEEAM18 搭配使用,但可能会降低通道间抗串扰 (XTALK) 性能。 |

| VQPS | N9 P9 | I | 仅供 TI 使用。可在正常工作期间连接至 DGND。 |

| 接地 | |||

| AGND | A10 B10 C10 D10 N10 P10 R10 T10 A11 B11 R11 T11 B12 R12 B13 G13 K13 R13 A14 B14 C14 D14 N14 P14 R14 T14 G15 H15 K15 G16 K16 | - | 模拟接地。 |

| DGND | A1 B1 E1 H1 J1 M1 R1 T1 A2 B2 E2 H2 J2 M2 R2 T2 A3 B3 E3 H3 J3 M3 R3 T3 K5 L5 N5 A6 B6 C6 F6 H6 J6 L6 P6 R6 T6 G7 K7 M7 H8 J8 N8 A9 B9 C9 G9 H9 J9 K9 M9 R9 T9 | - | 数字接地。 |

| VSSCLK | E10 G10 K10 M10 E11 G11 K11 M11 F12 G12 K12 L12 E13 F13 L13 M13 E14 F14 L14 M14 A15 B15 C15 D15 E15 F15 L15 M15 N15 P15 R15 T15 A16 B16 C16 F16 L16 P16 R16 T16 | - | 时钟接地。 |