at TA =

25°C, channel A shown, and DAC outputs unloaded (unless otherwise

noted)

| VDD = 5.5 V, VREF

= 5.0 V |

Figure 6-2 Integral Linearity Error

vs Digital Input Code

| VDD = 5.5 V, VREF

= 5.0 V |

Figure 6-4 Integral Linearity Error

Histogram

| VDD = 5.5 V, VREF

= 5.0 V |

Figure 6-6 Differential Linearity Error vs Digital Input

Code

| VDD = 5.5 V, VREF

= 5.0 V |

Figure 6-8 Total

Unadjusted Error vs Digital Input CodeFigure 6-10 Zero-Code Error vs Temperature Figure 6-12 Supply Current vs

Temperature

| VDD = 5.5 V, VREF

= 5.0 V, |

| DAC code transition from midscale – 1

to midscale LSB |

Figure 6-14 Glitch Impulse, Rising Edge, 1-LSB Step

| VDD = 2.7 V, VREF

= 2.5 V |

Figure 6-16 Full-Scale Settling Time, Rising Edge

| VDD = 5.5 V, VREF

= 5.0 V |

Figure 6-18 Power-On Glitch

| VDD = 5.5 V, DAC code at

midscale |

Figure 6-20 Power-Supply Rejection Ratio (PSRR)Figure 6-22 Reference Current vs Digital Input Code

| VDD = 2.7 V, VREF

= 2.5 V |

Figure 6-24 Control FeedthroughFigure 6-26 Channel-to-Channel Crosstalk

| VDD = 2.7 V, VREF

= 2.5 V |

Figure 6-3 Integrated Linearity Error

vs Digital Input Code

| VDD = 2.7 V, VREF

= 2.5 V |

Figure 6-5 Integrated Linearity Error

Histogram

| VDD = 2.7 V, VREF

= 2.5 V |

Figure 6-7 Differential Linearity Error vs Digital Input

Code

| VDD = 2.7 V, VREF

= 2.5 V |

Figure 6-9 Total

Unadjusted Error vs Digital Input CodeFigure 6-11 Gain

Error vs Temperature Figure 6-13 Power-down Current vs

Temperature

| VDD = 5.5 V, VREF

= 5.0 V, |

| DAC code transition from midscale to

midscale - 1 LSB |

Figure 6-15 Glitch Impulse, Falling Edge, 1-LSB Step

| VDD = 2.7 V, VREF

= 2.5 V |

Figure 6-17 Full-Scale Settling Time, Falling Edge

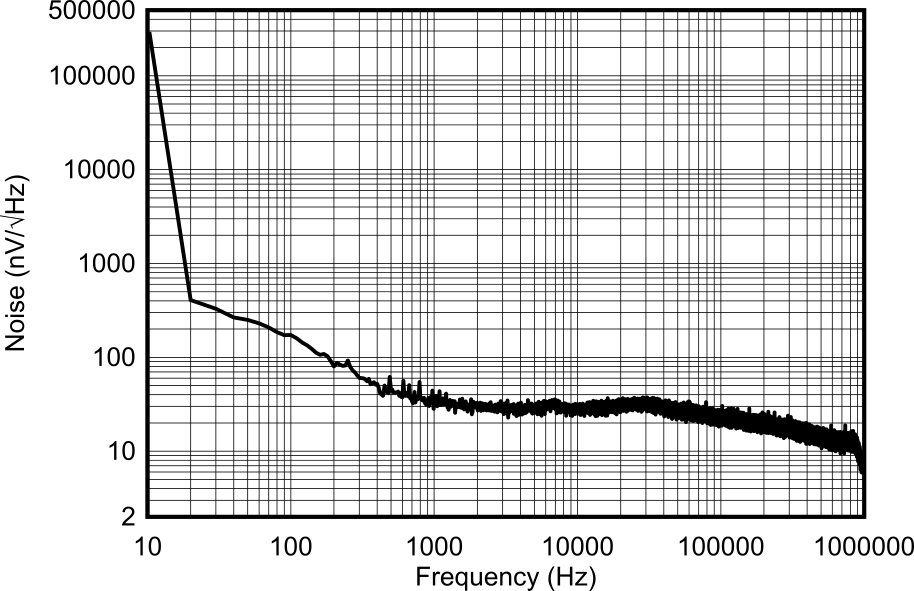

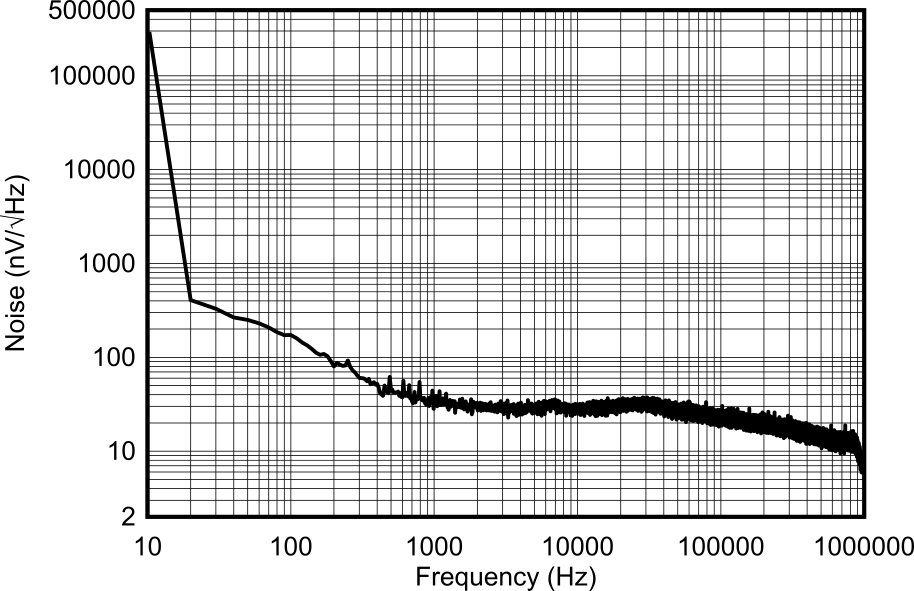

| VDD = 5.5 V, VREF

= 5.0 V |

Figure 6-19 Power-Off Glitch

| VDD = 5.5 V, VREF

= 5.0 V |

Figure 6-21 Output Noise Density vs Frequency

| VDD = 2.7 V, VREF

= 2.5 V |

Figure 6-23 Clock

Feedthrough

| |

| VDD = 5.5 V, VREF

= 5.0 V |

Figure 6-25 RESET Response