ZHCSX44 September 2024 DDS39RF12 , DDS39RFS12

PRODUCTION DATA

7.3.7.8.1 对 RBD 进行编程

RBD 的合适值范围取决于 Rx 和 Tx LMFC/LEMC 之间的相位差以及 Tx、通道和 Rx 中的链路延迟。因此,请勿提供预先确定好适用于所有系统的 RBD 值。提供的 LANE_ARR 寄存器可帮助用户测量通道到达时间并为系统选择适当的 RBD 值。为了确保确定性延迟,可在系统原型设计期间选择 RBD 值并将其存储在系统固件中。每次打开系统时计算 RBD 可能会导致不确定的延迟。

到达时间以四字节为单位进行报告,并以模数 64 基准计数器为基准进行测量,该计数器会针对接收到的每个四字节(每通道)递增。基准计数器由 SYSREF 对齐(复位)。

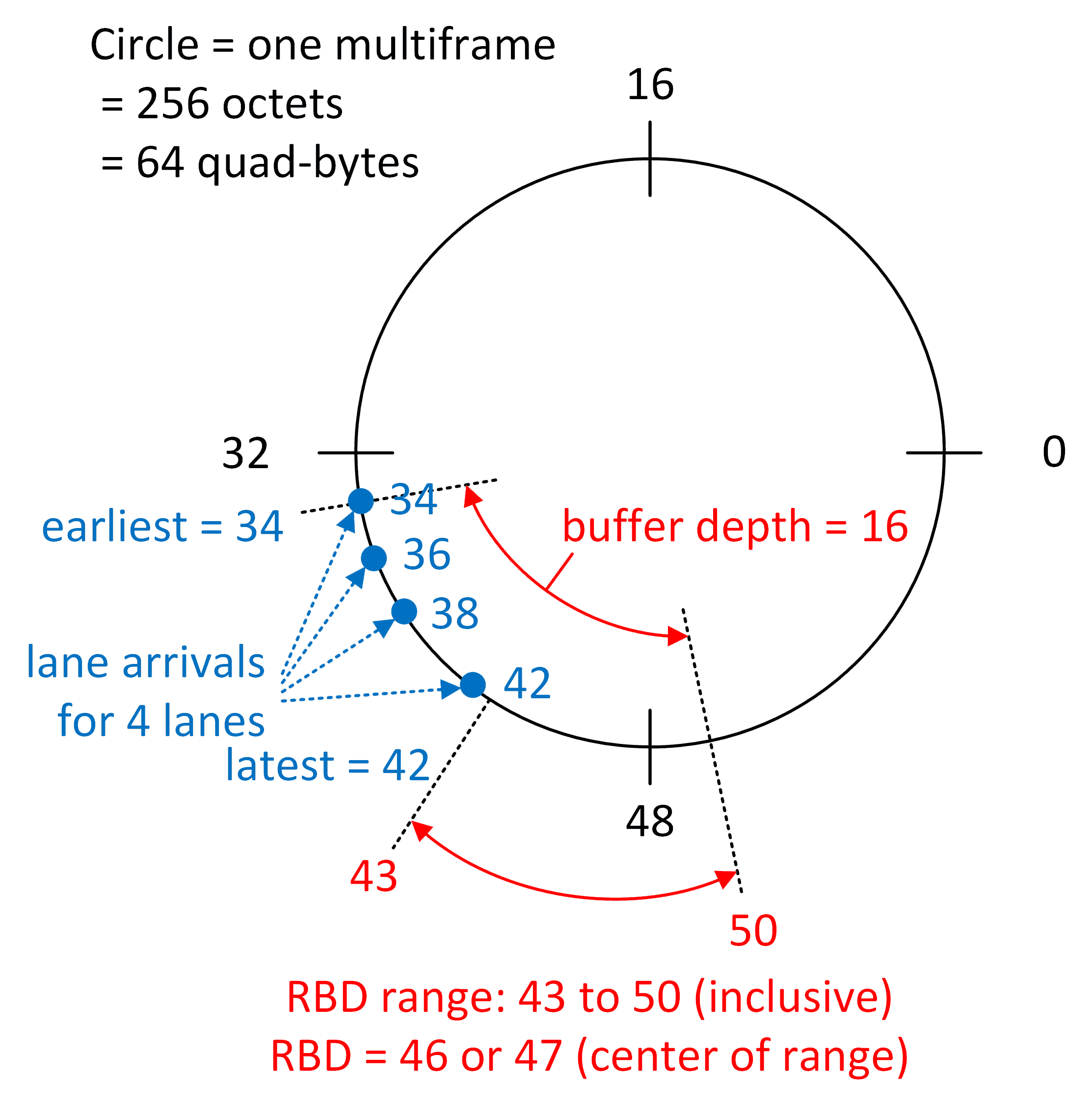

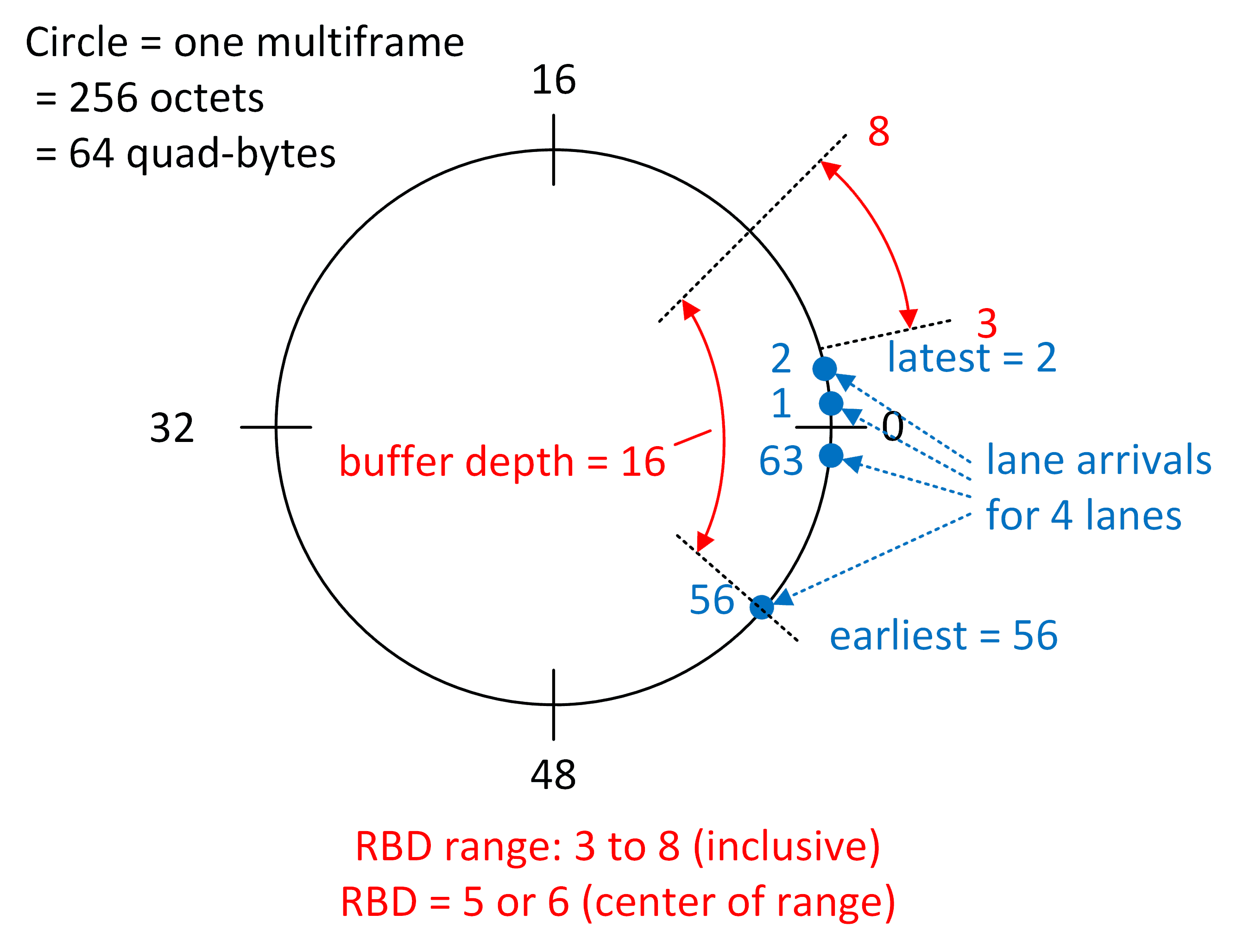

由于通道到达时间是模值,因此使用考虑模值的算术非常重要(与最早到达的通道相比,最近 到达的通道实际上可能具有更小 的 LANE_ARR 值)。图 7-55 和图 7-56 以图形方式描述了 RBD 计算,以强调这一点。通道到达时间被映射到周长为 64 个四字节的圆上,这对应于用于测量通道到达时间的模数 64 计数器。

最早可用的 RBD 值等于最新的 LANE_ARR 值加 1(模数 64)。最新可用的 RBD 值等于最早的 LANE_ARR 值加上缓冲区深度(模数 64)(缓冲区深度为 16 个四位/八位位组,除非 K x F = 32,此时缓冲区深度减少为 8 个四位/八位位组)。请注意,最新的可用 RBD 值会导致最早到达的通道在数据被读出的相同时钟周期内覆盖缓冲区数据(这是可以接受的,不会导致溢出)。

在可用范围的中间选择 RBD 值将更大程度地提高偏差容限,但如果需要更低的延迟,用户可以选择更接近最新到达通道的值。

图 7-55 RBD 示例(通道到达时间不会跨越零)

图 7-55 RBD 示例(通道到达时间不会跨越零) 图 7-56 RBD 示例(通道到达时间跨越零)

图 7-56 RBD 示例(通道到达时间跨越零)