ZHCSJA4B January 2019 – May 2022 DLP4500

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Chipset Component Usage Specification

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 Storage Conditions

- 7.3 ESD Ratings

- 7.4 Recommended Operating Conditions

- 7.5 Thermal Information

- 7.6 Electrical Characteristics

- 7.7 Timing Requirements

- 7.8 System Mounting Interface Loads

- 7.9 Micromirror Array Physical Characteristics

- 7.10 Micromirror Array Optical Characteristics

- 7.11 Typical Characteristics

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

-

11Layout

- 11.1 Layout Guidelines

- 11.2 Layout Example

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

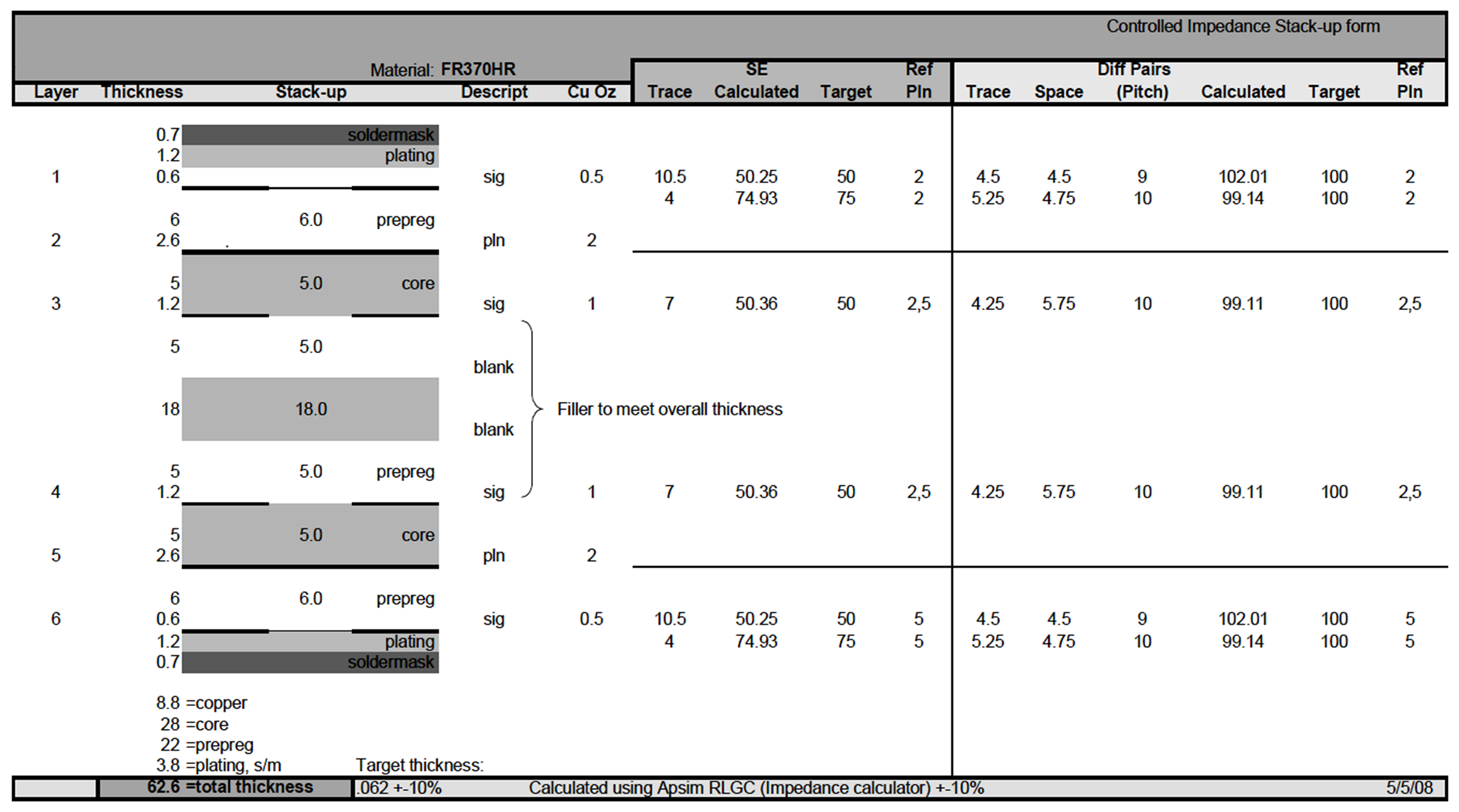

11.2.1 Printed Circuit Board Layer Stackup Geometry

The DLPC350 PCB is targeted at six layers with layer stack up shown in Figure 11-2. The PCB layer stack may vary depending on system design. However, careful attention is required to meet design considerations. Layers one and six should consist of the components layers. Low-speed routing and power splits are allowed on these layers. Layer two should consist of a solid ground plane. Layer five should be a split voltage plane. Layers three and four should be used as the primary routing layers. Routing on external layers should be less than 0.25 inches for priority one and two signals. Refer to Table 11-7 for signal priority groups.

Board material should be FR-370HR or similar. PCB should be designed for lead-free assembly with the stackup geometry shown in Figure 11-2.

Figure 11-2 Layer Stackup

Figure 11-2 Layer Stackup| PARAMETER | DESCRIPTION | RECOMMENDATION |

|---|---|---|

| Reference plane 1 | Ground plane for proper return | |

| Reference plane 2 | 1.9-V DMD I/O power plane or ground | |

| Er | Dielectric FR4 | 4.3 at 1 GHz (nominal) |

| H1 | Signal trace distance to reference plane 1 | 5 mil (0.127 mm) |

| H2 | Signal trace distance to reference plane 2 | 30.4 mil |