ZHCSJA4B January 2019 – May 2022 DLP4500

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Chipset Component Usage Specification

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 Storage Conditions

- 7.3 ESD Ratings

- 7.4 Recommended Operating Conditions

- 7.5 Thermal Information

- 7.6 Electrical Characteristics

- 7.7 Timing Requirements

- 7.8 System Mounting Interface Loads

- 7.9 Micromirror Array Physical Characteristics

- 7.10 Micromirror Array Optical Characteristics

- 7.11 Typical Characteristics

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

-

11Layout

- 11.1 Layout Guidelines

- 11.2 Layout Example

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

11.1.2 DMD Termination Requirements

Table 11-1 lists the termination requirements for the DMD interface. These series resistors should be placed as close to the DLPC350 pins as possible while following all PCB guidelines.

Table 11-1 Termination Requirements for DMD Interface

| SIGNALS | SYSTEM TERMINATION |

|---|---|

| DMD_D(23:0), DMD_TRC, DMD_SCTRL, DMD_LOADB, DMD_DRC_STRB, DMD_DRC_BUS, DMD_SAC_CLK, and DMD_SAC_BUS | External 5-Ω series termination at the transmitter |

| DMD_DCLK | External 5-Ω series termination at the transmitter |

| DMD_DRC_OE | External 0-Ω series termination. This signal must be externally pulled-up to VDD_DMD via a 30-kΩ to 51-kΩ resistor |

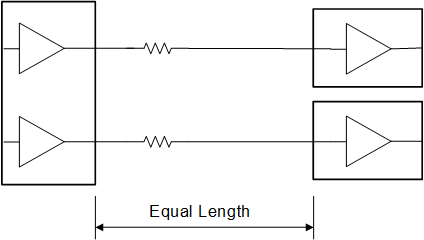

DMD_CLK and DMD_SAC_CLK clocks should be equal lengths, as shown in Figure 11-1.

Figure 11-1 Series-Terminated Clocks

Figure 11-1 Series-Terminated Clocks