ZHCSJA3B January 2019 – May 2022 DLP4500NIR

PRODUCTION DATA

- 1 特性

- 2 应用范围

- 3 说明

- 4 Revision History

- 5 Chipset Component Usage Specification

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 Storage Conditions

- 7.3 ESD Ratings

- 7.4 Recommended Operating Conditions

- 7.5 Thermal Information

- 7.6 Electrical Characteristics

- 7.7 Timing Requirements

- 7.8 System Mounting Interface Loads

- 7.9 Micromirror Array Physical Characteristics

- 7.10 Micromirror Array Optical Characteristics

- 7.11 Typical Characteristics

- 8 Detailed Description

- 9 Applications and Implementation

- 10Power Supply Recommendations

-

11Layout

- 11.1 Layout Guidelines

- 11.2 Layout Example

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

6 Pin Configuration and Functions

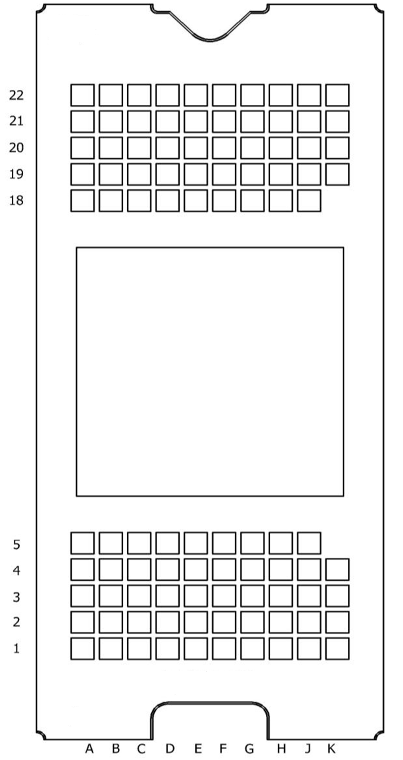

Figure 6-1 FQD Package LCCC (98) Bottom View

Figure 6-1 FQD Package LCCC (98) Bottom ViewTable 6-1 Connector Pins for FQD

| PIN | TYPE | SIGNAL | DATA RATE (1) | INTERNAL TERMINATION | DESCRIPTION | PACKAGE NET LENGTH (mm) (2) | |

|---|---|---|---|---|---|---|---|

| NAME | NO. | ||||||

| DATA INPUTS | |||||||

| DATA(0) | A1 | Input | LVCMOS | DDR | none | Input data bus, bit 0, LSB | 3.77 |

| DATA(1) | A2 | Input | LVCMOS | DDR | none | Input data bus, bit 1 | 3.77 |

| DATA(2) | A3 | Input | LVCMOS | DDR | none | Input data bus, bit 2 | 3.73 |

| DATA(3) | A4 | Input | LVCMOS | DDR | none | Input data bus, bit 3 | 3.74 |

| DATA(4) | B1 | Input | LVCMOS | DDR | none | Input data bus, bit 4 | 3.79 |

| DATA(5) | B3 | Input | LVCMOS | DDR | none | Input data bus, bit 5 | 3.75 |

| DATA(6) | C1 | Input | LVCMOS | DDR | none | Input data bus, bit 6 | 3.72 |

| DATA(7) | C3 | Input | LVCMOS | DDR | none | Input data bus, bit 7 | 3.75 |

| DATA(8) | C4 | Input | LVCMOS | DDR | none | Input data bus, bit 8 | 3.78 |

| DATA(9) | D1 | Input | LVCMOS | DDR | none | Input data bus, bit 9 | 3.75 |

| DATA(10) | D4 | Input | LVCMOS | DDR | none | Input data bus, bit 10 | 3.77 |

| DATA(11) | E1 | Input | LVCMOS | DDR | none | Input data bus, bit 11 | 3.75 |

| DATA(12) | E4 | Input | LVCMOS | DDR | none | Input data bus, bit 12 | 3.71 |

| DATA(13) | F1 | Input | LVCMOS | DDR | none | Input data bus, bit 13 | 3.76 |

| DATA(14) | F3 | Input | LVCMOS | DDR | none | Input data bus, bit 14 | 3.73 |

| DATA(15) | G1 | Input | LVCMOS | DDR | none | Input data bus, bit 15 | 3.72 |

| DATA(16) | G2 | Input | LVCMOS | DDR | none | Input data bus, bit 16 | 3.77 |

| DATA(17) | G4 | Input | LVCMOS | DDR | none | Input data bus, bit 17 | 3.73 |

| DATA(18) | H1 | Input | LVCMOS | DDR | none | Input data bus, bit 18 | 3.74 |

| DATA(19) | H2 | Input | LVCMOS | DDR | none | Input data bus, bit 19 | 3.76 |

| DATA(20) | H4 | Input | LVCMOS | DDR | none | Input data bus, bit 20 | 3.70 |

| DATA(21) | J1 | Input | LVCMOS | DDR | none | Input data bus, bit 21 | 3.77 |

| DATA(22) | J3 | Input | LVCMOS | DDR | none | Input data bus, bit 22 | 3.76 |

| DATA(23) | J4 | Input | LVCMOS | DDR | none | Input data bus, bit 23, MSB | 3.77 |

| DCLK | K1 | Input | LVCMOS | DDR | none | Input data bus clock | 3.74 |

| DATA CONTROL INPUTS | |||||||

| LOADB | K2 | Input | LVCMOS | DDR | none | Parallel-data load enable | 3.74 |

| TRC | K4 | Input | LVCMOS | DDR | none | Input-data toggle rate control | 4.70 |

| SCTRL | K3 | Input | LVCMOS | DDR | none | Serial-control bus | 3.75 |

| SAC_BUS | C20 | Input | LVCMOS | — | none | Stepped address-control serial-bus data | 3.77 |

| SAC_CLK | C22 | Input | LVCMOS | — | none | Stepped address-control serial-bus clock | 1.49 |

| MIRROR RESET CONTROL INPUTS | |||||||

| DRC_BUS | B21 | Input | LVCMOS | — | none | DMD reset-control serial bus | 3.73 |

| DRC_OE | A20 | Input | LVCMOS | — | none | Active-low output enable signal for internal DMD reset driver circuitry | 3.74 |

| DRC_STROBE | A22 | Input | LVCMOS | — | none | Strobe signal for DMD reset-control inputs | 3.73 |

| POWER INPUTS (3) | |||||||

| VBIAS | C19 | Power | Mirror-reset bias voltage | ||||

| VBIAS | D19 | Power | |||||

| VOFFSET | A19 | Power | Mirror-reset offset voltage | ||||

| VOFFSET | K19 | Power | |||||

| VRESET | E19 | Power | Mirror-reset voltage | ||||

| VRESET | F19 | Power | |||||

| VREF | B19 | Power | Power supply for LVCMOS double-data-rate (DDR) interface | ||||

| VREF | J19 | Power | |||||

| VCC | B22 | Power | Power supply for LVCMOS logic | ||||

| VCC | C2 | Power | |||||

| VCC | D21 | Power | |||||

| VCC | E2 | Power | |||||

| VCC | E20 | Power | |||||

| VCC | E22 | Power | |||||

| VCC | F21 | Power | |||||

| VCC | G3 | Power | |||||

| VCC | G19 | Power | |||||

| VCC | G20 | Power | |||||

| VCC | G22 | Power | |||||

| VCC | H19 | Power | |||||

| VCC | H21 | Power | |||||

| VCC | J20 | Power | |||||

| VCC | J22 | Power | |||||

| VCC | K21 | Power | |||||

| VSS | A21 | Power | Ground – Common return for all power inputs | ||||

| VSS | B2 | Power | |||||

| VSS | B4 | Power | |||||

| VSS | B20 | Power | |||||

| VSS | C21 | Power | |||||

| VSS | D2 | Power | |||||

| VSS | D3 | Power | |||||

| VSS | D20 | Power | |||||

| VSS | D22 | Power | |||||

| VSS | E3 | Power | |||||

| VSS | E21 | Power | |||||

| VSS | F2 | Power | |||||

| VSS | F4 | Power | |||||

| VSS | F20 | Power | |||||

| VSS | F22 | Power | |||||

| VSS | G21 | Power | |||||

| VSS | H3 | Power | |||||

| VSS | H20 | Power | |||||

| VSS | H22 | Power | |||||

| VSS | J2 | Power | |||||

| VSS | J21 | Power | |||||

| VSS | K20 | Power | |||||

(1)

- DDR = Double data rate

- SDR = Single data rate

- Refer to Section 7.7 for specifications and relationships.

(2) Net trace lengths inside the package:

- Relative dielectric constant for the FQD ceramic package is 9.8.

- Propagation speed = 11.8 / sqrt(9.8) = 3.769 inches/ns.

- Propagation delay = 0.265 ns/inch = 265 ps/inch = 10.43 ps/mm.

(3) The following power supplies are all required to operate the

DMD: VSS, VCC, VOFFSET, VBIAS, VRESET.

Table 6-2 Test Pads for FQD Package

| NAME | PIN | SIGNAL | DESCRIPTION |

|---|---|---|---|

| UNUSED | A5, A18, B5, B18, C5, C18, D5, D18, E5, E18, F5, F18, G5, G18, H5, H18, J5, J18, K22 | Test pads | Do not connect |