ZHCSJA3B January 2019 – May 2022 DLP4500NIR

PRODUCTION DATA

- 1 特性

- 2 应用范围

- 3 说明

- 4 Revision History

- 5 Chipset Component Usage Specification

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 Storage Conditions

- 7.3 ESD Ratings

- 7.4 Recommended Operating Conditions

- 7.5 Thermal Information

- 7.6 Electrical Characteristics

- 7.7 Timing Requirements

- 7.8 System Mounting Interface Loads

- 7.9 Micromirror Array Physical Characteristics

- 7.10 Micromirror Array Optical Characteristics

- 7.11 Typical Characteristics

- 8 Detailed Description

- 9 Applications and Implementation

- 10Power Supply Recommendations

-

11Layout

- 11.1 Layout Guidelines

- 11.2 Layout Example

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

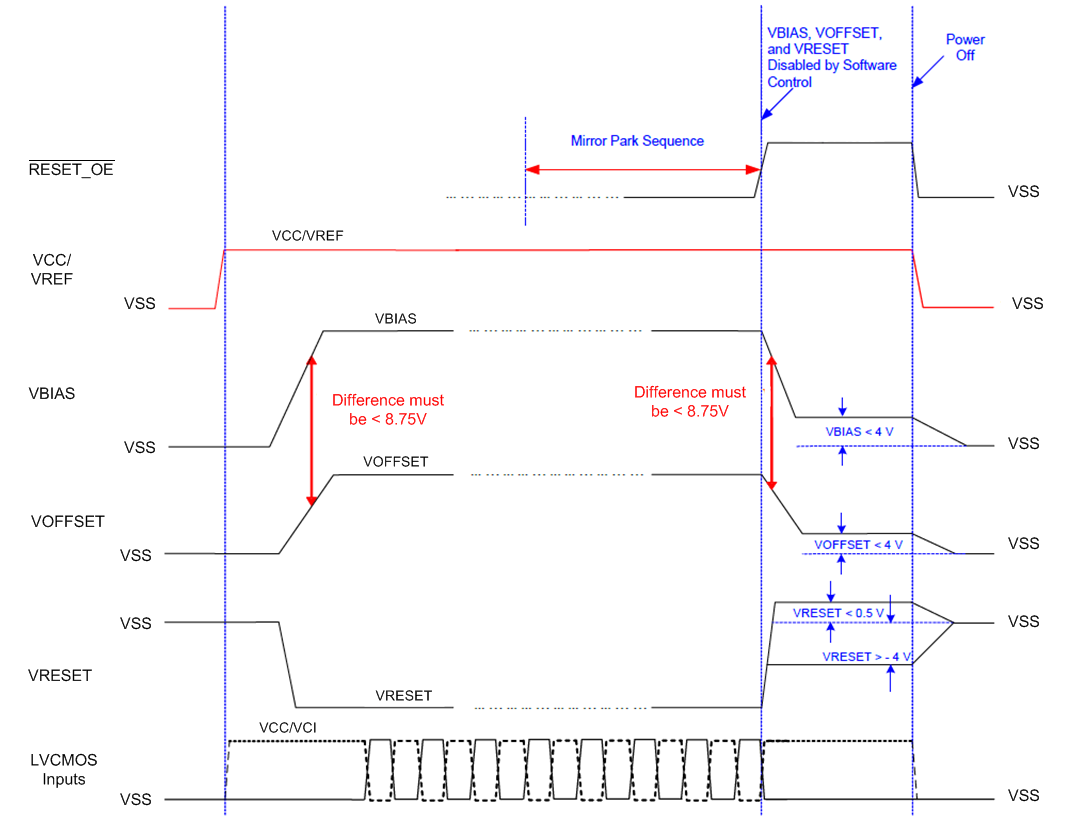

10.3 DMD Power Supply Power-Down Procedure

- Command the chipset controller to execute a mirror-parking sequence. See the controller data sheet (listed in Section 12.2.1) for details.

- Power down VBIAS, VOFFSET, and VRESET in any order, provided that the maximum delta voltage between VBIAS and VOFFSET is not exceeded (see Section 7.1 for details).

- Wait for VBIAS, VOFFSET, and VRESET to each discharge to a stable level within 4 V of the reference ground.

- Power down VCC and VREF in any order.

Note:

During the power-down procedure, the DMD LVCMOS inputs should be held at a level less than VREF + 0.3 V.

Note:

Power-supply slew rates during power down are unrestricted, provided that all other conditions are met.

Figure 10-1 Power-Up and Power-Down Timing

Figure 10-1 Power-Up and Power-Down Timing