ZHCSJA3B January 2019 – May 2022 DLP4500NIR

PRODUCTION DATA

- 1 特性

- 2 应用范围

- 3 说明

- 4 Revision History

- 5 Chipset Component Usage Specification

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 Storage Conditions

- 7.3 ESD Ratings

- 7.4 Recommended Operating Conditions

- 7.5 Thermal Information

- 7.6 Electrical Characteristics

- 7.7 Timing Requirements

- 7.8 System Mounting Interface Loads

- 7.9 Micromirror Array Physical Characteristics

- 7.10 Micromirror Array Optical Characteristics

- 7.11 Typical Characteristics

- 8 Detailed Description

- 9 Applications and Implementation

- 10Power Supply Recommendations

-

11Layout

- 11.1 Layout Guidelines

- 11.2 Layout Example

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

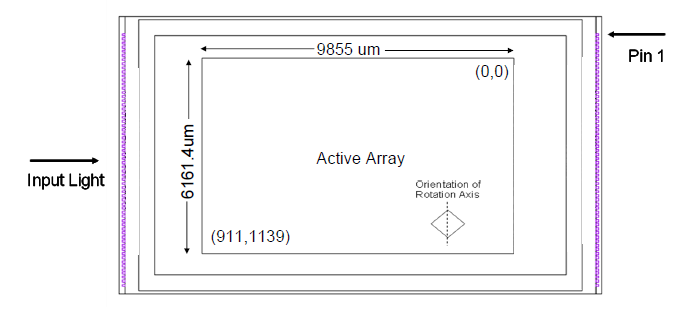

7.9 Micromirror Array Physical Characteristics

| VALUE | UNIT | |

|---|---|---|

| Number of active micromirror rows (2) | 1140 | micromirrors |

| Number of active micromirror columns (2) | 912 | micromirrors |

| Micromirror pitch, diagonal (2) | 7.6 | µm |

| Micromirror pitch, vertical and horizontal (2) | 10.8 | µm |

| Micromirror active array height (3) | 1140 | micromirrors |

| 6161.4 | µm | |

| Micromirror active array width (3) | 912 | micromirrors |

| 9855 | µm | |

| Micromirror array border (1) | 10 | mirrors/side |

(1) The mirrors that form the array border are hard-wired to tilt in the –12° (“Off”) direction once power is applied to the DMD (see Micromirror Array, Pitch, and Hinge-Axis Orientation and Micromirror Landed Positions and Light Paths).

(3) See Micromirror Active Area in Figure 7-4.

Figure 7-4 DLP4500NIR Micromirror Active Area

Figure 7-4 DLP4500NIR Micromirror Active Area