ZHCSKM7G december 2019 – july 2023 DP83826E , DP83826I

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Mode Comparison Tables

- 6 Pin Configuration and Functions (ENHANCED Mode)

- 7 Pin Configuration and Functions (BASIC Mode)

- 8 Specifications

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Auto-Negotiation (Speed/Duplex Selection)

- 9.3.2 Auto-MDIX Resolution

- 9.3.3 Energy Efficient Ethernet

- 9.3.4 EEE for Legacy MACs Not Supporting 802.3az

- 9.3.5 Wake-on-LAN Packet Detection

- 9.3.6 Low Power Modes

- 9.3.7 RMII Repeater Mode

- 9.3.8 Clock Output

- 9.3.9 Media Independent Interface (MII)

- 9.3.10 Reduced Media Independent Interface (RMII)

- 9.3.11 Serial Management Interface

- 9.3.12 100BASE-TX

- 9.3.13 10BASE-Te

- 9.3.14 Loopback Modes

- 9.3.15 BIST Configurations

- 9.3.16 Cable Diagnostics

- 9.3.17 LED and GPIO Configuration

- 9.4 Programming

- 9.5 Register Maps

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

8.8 Typical Characteristics

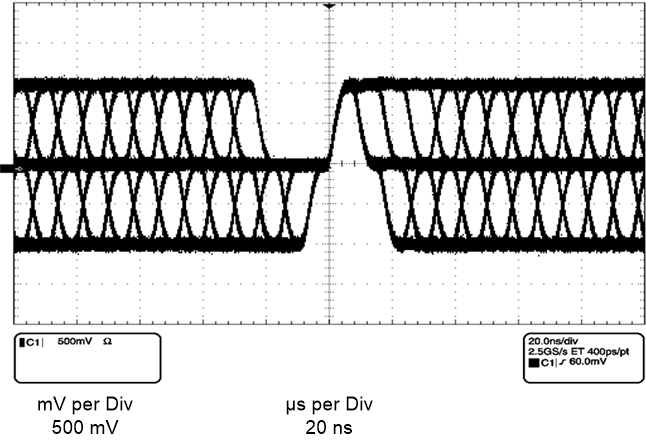

Figure 8-13 100BASE-TX PMD Eye Waveform

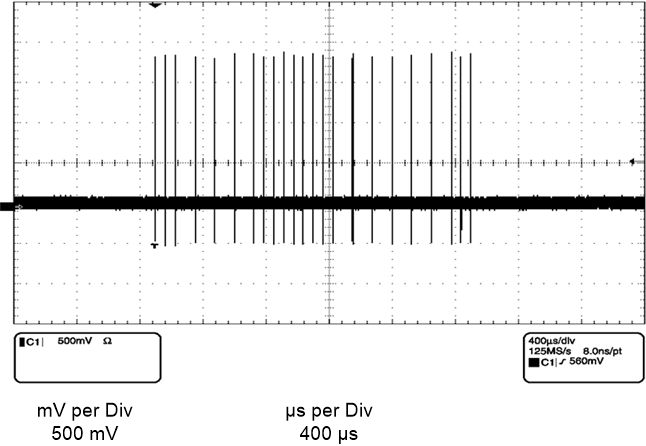

Figure 8-13 100BASE-TX PMD Eye Waveform Figure 8-15 Auto-Negotiation Fast Link Pulses Waveform

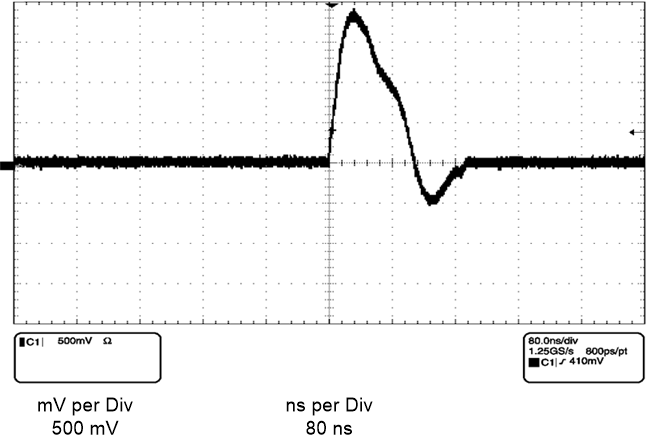

Figure 8-15 Auto-Negotiation Fast Link Pulses Waveform Figure 8-14 10BASE-Te Link Pulse Waveform

Figure 8-14 10BASE-Te Link Pulse Waveform