ZHCSM98D August 2020 – December 2023 DP83TD510E

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 引脚配置和功能

- 5 规格

- 6 详细说明

- 7 应用和实施

- 8 器件和文档支持

- 9 修订历史记录

- 10机械、封装和可订购信息

7.4.1.1 信号布线

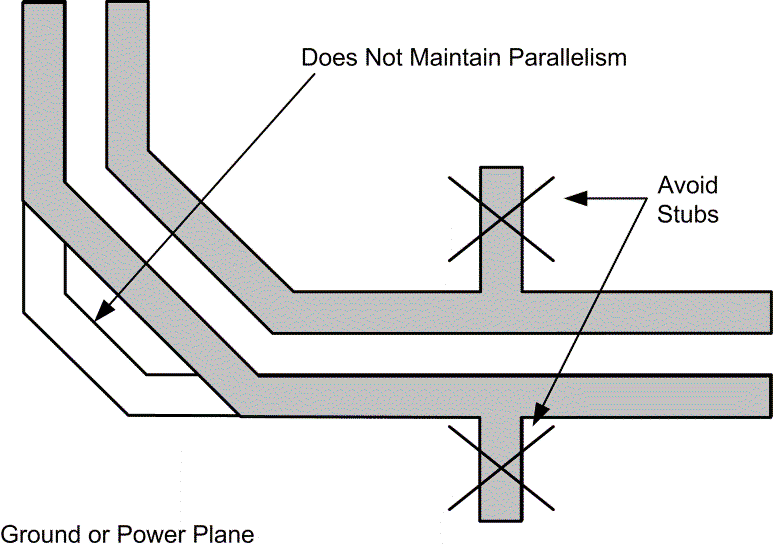

PCB 布线存在损耗,长布线会降低信号质量。应使迹线尽可能短。除非另有说明,否则所有信号布线都必须是 50Ω 单端阻抗。差分布线必须是 100Ω 差分阻抗。请务必确保阻抗始终可控。阻抗不连续性会产生反射,从而导致发射和信号完整性问题。所有信号布线,尤其是差分信号对,都应避免出现残桩。

图 7-7 差分信号布线

图 7-7 差分信号布线在差分对内,布线应相互平行且长度匹配。匹配的长度可充分减小延迟差异,避免增加共模噪声和发射。长度匹配对 MAC 接口连接也很重要。所有 RMII 发送信号布线的长度都应相互匹配,所有 RMII 接收信号布线的长度也应相互匹配。

理想情况下,信号路径布线上不应有交叉或过孔。过孔会导致阻抗不连续,应尽量减少过孔。在同一层布线差分信号对。不同层上的信号不应相互交叉,除非它们之间至少有一个返回路径平面。差分对之间应始终保持恒定耦合距离。为提高便利性和效率,TI 建议首先布线关键信号(即 MDI 差分对、基准时钟和 MAC IF 布线)。