ZHCSRD8A January 2023 – March 2024 DRV8143-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 器件比较

- 5 引脚配置和功能

- 6 规格

- 7 详细说明

- 8 寄存器映射 - 仅限 SPI 型号

- 9 应用和实施

- 10器件和文档支持

- 11修订历史记录

- 12机械、封装和可订购信息

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

- DGQ|28

订购信息

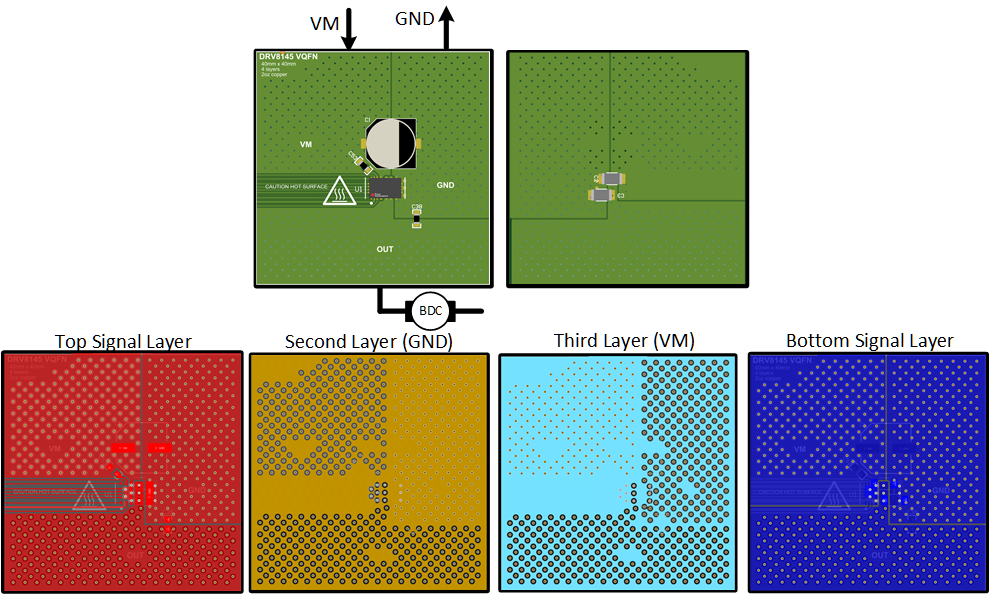

9.4.2 布局示例

下图展示了用于带引线封装器件的 4cm x 4cm x 1.6mm、4 层 PCB 的布局示例。在这 4 层中,在顶部/底部信号层使用 2盎司铜,在内部电源层使用 1盎司铜,热过孔钻孔直径为 0.3mm,镀铜层为 0.025mm,最小过孔间距为 1mm。无引线 VQFN-HR 封装也可以采用相同的布局。4cm x 4cm x 1.6mm 的节 6.5.14基于类似的布局。

注意:所示布局示例适用于采用 VQFN-HR 封装的 DRV814xQ1 器件的全桥拓扑。

图 9-9 布局示例:4cm x 4cm x 1.6mm,4 层 PCB

图 9-9 布局示例:4cm x 4cm x 1.6mm,4 层 PCB