ZHCSSN3A November 2023 – March 2024 DRV8242-Q1

PRODUCTION DATA

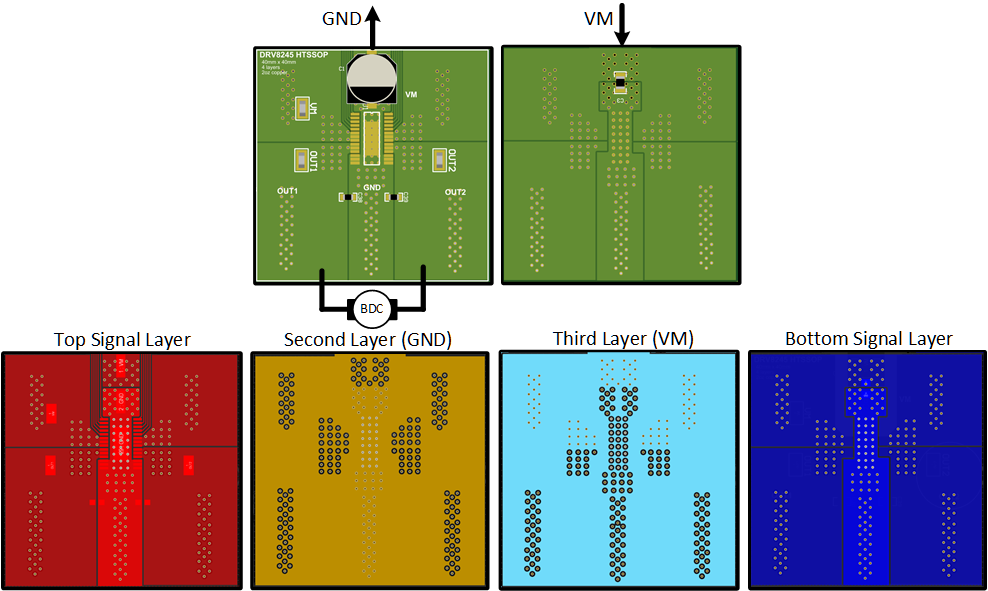

9.4.2 布局示例

下图展示了用于带引线封装器件的 4cm x 4cm x 1.6mm、4 层 PCB 的布局示例。在这 4 层中,在顶部/底部信号层使用 2 盎司铜,在内部电源层使用 1 盎司铜,热过孔钻孔直径为 0.3mm,镀铜层为 0.025mm,最小过孔间距为 1mm。无引线 VQFN-HR 封装也可以采用相同的布局。4cm x 4cm x 1.6mm 的节 6.6基于类似的布局。

注意:所示布局示例适用于采用 SSOP 封装的 DRV824xQ1 器件的全桥拓扑。

图 9-6 布局示例:4cm x 4cm x 1.6mm,4 层 PCB

图 9-6 布局示例:4cm x 4cm x 1.6mm,4 层 PCB