ZHCSC39B February 2014 – November 2017 DRV8308

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configurations and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Hall Comparators

- 7.3.2 FG Amplifier, Comparator, and FG Output

- 7.3.3 Enable, Reset, and Clock Generation

- 7.3.4 Commutation

- 7.3.5 Commutation Logic Block Diagram

- 7.3.6 Commutation Parameters

- 7.3.7 Braking

- 7.3.8 Output Pre-Drivers

- 7.3.9 Current Limit

- 7.3.10 Charge Pump

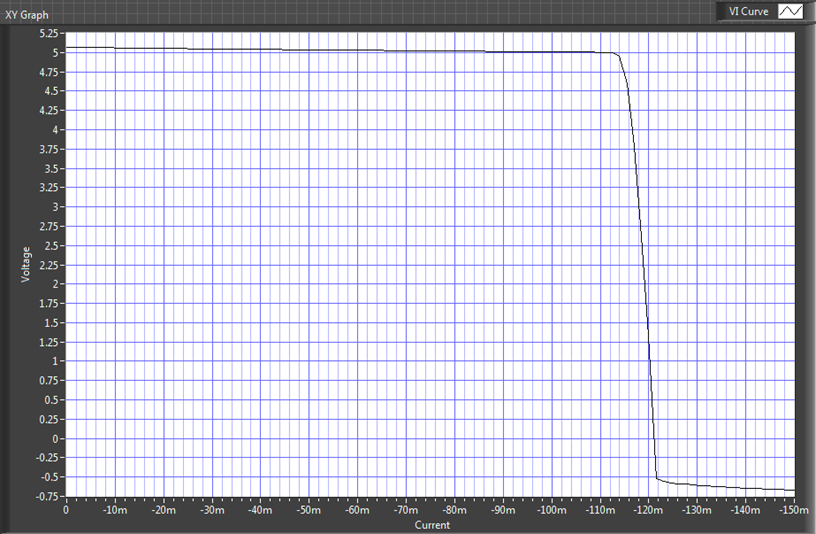

- 7.3.11 5-V Linear Regulator

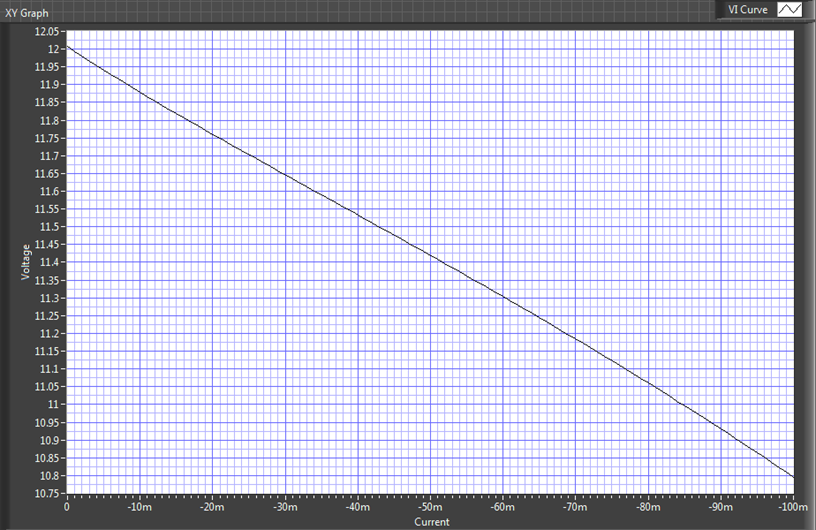

- 7.3.12 Power Switch

- 7.3.13 Protection Circuits

- 7.4 Device Functional Modes

- 7.5 Programming

- 7.6 Register Map

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) (1) (2) (3)| MIN | MAX | UNIT | |

|---|---|---|---|

| Power supply voltage (VM) | –0.3 | 42 | V |

| Charge pump and high side gate drivers (VCP, UHSG, VHSG, WHSG) | –0.3 | 50 | V |

| Output pin, low side gate drivers, charge pump flying cap and switched VM power supply voltage (U, V, W, ULSG, VLSG, WLSG, CP1, CP2 VSW) | –0.6 | 40 | V |

| Internal core voltage regulator (VINT) | –0.3 | 2 | V |

| Linear voltage regulator output (VREG) | –0.3 | 5.5 | V |

| Sense current pin (ISEN) | –0.3 | 2 | V |

| Digital pin voltage range (SCLK, SCS, SMODE, SDATAI, SDATAO, FGOUT, FAULTn, LOCKn, CLKIN, BRAKE, DIR, ENABLE, RESET) | –0.5 | 5.75 | V |

| Hall sensor input pin voltage (UHP, UHN, VHP, VHN, WHP, WHN, FGFB, FGINN/TACH, FGINP) | 0 | VREG | V |

| Continuous total power dissipation | See Thermal Information | ||

| Operating junction temperature range, TJ | –40 | 150 | °C |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground pin.

(3) Power dissipation and thermal limits must be observed

6.2 Handling Ratings

| MIN | MAX | UNIT | |||

|---|---|---|---|---|---|

| Tstg | Storage temperature range | –60 | 150 | °C | |

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins(1) | -4000 | 4000 | V |

| Charged device model (CDM), per JEDEC specification JESD22-C101, all pins(2) | -1500 | 1500 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)| MIN | NOM | MAX | UNIT | |||

|---|---|---|---|---|---|---|

| VM | Motor power supply voltage range, ENABLE = 1, motor operating(3) | 8.5 | 32 | V | ||

| VMDIS | Motor power supply voltage range, ENABLE = 0, motor not operating | 4.5 | 35 | |||

| IVREG | VREG output current(1) | 0 | 30 | mA | ||

| IVSW | VSW output current(1) | 0 | 30 | |||

| fHALL | Hall sensor input frequency(4) | 0 | 30 | kHz | ||

| fCLKIN | Frequency on CLKIN | SPDMODE = 00 (Clock Frequency Mode) | 0 | 90 | ||

| SPDMODE = 01 (Clock PWM Mode) | 16 | 50 (2) | ||||

(1) Power dissipation and thermal limits must be observed

(2) Operational with frequencies above 50 kHz, but resolution is degraded

(3) Note that at VM < 12 V, gate drive output voltage tracks VM voltage

(4) fHALL of 50 Hz to 6.7 kHz is best

6.4 Thermal Information

| THERMAL METRIC(1) | DRV8308 | UNIT | |

|---|---|---|---|

| RHA (VQFN) | |||

| 40 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 33.2 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 23 | °C/W |

| RθJB | Junction-to-board thermal resistance | 8.8 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.3 | °C/W |

| ψJB | Junction-to-board characterization parameter | 8.8 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | 2.3 | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)6.6 SPI Timing Requirements

TA = 25°C, over recommended operating conditions unless otherwise noted (1)| NUMBER(2) | MIN | MAX | UNIT | ||

|---|---|---|---|---|---|

| 1 | tCYC | Clock cycle time | 62 | ns | |

| 2 | tCLKH | Clock high time | 25 | ||

| 3 | tCLKL | Clock low time | 25 | ||

| 4 | tSU(SDATI) | Setup time, SDATI to SCLK | 5 | ||

| 5 | tH(SDATI) | Hold time, SDATI to SCLK | 1 | ||

| 6 | tSU(SCS) | Setup time, SCS to SCLK | 5 | ||

| 7 | tH(SCS) | Hold time, SCS to SCLK | 1 | ||

| 8 | tL(SCS) | Inactive time, SCS (between writes) | 100 | ||

| 9 | tD(SDATO) | Delay time, SCLK to SDATO (during read) | 10 | ||

| tAWAKE | Wake time (ENABLE active to high-side gate drive enabled) | 1 | ms | ||

| tSPI | Delay from power-up or RESET low until serial interface functional | 10 | μs |

(1) SMODE = Low

(2) These numbers refer to the corresponding number in Figure 1

Figure 1. SPI Timing Requirements

Figure 1. SPI Timing Requirements

6.7 Typical Characteristics