ZHCSOY8B September 2021 – February 2022 DRV8311

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Output Stage

- 8.3.2 Control Modes

- 8.3.3 Device Interface Modes

- 8.3.4 AVDD Linear Voltage Regulator

- 8.3.5 Charge Pump

- 8.3.6 Slew Rate Control

- 8.3.7 Cross Conduction (Dead Time)

- 8.3.8 Propagation Delay

- 8.3.9 Pin Diagrams

- 8.3.10 Current Sense Amplifiers

- 8.3.11 Protections

- 8.4 Device Functional Modes

- 8.5 SPI Communication

- 9 DRV8311 Registers

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

10.3.1 Detailed Design Procedure

Benefits of tSPI

The DRV8311P device integrates tSPI which allows for random write and read access to secondary motor driver devices for simultaneous motor control over a standard 4-wire SPI interface. This significantly reduce the number of wires in the system to reduce the overall system size and BOM costs. tSPI is especially useful in multi-motor systems by:

- Allowing random access to the DRV8311P devices with a general call address

- Performing read and writes in any order

- No requirement for all tSPI devices to be active at all times

- Perform transactions with any active secondary device regardless of the status of the other devices

For more information on using tSPI in multi-motor systems, refer Reduce Wires for Your Next Multi-Motor BLDC Design With tSPI Protocol.

Application Curves

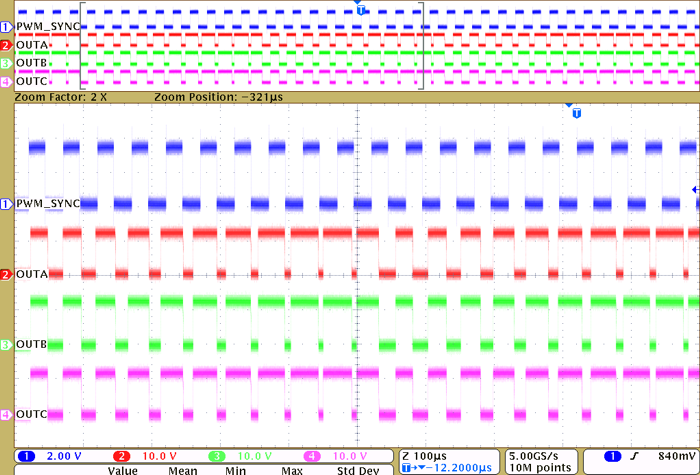

Figure 10-7 PWM Synchronous Duty Cycle

Operation with PWM_SYNC = 2b (10% - 90%) (PWM_SYNC, OUTA, OUTB, OUTC)

Figure 10-7 PWM Synchronous Duty Cycle

Operation with PWM_SYNC = 2b (10% - 90%) (PWM_SYNC, OUTA, OUTB, OUTC)