ZHCSKG2B September 2016 – October 2019 DS280BR820

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

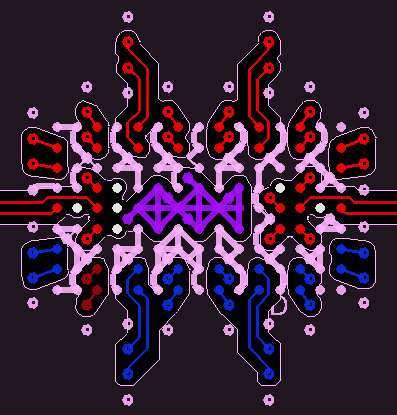

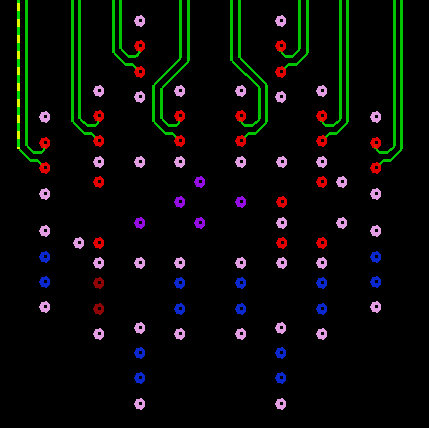

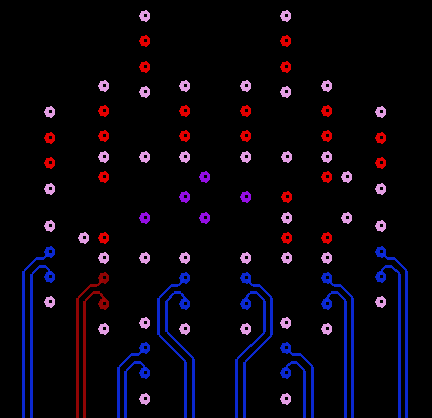

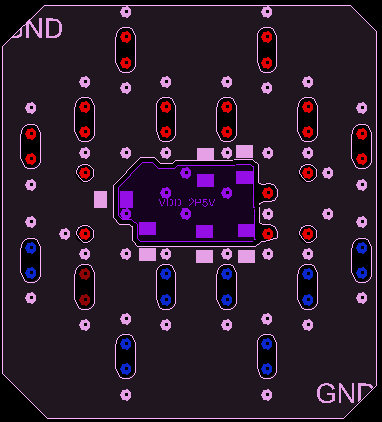

10.2.1 Stripline Example

The following example layout demonstrates how all signals can be escaped from the BGA array using stripline routing on a generic 8+ layer stackup. This example layout assumes the following:

- Trace width: 0.15 mm (6 mil)

- Trace edge-to-edge spacing: 0.16 mm (6.4 mil)

- VIA finished hole size (diameter): 0.254 mm (10 mil)

- VIA-to-VIA spacing: 1.0 mm (39 mil), to enhance PCB manufacturability

- No VIA-in-pad used

Note that many other escape routing options exist using different trace width and spacing combinations. The optimum trace width and spacing will depend on the PCB material, PCB routing density, and other factors. Microstrip escape routing is also possible and may be preferable in some application scenarios such as front-port applications.

Figure 31. Stripline Example, Top Layer

Figure 31. Stripline Example, Top Layer  Figure 33. Stripline Example, Internal Signal Layer 2

Figure 33. Stripline Example, Internal Signal Layer 2  Figure 32. Stripline Example, Internal Signal Layer 1

Figure 32. Stripline Example, Internal Signal Layer 1  Figure 34. Stripline Example, Bottom Layer

Figure 34. Stripline Example, Bottom Layer