ZHCSQD1 August 2022 DS320PR810

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

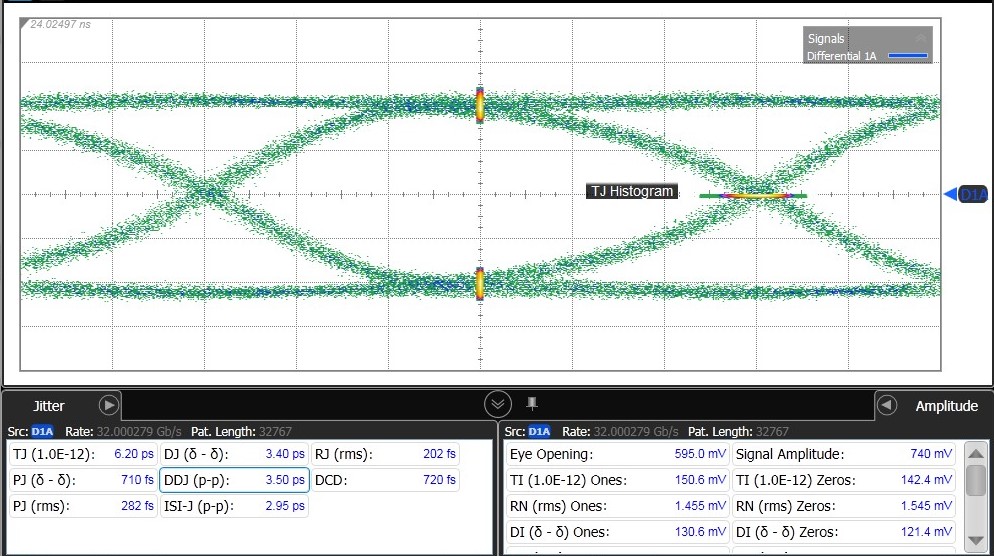

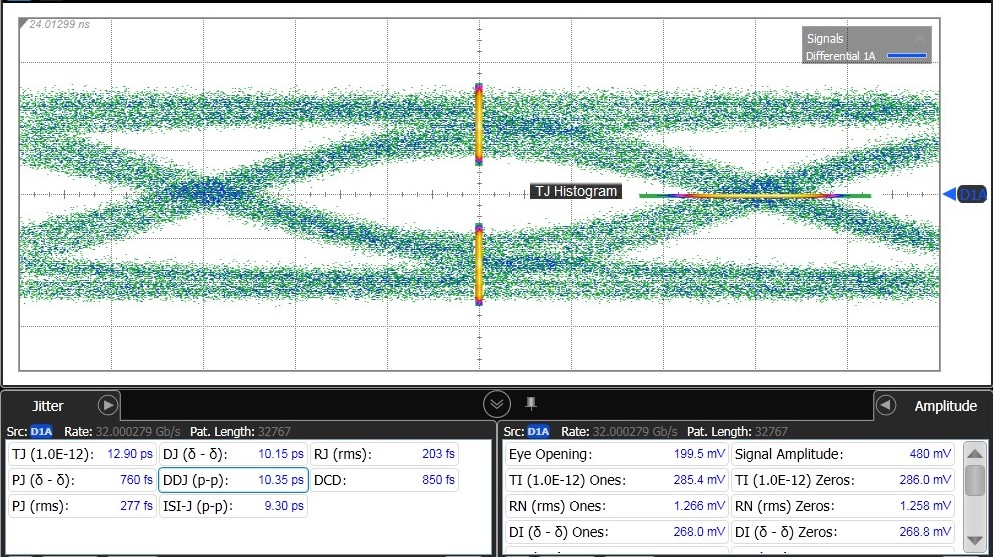

6.9 Typical Jitter Characteristics

Figure 6-4 , Figure 6-5, and Figure 6-6 show eye diagrams at BERT source output, through calibration traces, and through 810 respectively. Note: 810 adds little to no random jitter. Residual equalization of ≅4 dB at EQ = 0 setting results in slightly lower deterministic jitter through DUT compared to baseline setup with 7 dB loss.

Figure 6-4 At BERT Source Output (1

dB Loss)

Figure 6-4 At BERT Source Output (1

dB Loss)  Figure 6-6

Through DS320PR810

(7 dB Loss and DUT EQ = 0)

Figure 6-6

Through DS320PR810

(7 dB Loss and DUT EQ = 0)  Figure 6-5

Through Baseline Calibration Trace Setup (7 dB Loss)

Figure 6-5

Through Baseline Calibration Trace Setup (7 dB Loss)