ZHCSEN8A NOVEMBER 2014 – January 2016 DS90UH940-Q1

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 应用 图

- 5 修订历史记录

- 6 Pin Configurations and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings—JEDEC

- 7.3 ESD Ratings—IEC and ISO

- 7.4 Recommended Operating Conditions

- 7.5 Thermal Information

- 7.6 DC Electrical Characteristics

- 7.7 AC Electrical Characteristics

- 7.8 Timing Requirements for the Serial Control Bus

- 7.9 Switching Characteristics

- 7.10 Timing Diagrams and Test Circuits

- 7.11 Power Sequence

- 7.12 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 High Speed Forward Channel Data Transfer

- 8.3.2 Low Speed Back Channel Data Transfer

- 8.3.3 FPD-Link III Port Register Access

- 8.3.4 Clock and Output Status

- 8.3.5 LVCMOS VDDIO Option

- 8.3.6 Power Down (PDB)

- 8.3.7 Interrupt Pin — Functional Description and Usage (INTB_IN)

- 8.3.8 General-purpose I/O

- 8.3.9 SPI Communication

- 8.3.10 Backward Compatibility

- 8.3.11 Input Equalization

- 8.3.12 I2S Audio Interface

- 8.3.13 HDCP

- 8.3.14 Built-In Self Test (BIST)

- 8.3.15 Internal Pattern Generation

- 8.4 Device Functional Modes

- 8.5

Programming

- 8.5.1 Serial Control Bus

- 8.5.2 Multi-Master Arbitration Support

- 8.5.3 I2C Restrictions on Multi-Master Operation

- 8.5.4 Multi-Master Access to Device Registers for Newer FPD-Link III Devices

- 8.5.5 Multi-Master Access to Device Registers for Older FPD-Link III Devices

- 8.5.6 Restrictions on Control Channel Direction for Multi-Master Operation

- 8.6 Register Maps

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

11 Layout

11.1 Layout Guidelines

Circuit board layout and stack-up for the FPD-Link III devices should be designed to provide low-noise power feed to the device. Good layout practice will also separate high frequency or high-level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. Power system performance may be greatly improved by using thin dielectrics (2 to 4 mils) for power/ground sandwiches. This arrangement provides plane capacitance for the PCB power system with low-inductance parasitics, which has proven especially effective at high frequencies, and makes the value and placement of external bypass capacitors less critical. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range of 0.01 µF to 0.1 µF. Tantalum capacitors may be in the 2.2 µF to 10 µF range. Voltage rating of the tantalum capacitors should be at least 5X the power supply voltage being used.

Surface mount capacitors are recommended due to their smaller parasitics. When using multiple capacitors per supply pin, locate the smaller value closer to the pin. A large bulk capacitor is recommend at the point of power entry. This is typically in the 50 µF to 100 µF range and will smooth low frequency switching noise. It is recommended to connect power and ground pins directly to the power and ground planes with bypass capacitors connected to the plane with via on both ends of the capacitor. Connecting power or ground pins to an external bypass capacitor will increase the inductance of the path.

A small body size X7R chip capacitor, such as 0603 or 0402, is recommended for external bypass. Its small body size reduces the parasitic inductance of the capacitor. The user must pay attention to the resonance frequency of these external bypass capacitors, usually in the range of 20MHz to 30 MHz. To provide effective bypassing, multiple capacitors are often used to achieve low impedance between the supply rails over the frequency of interest. At high frequency, it is also a common practice to use two vias from power and ground pins to the planes, reducing the impedance at high frequency.

Some devices provide separate power and ground pins for different portions of the circuit. This is done to isolate switching noise effects between different sections of the circuit. Separate planes on the PCB are typically not required. Pin Description tables typically provide guidance on which circuit blocks are connected to which power pin pairs. In some cases, an external filter may be used to provide clean power to sensitive circuits such as PLLs.

Use at least a four layer board with a power and ground plane. Locate LVCMOS signals away from the CML lines to prevent coupling from the LVCMOS lines to the CML lines. Closely-coupled differential lines of 100 Ω are typically recommended for CML interconnect. The closely coupled lines help to ensure that coupled noise will appear as common-mode and thus is rejected by the receivers. The tightly coupled lines will also radiate less.

Information on the WQFN style package is provided in TI Application Note: AN-1187.

11.2 Layout Example

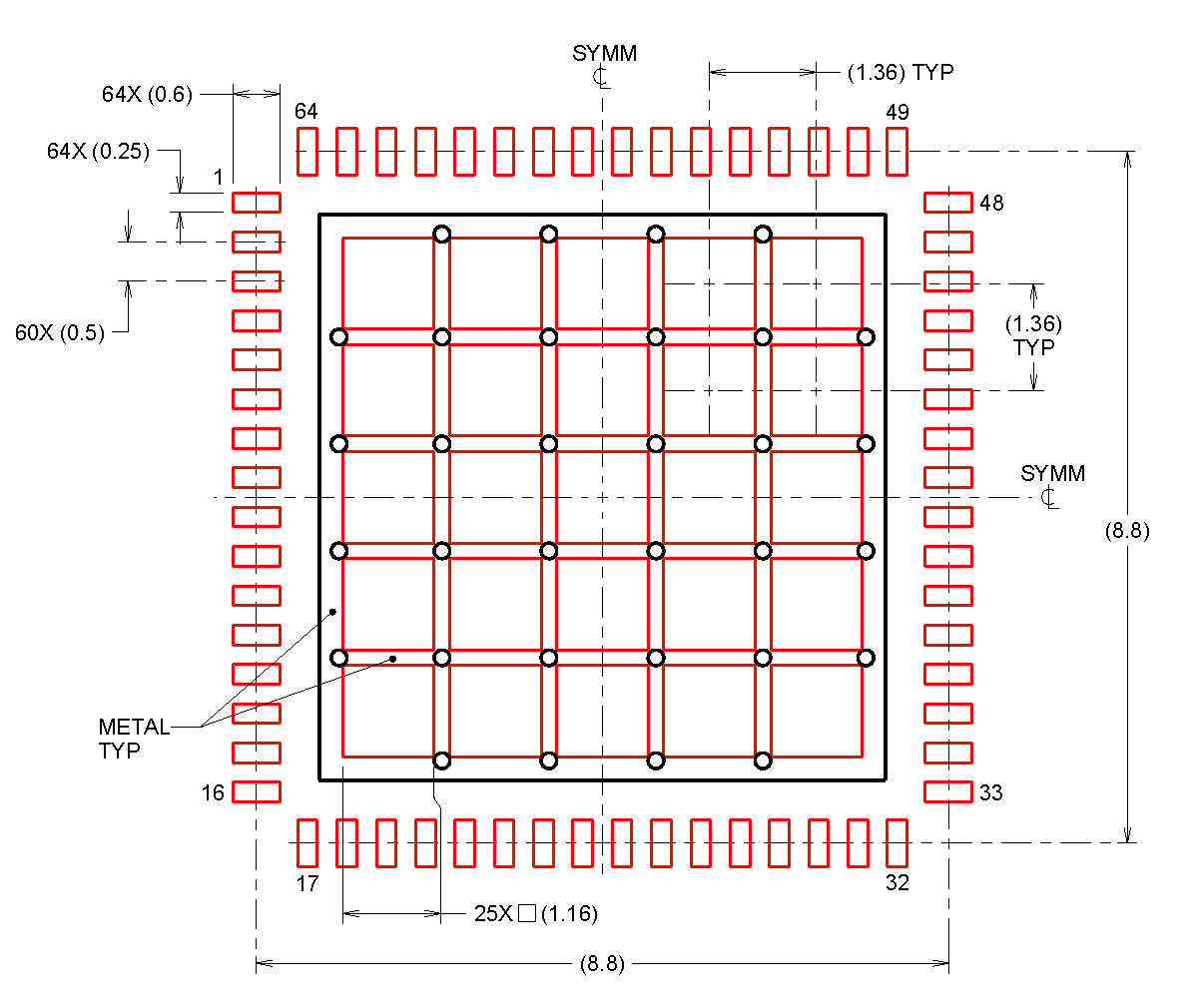

Stencil parameters such as aperture area ratio and the fabrication process have a significant impact on paste deposition. Inspection of the stencil prior to placement of the WQFN package is highly recommended to improve board assembly yields. If the via and aperture openings are not carefully monitored, the solder may flow unevenly through the DAP. Stencil parameters for aperture opening and via locations are shown in Figure 43:

Table 15. No Pullback WQFN Stencil Aperture Summary

| Device | Pin Count | Mkt Dwg | PCB I/O Pad Size (mm) | PCB Pitch (mm) | PCB DAP Size(mm) | Stencil I/O Aperture (mm) | Stencil DAP Aperture (mm) | Number OF DAP Aperture Openings | Gap between DAP Aperture (Dim A mm) |

|---|---|---|---|---|---|---|---|---|---|

| DS90UH940-Q1 | 64 | NKD | 0.25 x 0.6 | 0.5 | 7.2 x 7.2 | 0.25 x 0.6 | 1.16 x 1.16 | 25 | 0.2 |

Figure 43. 64-Pin WQFN Stencil Example of Via and Opening Placement

Figure 43. 64-Pin WQFN Stencil Example of Via and Opening Placement(dimensions in mm)

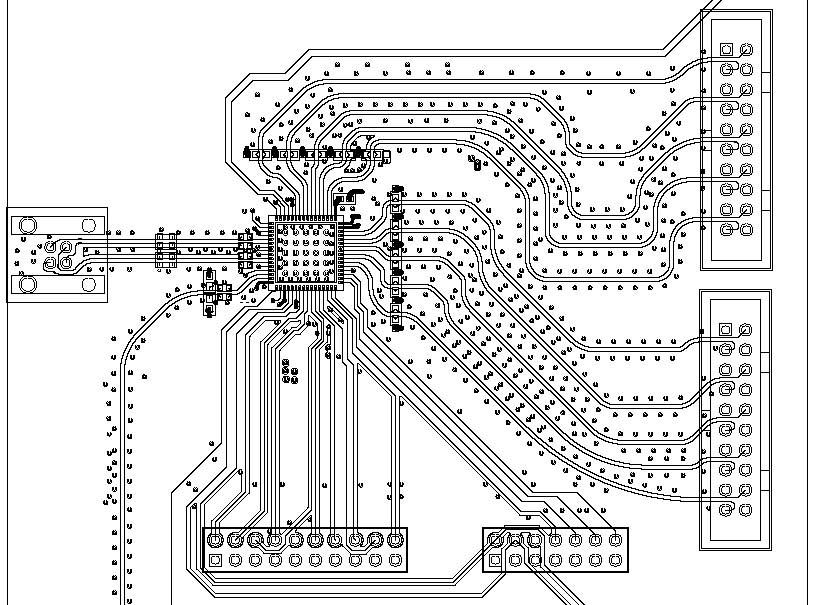

Figure 44 (PCB layout example) is derived from a layout design of the DS90UH940-Q1. This graphic and additional layout description are used to demonstrate both proper routing and proper solder techniques when designing in the Deserializer.

Figure 44. DS90UH940-Q1 Deserializer Example Layout

Figure 44. DS90UH940-Q1 Deserializer Example Layout