ZHCSFC4D december 2015 – september 2020 HD3SS3220

PRODUCTION DATA

3 说明

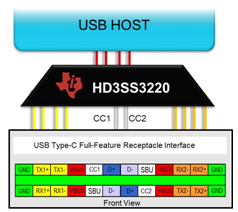

HD3SS3220 是一款具有 USB 超高速 (SS) 2:1 多路复用器的 DRP 端口控制器。该器件为实现 USB Type-C 的生态系统提供通道配置 (CC) 逻辑和 5V VCONN 电源。HD3SS3220 可配置为下行端口 (DFP)、上行端口 (UFP) 或双角色端口 (DRP),因此非常适合任何应用。

根据 Type-C 规范,HD3SS3220 在 DRP 模式下会交替将自身配置为 DFP 或 UFP。CC 逻辑块通过监视 CC1 和 CC2 引脚上的上拉或下拉电阻,以确定何时连接了 USB 端口以及其端口角色。连接 USB 端口后,CC 逻辑还将确定电缆方向并相应地配置 USB SS 多路复用器。最后,CC 逻辑将分别在 DFP 和 UFP 模式下广播或检测 Type-C 电流模式(默认、中等或高)。

集成的多路复用器具有出色的动态特性,可在信号眼图衰减最小的情况下实现转换,并且附加抖动极少。尽管 RX 和 TX 通道的共模电压不同,但是该器件的开关路径会部署自适应共模电压跟踪功能,确保两通道相同。

器件信息(1)

| 器件型号 | 封装 | 封装尺寸(标称值) |

|---|---|---|

| HD3SS3220 | VQFN RNH (30) | 2.50mm x 4.50mm |

| HD3SS3220I |

(1) 有关所有的可用封装,请参阅数据表末尾的可订购米6体育平台手机版_好二三四附录。

简化原理图

简化原理图 典型应用

典型应用