ZHCSE61A July 2015 – September 2015 ISO7830

PRODUCTION DATA.

- 1 特性

- 2 应用范围

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Power Rating

- 6.6 Electrical Characteristics, 5 V

- 6.7 Electrical Characteristics, 3.3 V

- 6.8 Electrical Characteristics, 2.5 V

- 6.9 Switching Characteristics, 5 V

- 6.10 Switching Characteristics, 3.3 V

- 6.11 Switching Characteristics, 2.5 V

- 6.12 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- DWW|16

- DW|16

散热焊盘机械数据 (封装 | 引脚)

订购信息

9 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

9.1 Application Information

The ISO7831 is a high-performance, quad-channel digital isolator with 5.7 kVRMS isolation voltage. The device comes with enable pins on each side which can be used to put the respective outputs in high impedance for multi master driving applications and reduce power consumption. ISO7831 uses single-ended CMOS-logic switching technology. Its supply voltage range is from 2.25 V to 5.5 V for both supplies, VCC1 and VCC2. When designing with digital isolators, it is important to keep in mind that due to the single-ended design structure, digital isolators do not conform to any specific interface standard and are only intended for isolating single-ended CMOS or TTL digital signal lines. The isolator is typically placed between the data controller (that is, μC or UART), and a data converter or a line transceiver, regardless of the interface type or standard.

9.2 Typical Application

The Isolated SPI Interface is shown in Figure 16.

Figure 16. Isolated SPI Interface for an Analog Input Module With 16 Input

Figure 16. Isolated SPI Interface for an Analog Input Module With 16 Input

9.2.1 Design Requirements

For ISO7831, use the parameters shown in Table 2.

Table 2. Design Parameters

| PARAMETER | VALUE |

|---|---|

| Supply voltage | 2.25 to 5.5 V |

| Decoupling capacitor between VCC1 and GND1 | 0.1 µF |

| Decoupling capacitor from VCC2 and GND2 | 0.1 µF |

9.2.2 Detailed Design Procedure

Unlike optocouplers, which need external components to improve performance, provide bias, or limit current, ISO7831 only needs two external bypass capacitors to operate.

Figure 17. Typical ISO7830 Circuit Hook-up

Figure 17. Typical ISO7830 Circuit Hook-up

9.2.2.1 Electromagnetic Compatibility (EMC) Considerations

Many applications in harsh industrial environment are sensitive to disturbances such as electrostatic discharge (ESD), electrical fast transient (EFT), surge and electromagnetic emissions. These electromagnetic disturbances are regulated by international standards such as IEC 61000-4-x and CISPR 22. Although system-level performance and reliability depends, to a large extent, on the application board design and layout, the ISO7830 incorporate many chip-level design improvements for overall system robustness. Some of these improvements include:

- Robust ESD protection for input and output signal pins and inter-chip bond pads.

- Low-resistance connectivity of ESD cells to supply and ground pins.

- Enhanced performance of high voltage isolation capacitor for better tolerance of ESD, EFT and surge events.

- Bigger on-chip decoupling capacitors to bypass undesirable high energy signals through a low impedance path.

- PMOS and NMOS devices isolated from each other by using guard rings to avoid triggering of parasitic SCRs.

- Reduced common mode currents across the isolation barrier by ensuring purely differential internal operation.

9.2.3 Application Curve

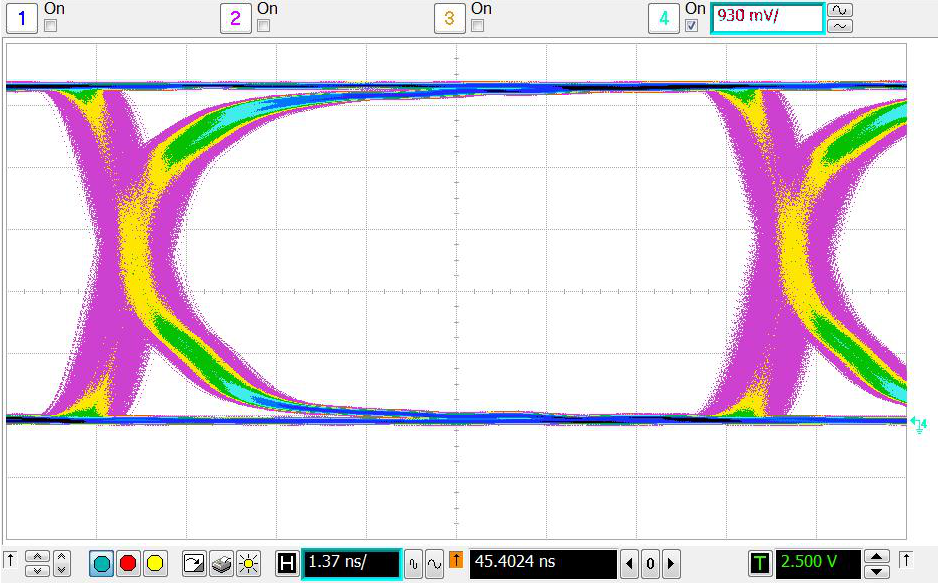

Typical eye diagram of ISO7830 indicate low jitter and wide open eye at the maximum data rate of 100 Mbps.

Figure 18. Eye Diagram at 100 Mbps PRBS, 5 V and 25°C

Figure 18. Eye Diagram at 100 Mbps PRBS, 5 V and 25°C