ZHCSW60 November 2023 – April 2024 IWRL6432AOP

ADVANCE INFORMATION

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 功能方框图

- 5 器件比较

- 6 终端配置和功能

-

7 规格

- 7.1 绝对最大额定值

- 7.2 ESD 等级

- 7.3 上电小时数 (POH)

- 7.4 建议运行条件

- 7.5 一次性可编程 (OTP) 电子保险丝的 VPP 规格

- 7.6 电源规格

- 7.7 节电模式

- 7.8 每个电压轨的峰值电流要求

- 7.9 支持的 DFE 特性

- 7.10 射频规格

- 7.11 CPU 规格

- 7.12 热阻特性

- 7.13 天线辐射方向图

- 7.14 天线位置

- 7.15 时序和开关特性

- 8 详细说明

- 9 监控和诊断

- 10应用、实施和布局

- 11器件和文档支持

- 12修订历史记录

- 13机械、封装和可订购信息

7.9 支持的 DFE 特性

- TX 输出退避

-

从 0dB 到 26dB TX 退避,步长为 1dB

-

- RX 增益

- 实际 RX 通道

- 总 RX 增益范围为 30dB 至 40dB,步长为 2dB

- VCO

- 单个 VCO 覆盖高达 7GHz 的整个射频扫描带宽。

- 高通滤波器

- 支持转角频率选项 175kHz、350kHz、700kHz、1400kHz

- 仅一阶高通滤波器

- 低通滤波器

- 支持的最大中频带宽为 5MHz

- 40dB 阻带抑制,支持两个滤波选项

- 90% 可见性 — 中频带宽是奈奎斯特的 90%(由于滤波器长度较大而具有更长的趋稳时间)

- 80% 可见性 — 中频带宽是奈奎斯特的 80% 并且由于更短的稳定时间而快 30%(与 90% 可见性相比)

- 支持的 ADC 采样速率

- 1.0、1.25、1.667、2.0、2.5、4.0、5.0、6.667、7.692、10.0、12.5Msps

- 计时引擎

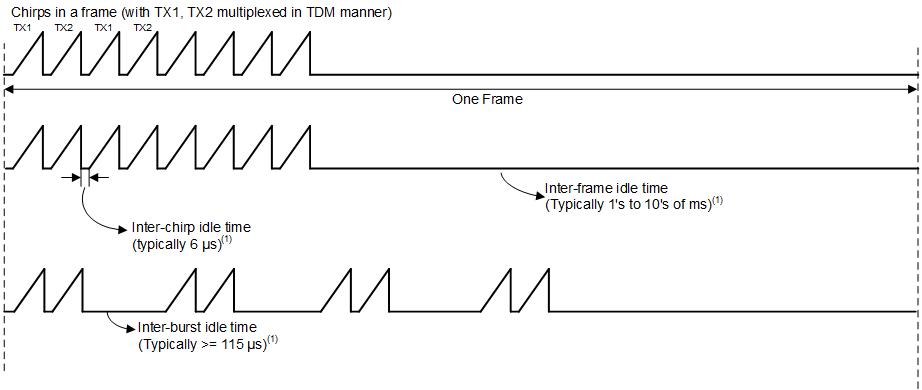

- 支持线性调频脉冲、突发和帧

- 与较长的突发空闲时间相比,较长的帧空闲时间可以节省较多功耗。此外,与较长的突发空闲时间相比,较长的线性调频脉冲空闲时间所节省的功耗较少。有关更多详细信息,请参阅毫米波传感估算器中的功率计算器。

- 可跨密集线性调频脉冲的线性调频脉冲累积(计算平均值)来降低存储器要求

- 配置每个线性调频脉冲抖动参数

- 支持线性调频脉冲、突发和帧

- 请参阅 DFP API 文档