ZHCSW60 November 2023 – April 2024 IWRL6432AOP

ADVANCE INFORMATION

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 功能方框图

- 5 器件比较

- 6 终端配置和功能

-

7 规格

- 7.1 绝对最大额定值

- 7.2 ESD 等级

- 7.3 上电小时数 (POH)

- 7.4 建议运行条件

- 7.5 一次性可编程 (OTP) 电子保险丝的 VPP 规格

- 7.6 电源规格

- 7.7 节电模式

- 7.8 每个电压轨的峰值电流要求

- 7.9 支持的 DFE 特性

- 7.10 射频规格

- 7.11 CPU 规格

- 7.12 热阻特性

- 7.13 天线辐射方向图

- 7.14 天线位置

- 7.15 时序和开关特性

- 8 详细说明

- 9 监控和诊断

- 10应用、实施和布局

- 11器件和文档支持

- 12修订历史记录

- 13机械、封装和可订购信息

8.3.5 处理器子系统

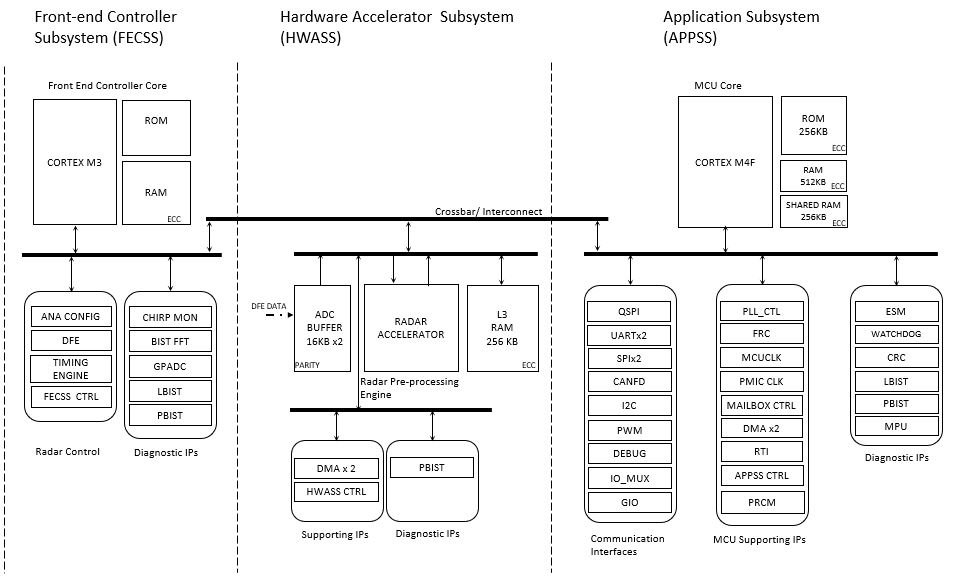

图 8-4 处理器子系统

图 8-4 处理器子系统图 8-4 展示了 IWRL6432AOP 器件中客户可编程处理器子系统的方框图。概括来说,有两个客户可编程子系统,图中用虚线隔开。左侧显示了 HWA,它是一种用于高性能(64 位,80MHz)以及关联的外设数据传输的高带宽互连。RDIF 接口用于测量数据输出、L3 雷达数据立方体存储器、ADC 缓冲器、CRC 引擎和数据握手存储器(互连上提供的额外存储器)。

图的右侧显示了主子系统。主子系统是器件的主要控制器,控制着所有器件外设和器件的通用活动。主子系统包含 Cortex-M4F 处理器和关联的外设和通用元件,例如 DMA、CRC 和通过外设中心资源(PCR 互连)连接到主互连的外设(I2C、UART、SPI、CAN、PMIC 时钟模块、PWM、 等)。