SNVS153F May 2001 – September 2016 LM2698

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

10 Layout

10.1 Layout Guidelines

The GND pin and the NC pin is recommended to be connected by a short trace as shown in Layout Examples.

Table 2 shows the thermal resistance using different scenarios.

10.2 Layout Examples

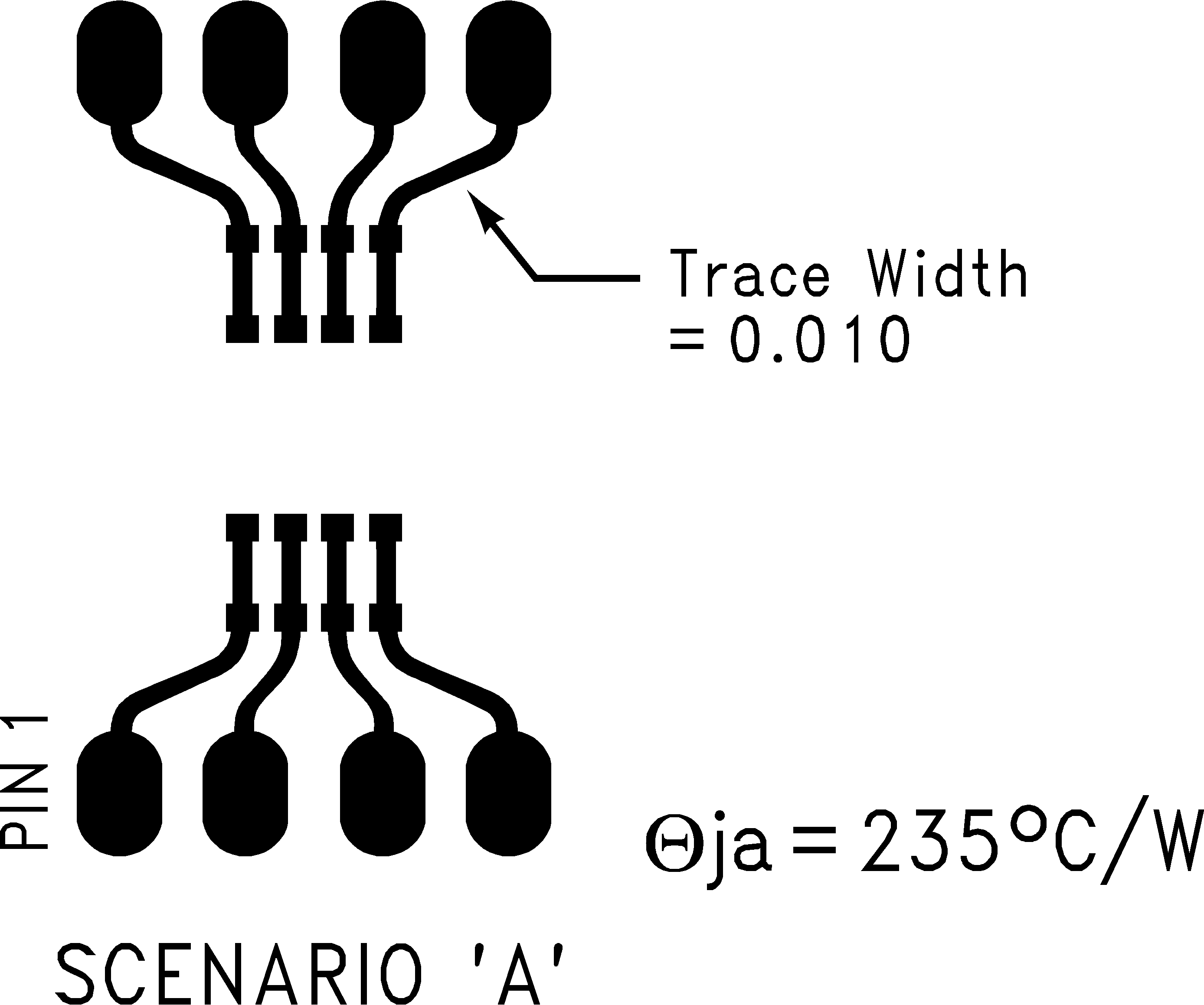

| Junction to ambient thermal resistance (no external heat sink) for the MSO8 package with minimal trace widths (0.010 inches) from the pins to the circuit. | ||

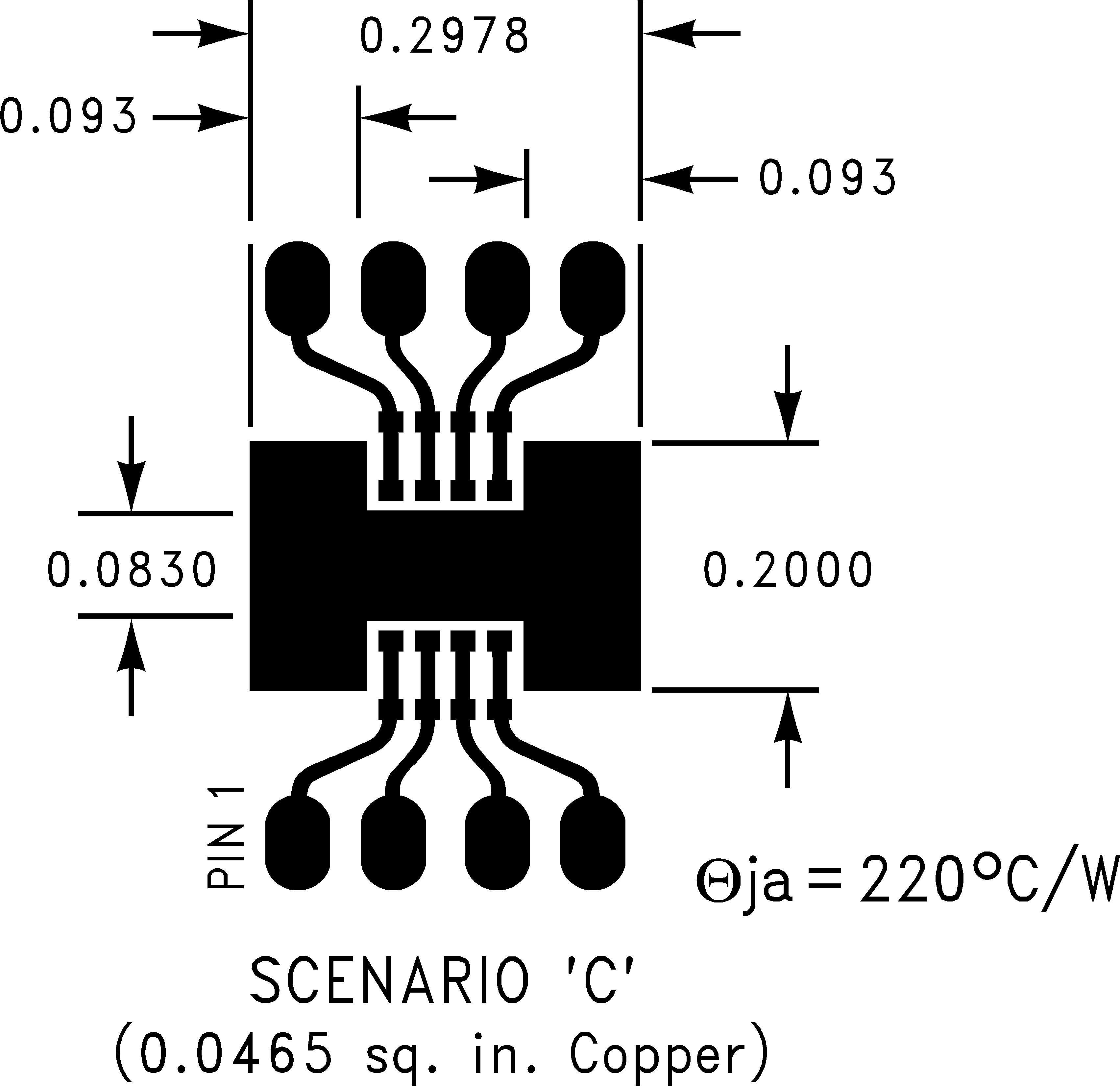

| Junction to ambient thermal resistance for the MSO8 package with minimal trace widths (0.010 inches) from the pins to the circuit and approximately 0.0465 sq. in. of copper heat sinking. | ||

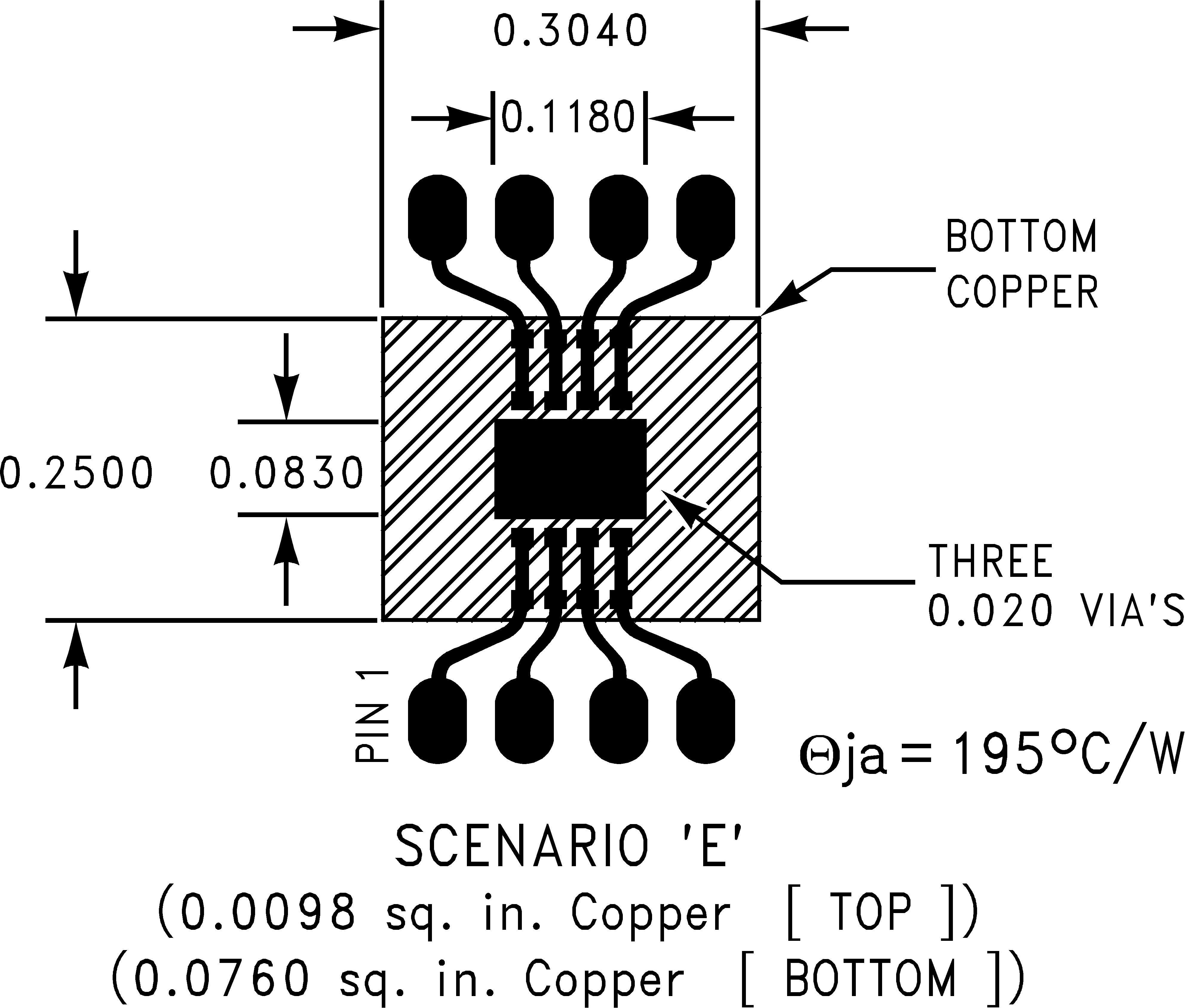

Junction to ambient thermal resistance for the MSO8 package with minimal trace widths (0.010 inches) from the pins to the circuit and approximately 0.0098 sq. in. of copper heat sinking on the top layer and 0.0760 sq. in. of copper heat sinking on the bottom layer, with three 0.020 in. vias connecting the planes.

Figure 29. Pad Layout Scenario 'E'

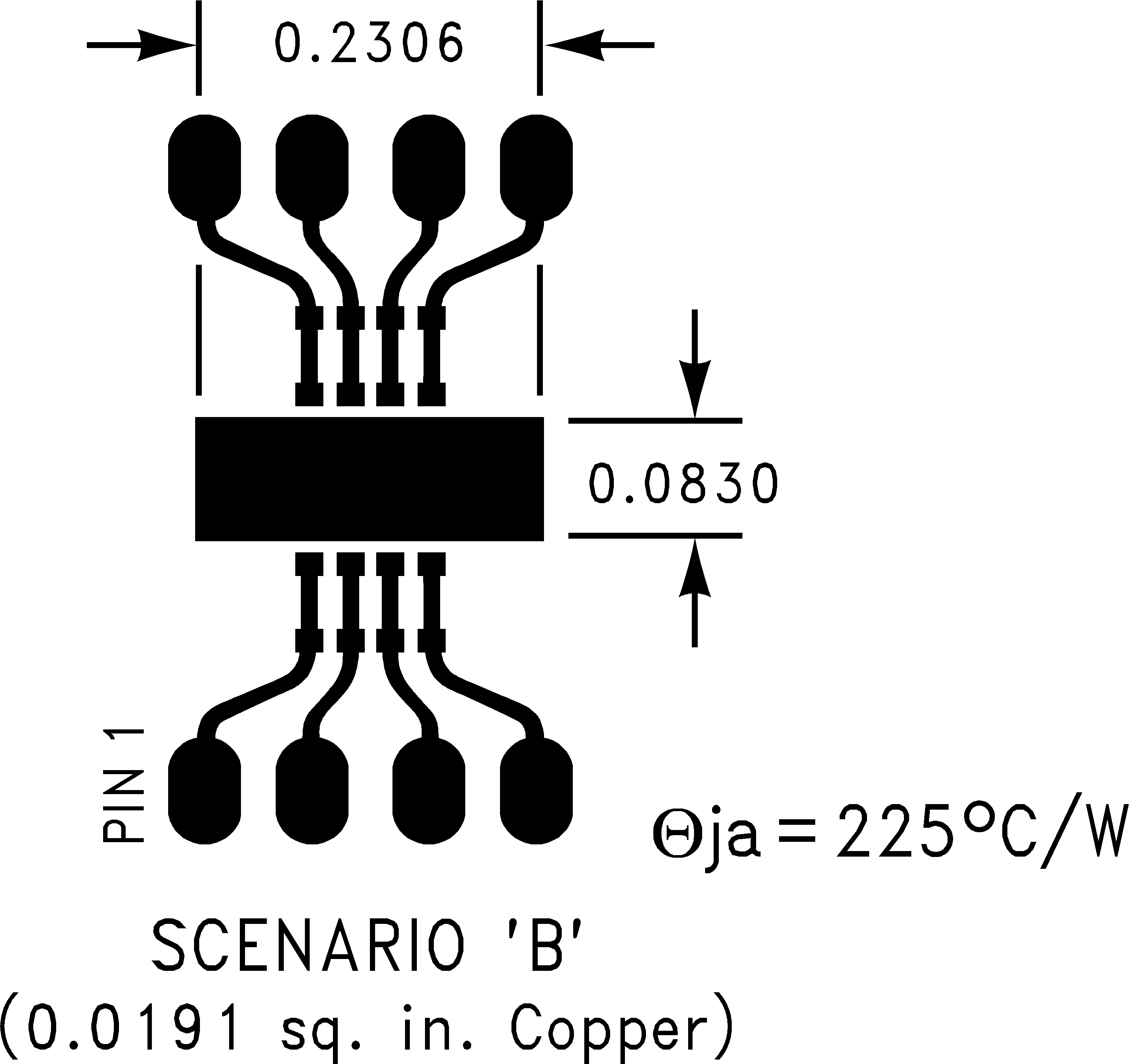

Junction to ambient thermal resistance for the MSO8 package with minimal trace widths (0.010 inches) from the pins to the circuit and approximately 0.0191 sq. in. of copper heat sinking.

Figure 26. Pad Layout Scenario 'B'

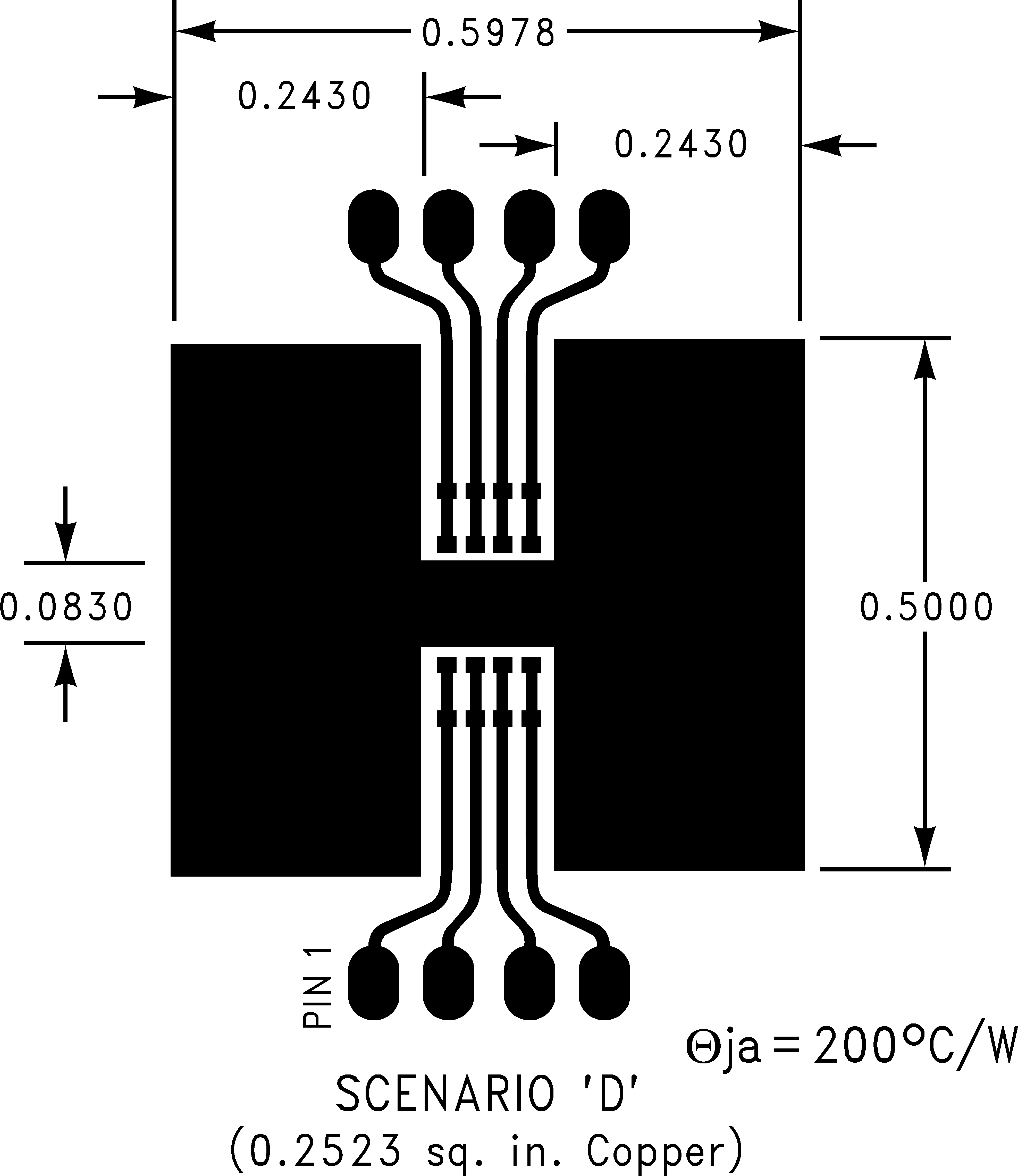

Junction to ambient thermal resistance for the MSO8 package with minimal trace widths (0.010 inches) from the pins to the circuit and approximately 0.2523 sq. in. of copper heat sinking.

Figure 28. Pad Layout Scenario 'D'