SNVS071C March 2000 – September 2015 LM2766

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

8 Detailed Description

8.1 Overview

The LM2766 CMOS charge-pump voltage converter operates as a voltage doubler for an input voltage in the range of 1.8 V to 5.5 V. Two low-cost capacitors and a diode (needed during start-up) are used in this circuit.

8.2 Functional Block Diagram

8.3 Feature Description

8.3.1 Test Circuit

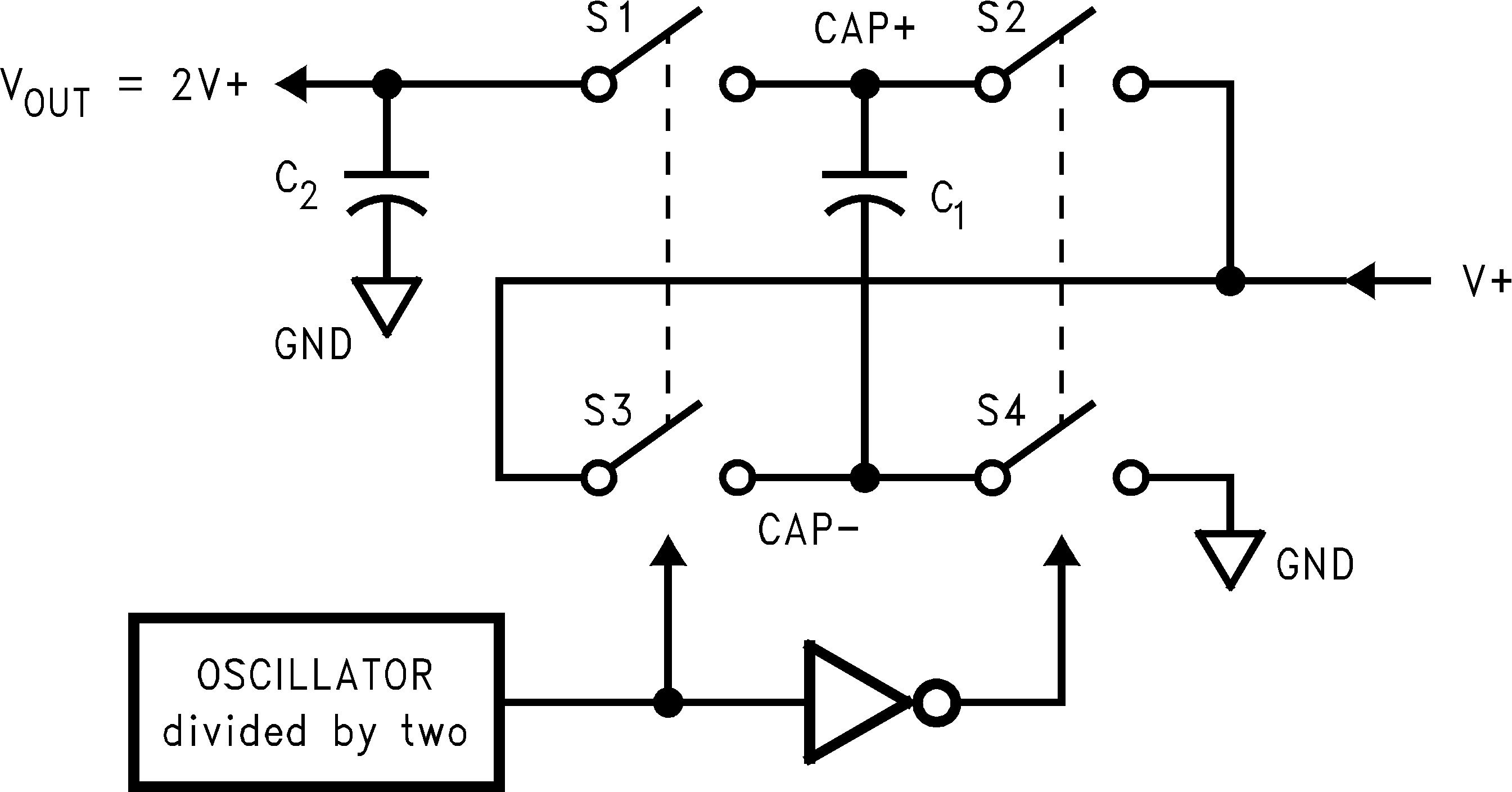

The LM2766 contains four large CMOS switches which are switched in a sequence to double the input supply voltage. Energy transfer and storage are provided by external capacitors. Figure 10 illustrates the voltage conversion scheme. When S2 and S4 are closed, C1 charges to the supply voltage V+. During this time interval, switches S1 and S3 are open. In the next time interval, S2 and S4 are open; at the same time, S1 and S3 are closed, the sum of the input voltage V+ and the voltage across C1 gives the 2 V+ output voltage when there is no load. The output voltage drop when a load is added is determined by the parasitic resistance (Rds(on) of the MOSFET switches and the ESR of the capacitors) and the charge transfer loss between capacitors. See Application and Implementation for further details.

Figure 10. Voltage Doubling Principle

Figure 10. Voltage Doubling Principle

8.4 Device Functional Modes

8.4.1 Shutdown Mode

A shutdown (SD) pin is available to disable the device and reduce the quiescent current to 0.1 µA. In normal operating mode, the SD pin is connected to V+. The device can be brought into the shutdown mode by applying to the SD pin a voltage less than 20% of the V+ pin voltage.