SNVS484H January 2007 – July 2015 LM5001 , LM5001-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Applications and Implementation

- 9 Layout

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

6 Specifications

6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| VIN to GND | 76 | V | ||

| SW to GND (Steady State) | –0.3 | 76 | V | |

| VCC, EN to GND | 14 | V | ||

| COMP, FB, RT to GND | –0.3 | 7 | V | |

| Maximum Junction Temperature | 150 | °C | ||

| Storage Temperature Range, Tstg | -65 | 150 | °C | |

6.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002(1) | ±2000 | V |

| Charged-device model (CDM), per AEC Q100-011 | ±750 | |||

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

6.3 Recommended Operating Conditions

| MIN | NOM | MAX | UNIT | |

|---|---|---|---|---|

| VIN | 3.1 | 75 | V | |

| Operating Junction Temperature | −40 | 125 | °C |

6.4 Thermal Information

| THERMAL METRIC | LM5001-Q1 | LM5001 | UNIT | |||

|---|---|---|---|---|---|---|

| SOIC | SOIC | WSON | ||||

| (8 PINS) | ||||||

| RθJA | Junction-to-ambient thermal resistance | 140 | 140 | 40 | °C/W | |

| RθJCtop | Junction-to-case (top) thermal resistance | 32 | 32 | 4.5 | ||

6.5 Electrical Characteristics

Minimum and Maximum limits are ensured through test, design, or statistical correlation, over the junction temperature (TJ) range of –40°C to +125°C. Typical values represent the most likely parametric norm at TJ = 25°C, and are provided for reference purposes only. VVIN = 10 V, RRT = 48.7 kΩ unless otherwise stated(1).(1) Min and Max limits are 100% production tested at 25°C. Limits over the operating temperature range are specified through correlation using Statistical Quality Control (SQC) methods. Limits are used to calculate TI’s Average Outgoing Quality Level (AOQL).

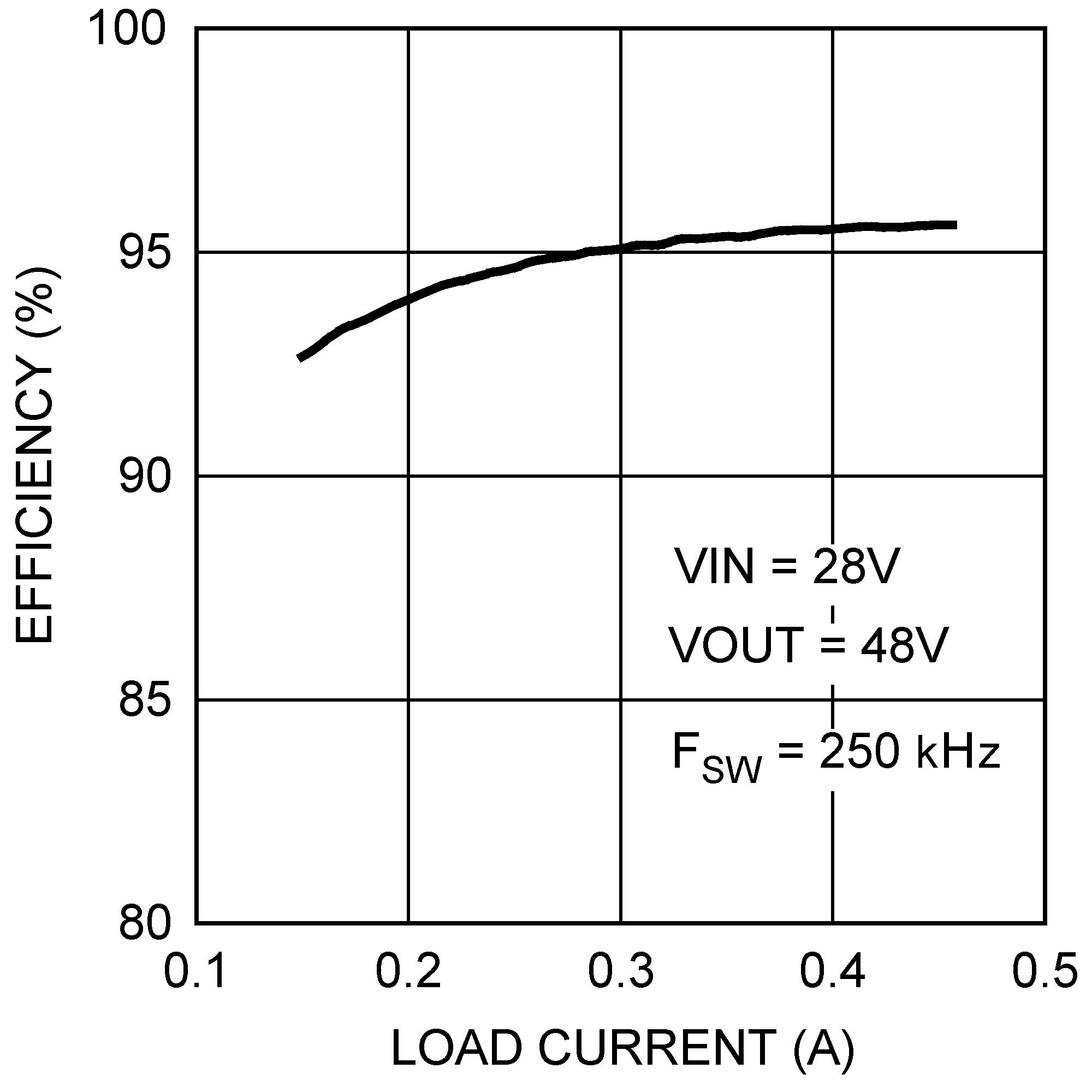

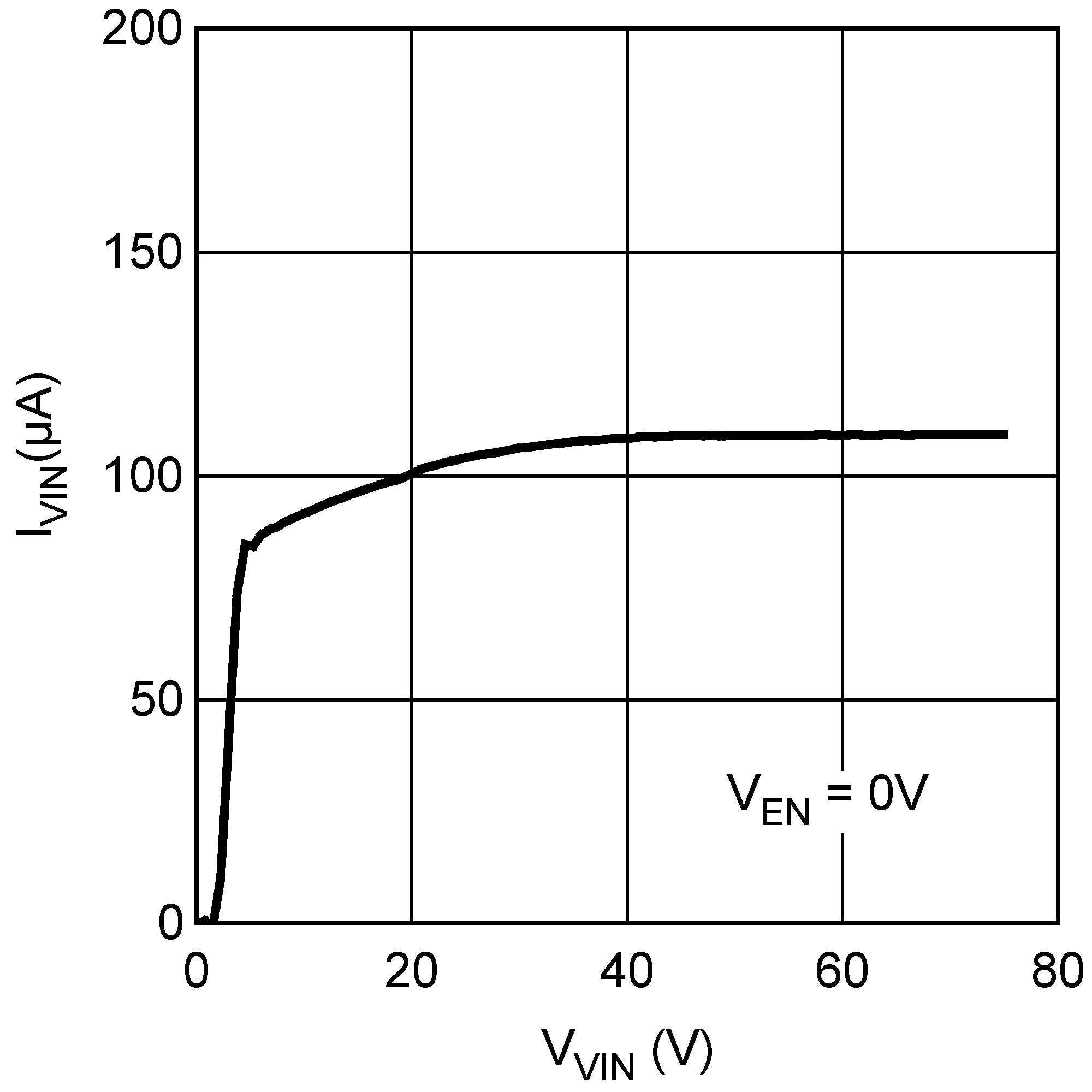

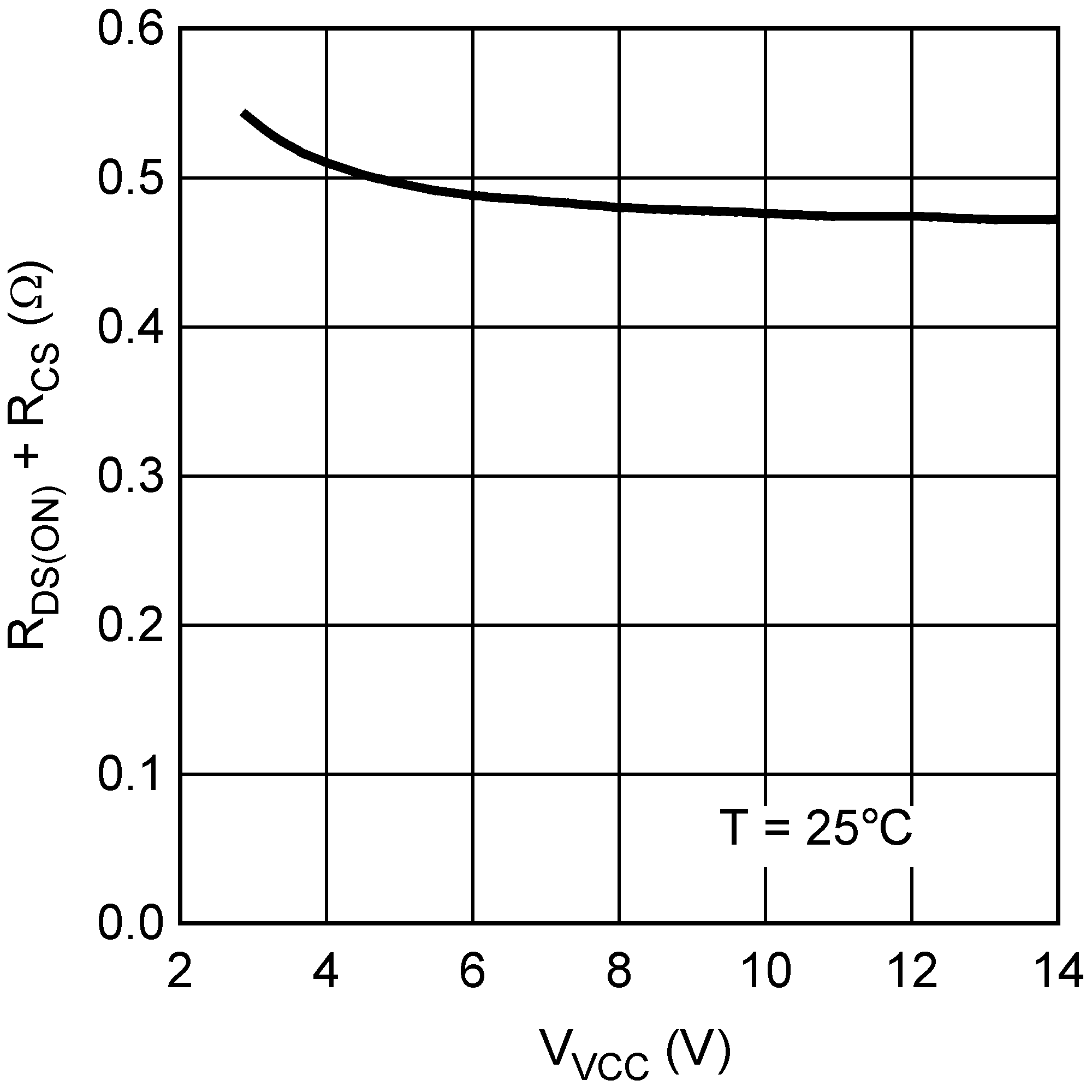

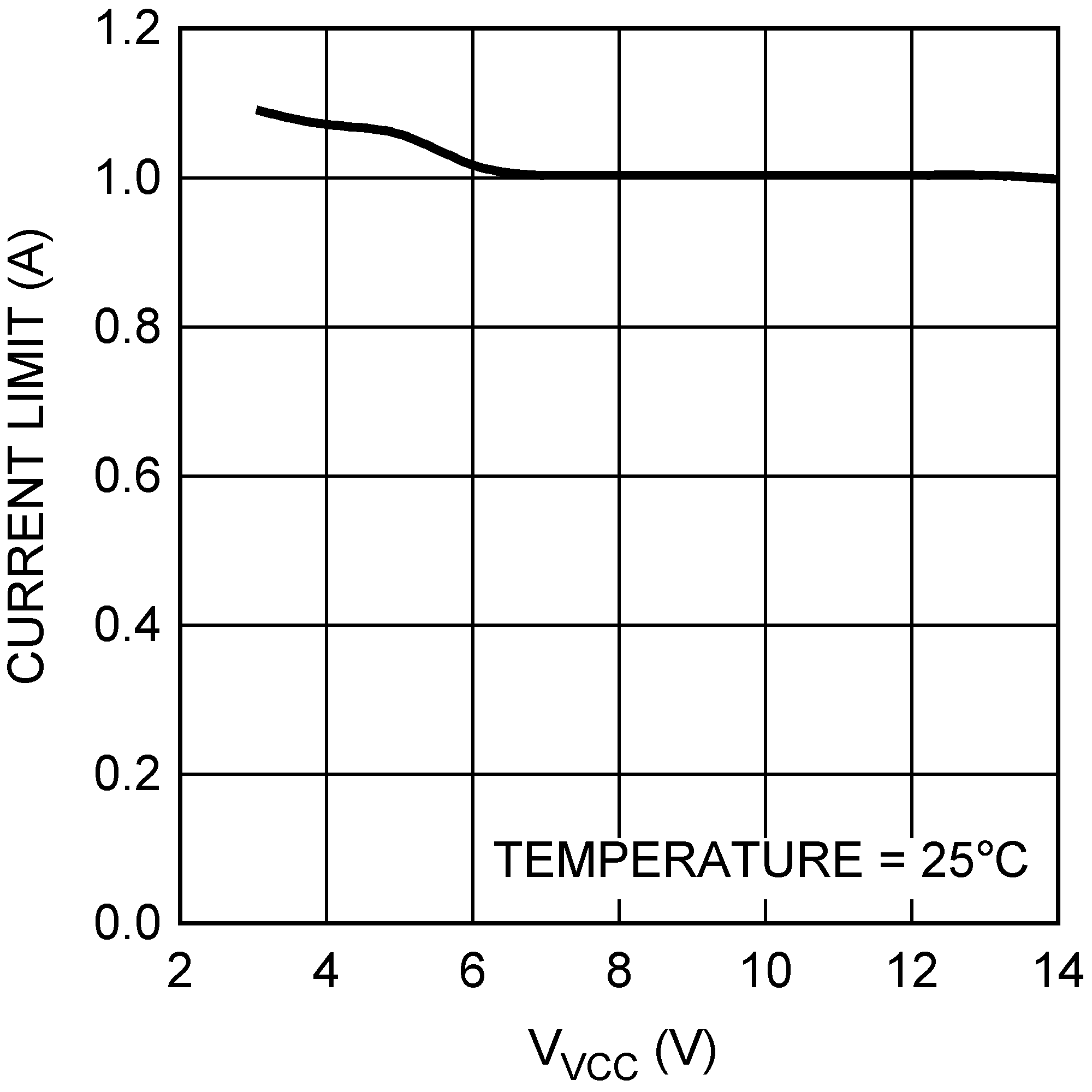

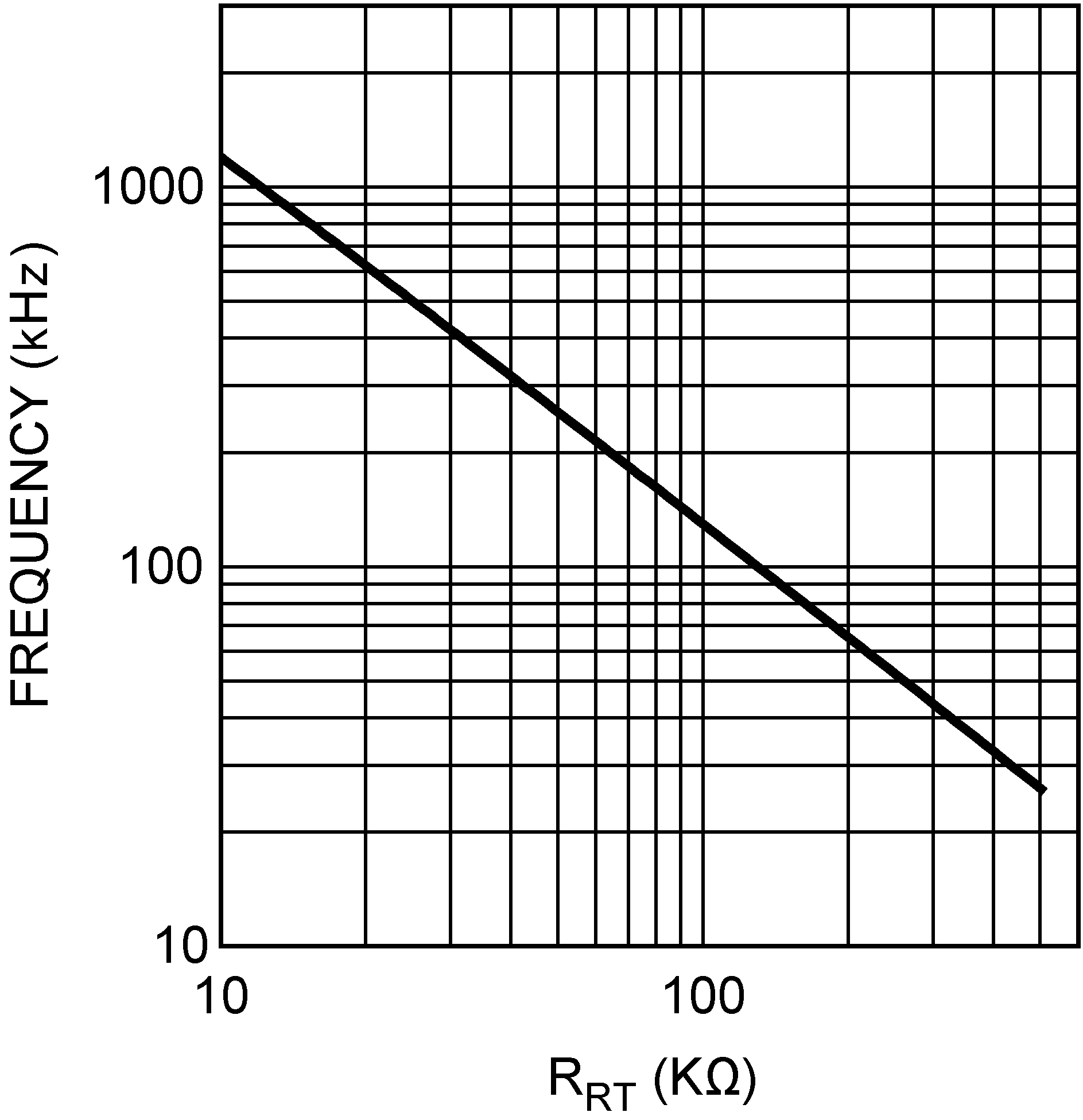

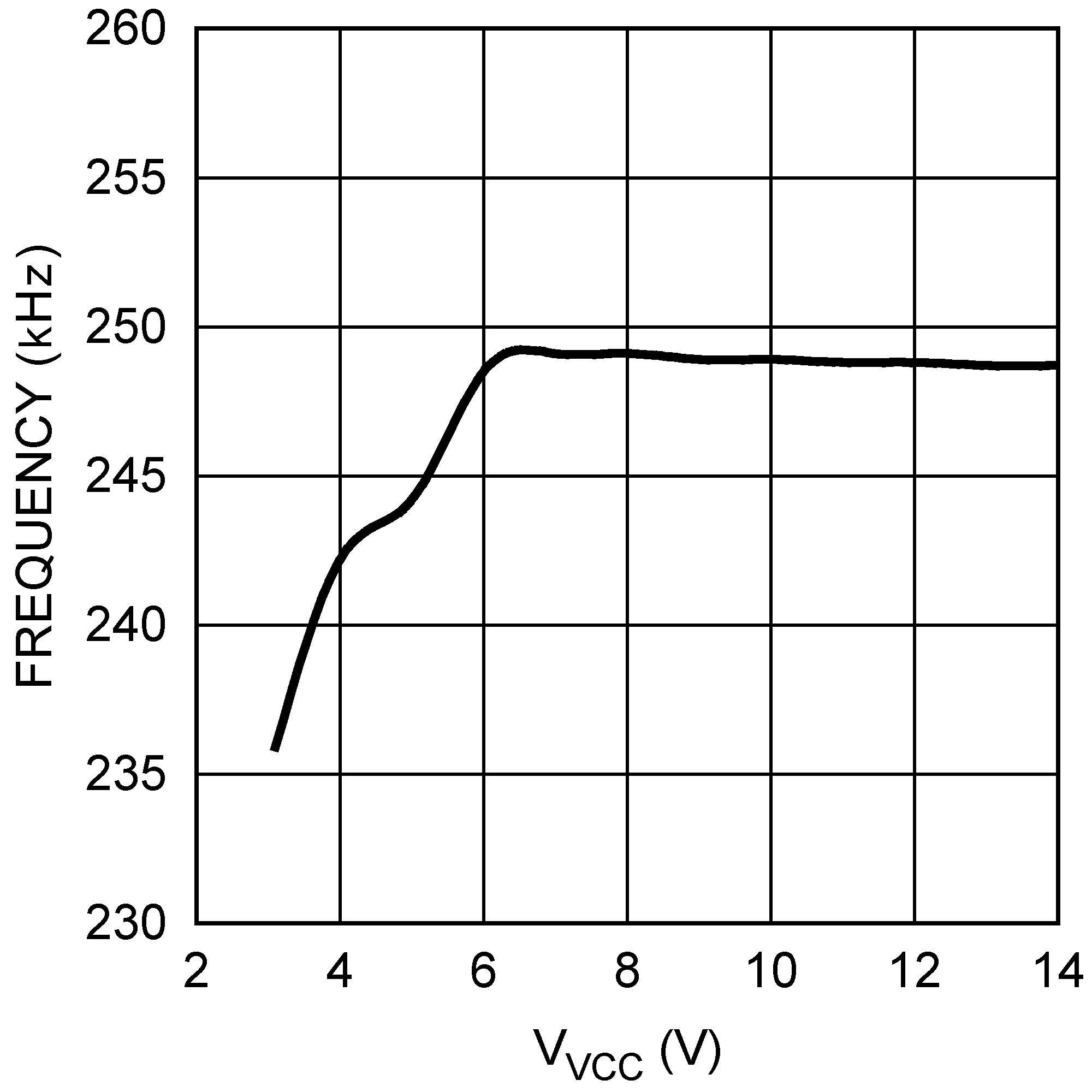

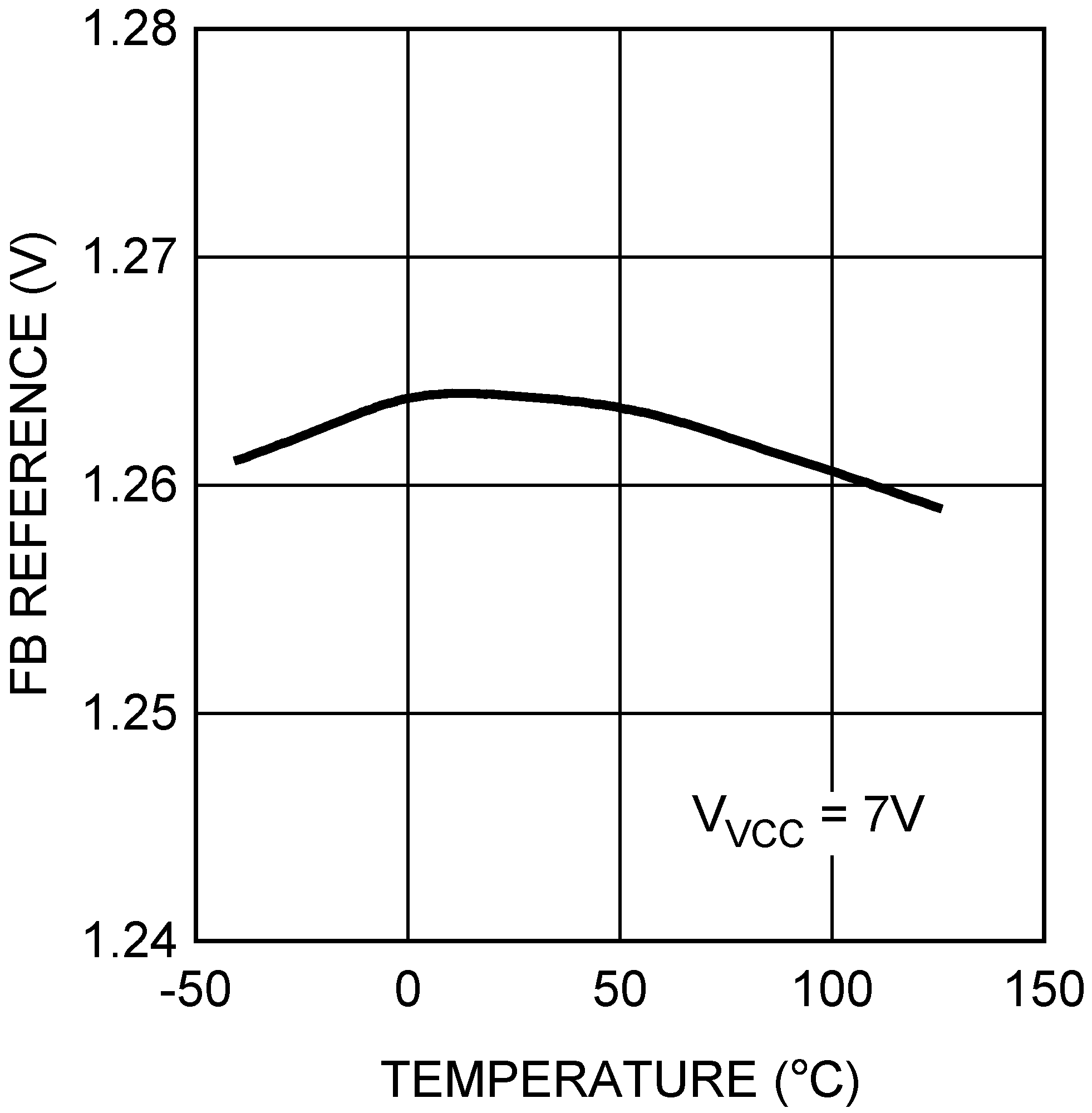

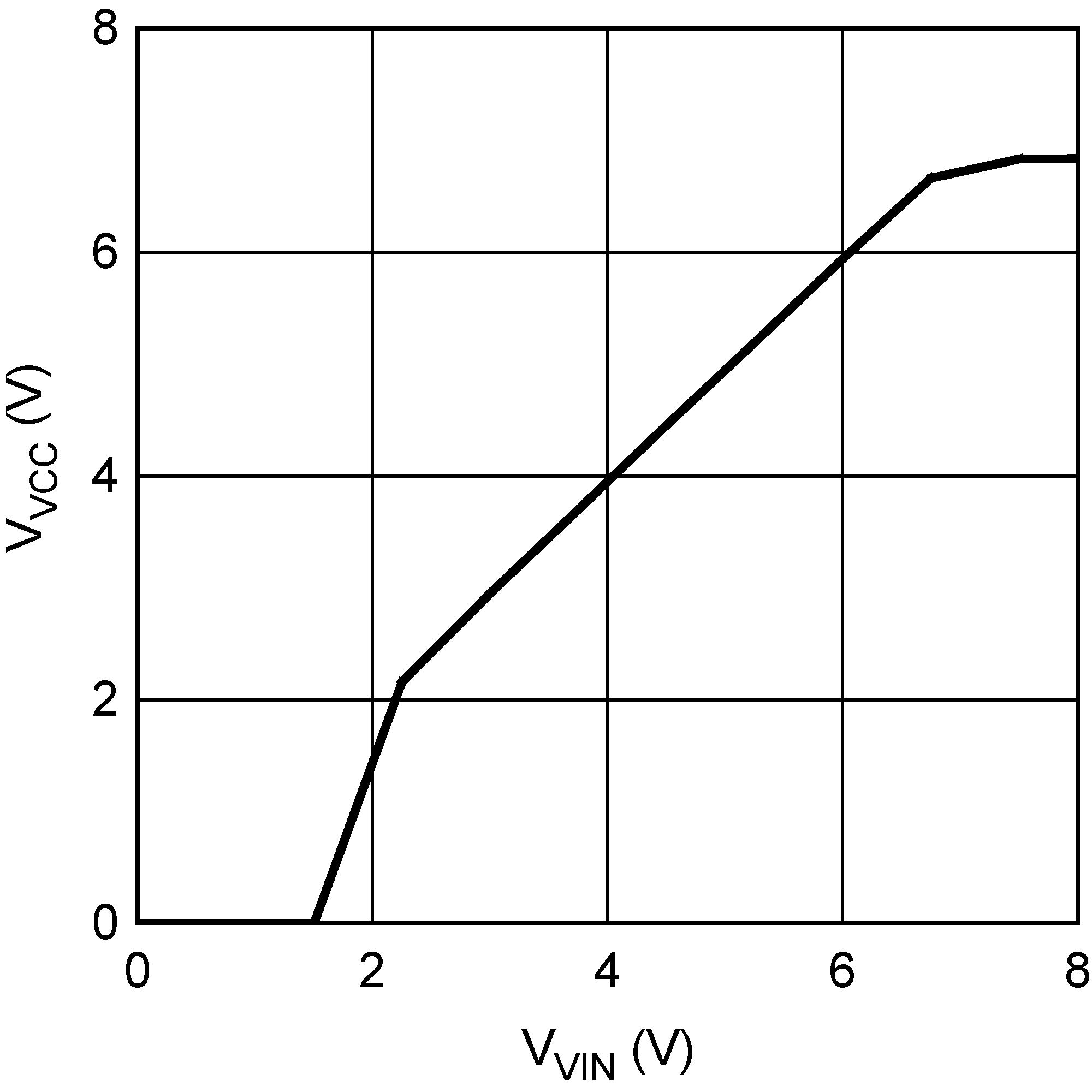

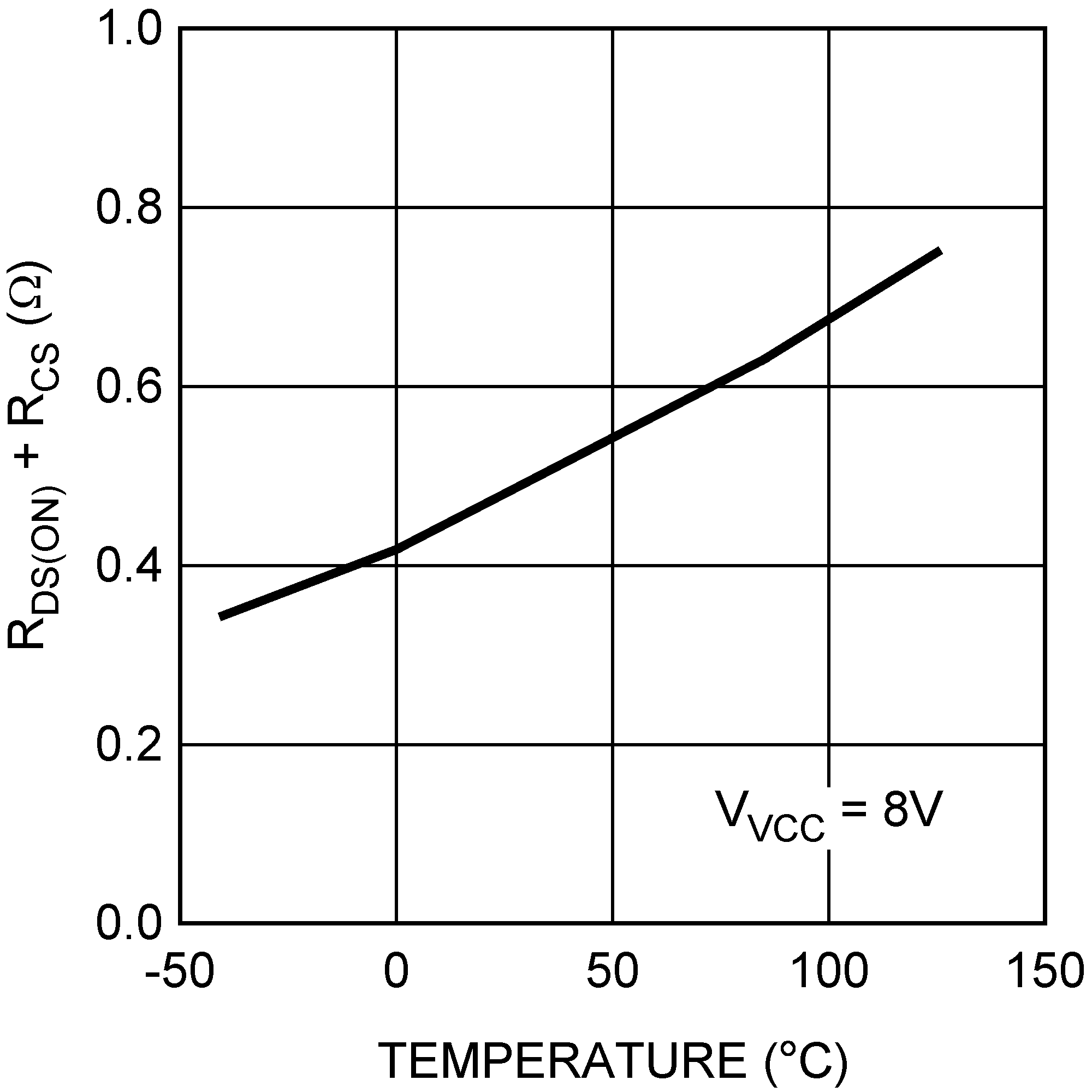

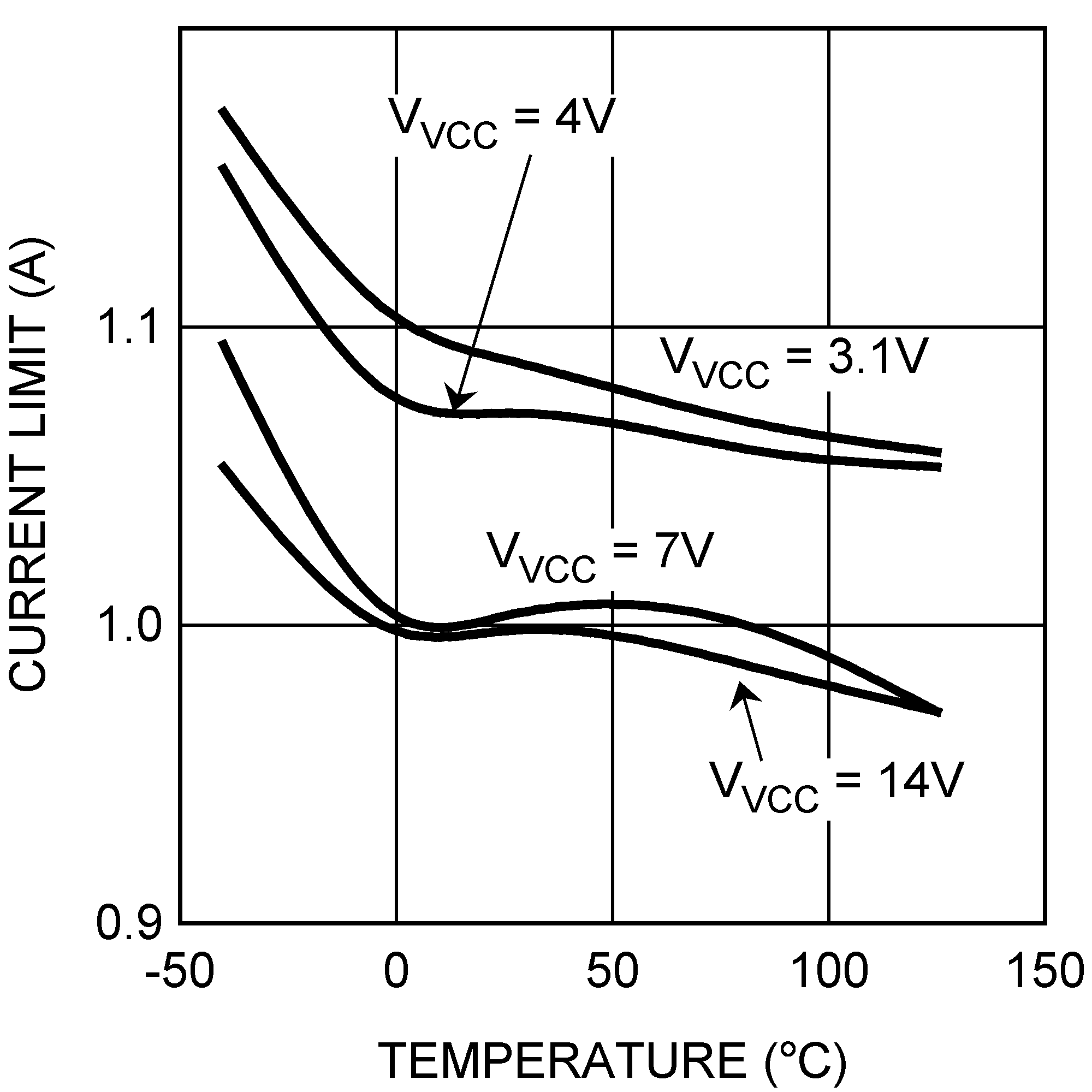

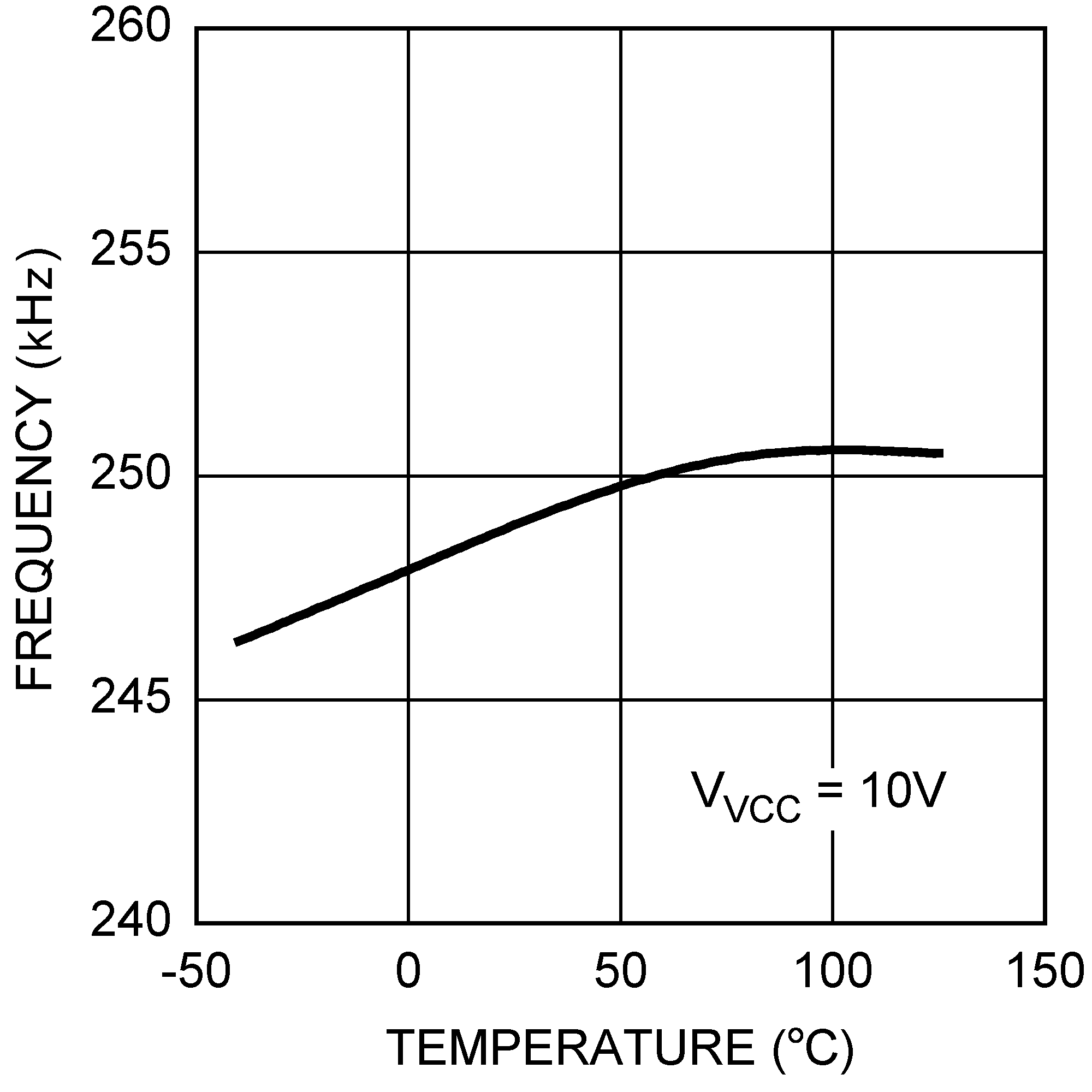

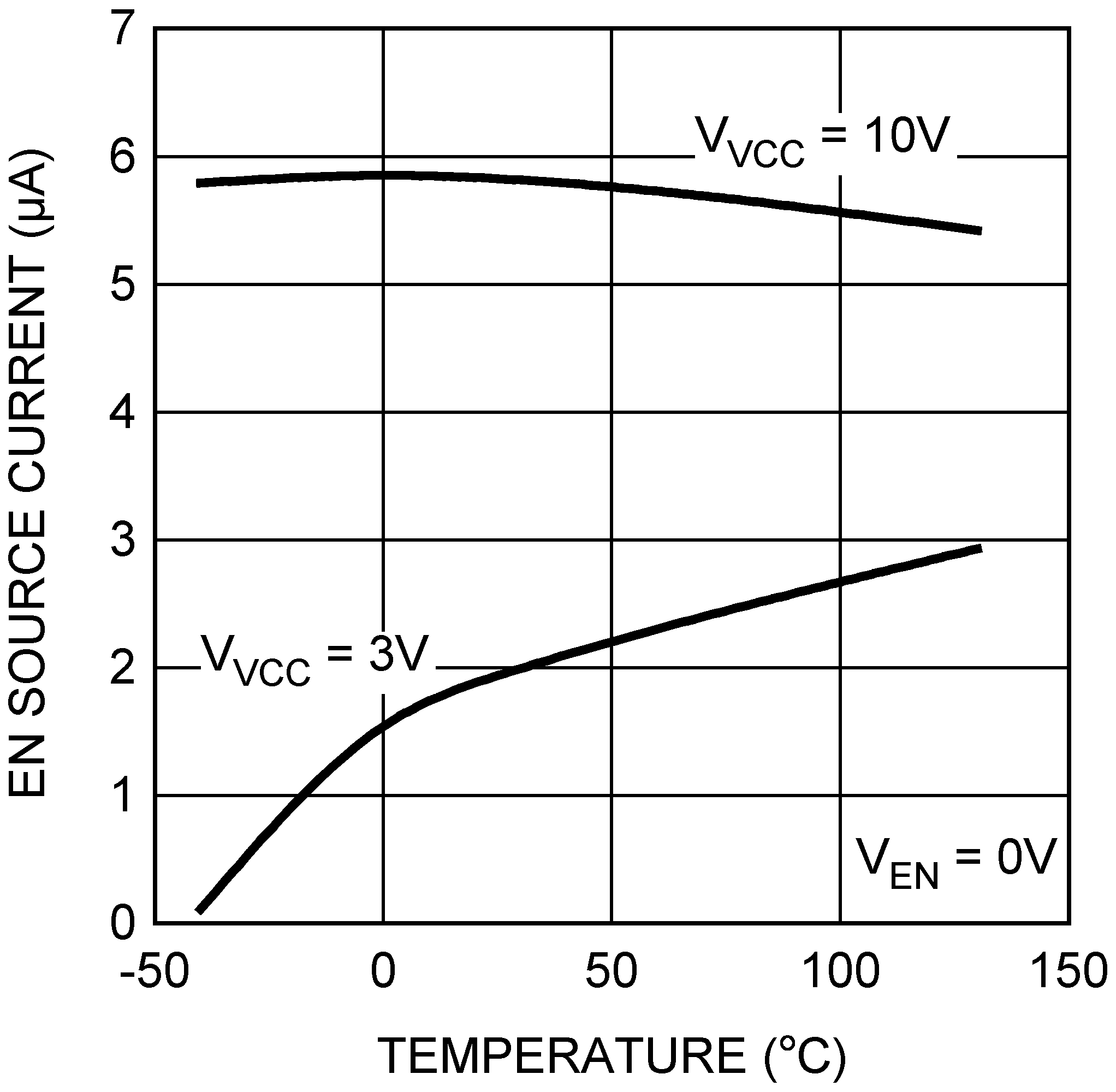

6.6 Typical Characteristics