ZHCSD65B SEPTEMBER 2013 – December 2014 LM5121 , LM5121-Q1

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Undervoltage Lockout (UVLO)

- 7.3.2 High Voltage VCC Regulator

- 7.3.3 Oscillator

- 7.3.4 Slope Compensation

- 7.3.5 Error Amplifier

- 7.3.6 PWM Comparator

- 7.3.7 Disconnection Switch Control

- 7.3.8 Soft-Start

- 7.3.9 HO and LO Drivers

- 7.3.10 Bypass Operation (VOUT = VIN)

- 7.3.11 Cycle-by-Cycle Current Limit

- 7.3.12 Circuit Breaker Function

- 7.3.13 Clock Synchronization

- 7.3.14 Maximum Duty Cycle

- 7.3.15 Thermal Protection

- 7.4 Device Functional Modes

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2

Detailed Design Procedure

- 8.2.2.1 Timing Resistor RT

- 8.2.2.2 UVLO Divider RUV2, RUV1

- 8.2.2.3 Input Inductor LIN

- 8.2.2.4 Current Sense Resistor RS

- 8.2.2.5 Current Sense Filter RCSFP, RCSFN, CCS

- 8.2.2.6 Slope Compensation Resistor RSLOPE

- 8.2.2.7 Output Capacitor COUT

- 8.2.2.8 Input Capacitor CIN

- 8.2.2.9 VIN Filter RVIN, CVIN

- 8.2.2.10 Bootstrap Capacitor CBST and Boost Diode DBST

- 8.2.2.11 VCC Capacitor CVCC

- 8.2.2.12 Output Voltage Divider RFB1, RFB2

- 8.2.2.13 Soft-Start Capacitor CSS

- 8.2.2.14 Restart Capacitor CRES

- 8.2.2.15 Low-Side Power Switch QL

- 8.2.2.16 High-Side Power Switch QH and Additional Parallel Schottky Diode

- 8.2.2.17 Snubber Components

- 8.2.2.18 Disconnect Switch QD Selection

- 8.2.2.19 Freewheeling Diode DF Selection

- 8.2.2.20 Loop Compensation Components CCOMP, RCOMP, CHF

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械封装和可订购信息

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

The LM5121 device is a step-up dc-dc converter. The device is typically used to convert a lower dc voltage to a higher dc voltage. Use the following design procedure to select component values for the LM5121 device. Alternately, use the WEBENCH® software to generate a complete design. The WEBENCH software uses an iterative design procedure and accesses a comprehensive database of components when generating a design. This section presents a simplified discussion of the design process.

8.1.1 Feedback Compensation

The open loop response of a boost regulator is the product of the modulator transfer function and the feedback transfer function. When plotted on a dB scale, the open loop gain is shown as the sum of modulator gain and feedback gain. The modulator transfer function of a current mode boost regulator including a power stage transfer function with an embedded current loop can be simplified as one pole, one zero and one Right Half Plane (RHP) zero system.

Modulator transfer function is defined as follows:

where

-

-

-

-

-

- n is the number of the phase.

If the ESR of COUT (RESR) is small enough and the RHP zero frequency is far away from the target crossover frequency, the modulator transfer function can be further simplified to one pole system and the voltage loop can be closed with only two loop compensation components, RCOMP and CCOMP, leaving a single pole response at the crossover frequency. A single pole response at the crossover frequency yields a very stable loop with 90 degrees of phase margin.

The feedback transfer function includes the feedback resistor divider and loop compensation of the error amplifier. RCOMP, CCOMP and optional CHF configure the error amplifier gain and phase characteristics, and create a pole at origin, a low frequency zero and a high frequency pole.

The feedback transfer function is defined as follows:

where

The pole at the origin minimizes output steady state error. The low frequency zero should be set to cancel the load pole of the modulator. The high frequency pole can be used to cancel the zero created by the output capacitor ESR or to decrease noise susceptibility of the error amplifier. By placing the low frequency zero an order of magnitude less than the crossover frequency, the maximum amount of phase boost is achieved at the crossover frequency. The high frequency pole should be set above the crossover frequency since the addition of CHF adds a pole in the feedback transfer function.

The crossover frequency (open loop bandwidth) is usually selected between one twentieth and one fifth of the switching frequency. In a simplified formula, the estimated crossover frequency can be defined as:

where

For higher crossover frequency, RCOMP can be increased, while proportionally decreasing CCOMP. Conversely, decreasing RCOMP while proportionally increasing CCOMP, results in lower bandwidth while keeping the same zero frequency in the feedback transfer function.

The modulator transfer function can be measured using a network analyzer and the feedback transfer function can be configured for the desired open loop transfer function. If the network analyzer is not available, step load transient tests can be performed to verify acceptable performance. The step load goal is minimum overshoot/undershoot with a damped response.

8.1.2 Sub-Harmonic Oscillation

Peak current mode regulator can exhibit unstable behavior when operating above 50% duty cycle. This behavior is known as sub-harmonic oscillation and is characterized by alternating wide and narrow pulses at the SW pin. Sub-harmonic oscillation can be prevented by adding a voltage ramp (slope compensation) on top of the sensed inductor current. By choosing K≥0.82~1.0, the sub-harmonic oscillation will be eliminated even with widely varying input voltage.

In time-domain analysis, the steady-state inductor current starting from an initial point returns to the same point. When the amplitude of an end cycle current error (dI1) caused by an initial perturbation (dI0) is less than the amplitude of dI0 or dI1/dI0 > –1, the perturbation naturally disappears after a few cycles. When dl1/dl0<-1, the initial perturbation no longer disappear, it results in sub-harmonic oscillation in the steady-state.

Figure 30. Effect of Initial Perturbation when dl1/dl0 < -1

Figure 30. Effect of Initial Perturbation when dl1/dl0 < -1

dI1/dI0 can be calculated as:

The relationship between dI1/dI0 and K factor is illustrated in the graphic below.

Figure 31. dl1/dl0 vs K Factor

Figure 31. dl1/dl0 vs K Factor

The absolute minimum value of K is 0.5. When K<0.5, the amplitude of dl1 is greater than the amplitude of dl0 and any initial perturbation results in sub-harmonic oscillation. If K=1, any initial perturbation will be removed in one switching cycle. This is known as one-cycle damping. When -1<dl1/dl0<0, any initial perturbation will be under-damped. Any perturbation will be over-damped when 0<dl1/dl0<1.

In the frequency-domain, Q, the quality factor of sampling gain term in modulator transfer function, is used to predict the tendency for sub-harmonic oscillation, which is defined as:

The relationship between Q and K factor is illustrated in Figure 32.

Figure 32. Sampling Gain Q vs K Factor

Figure 32. Sampling Gain Q vs K Factor

The recommended absolute minimum value of K is 0.5. High gain peaking when K is less than 0.5 results in sub-harmonic oscillation at fSW/2. A higher value of K factor may introduce additional phase shift near the crossover frequency, but has the benefit of reducing noise susceptibility in the current loop. The maximum allowable value of K factor can be calculated using the maximum crossover frequency equation and frequency analysis formulas in Table 1.

Table 1. Boost Regulator Frequency Analysis

| SIMPLIFIED FORMULA | COMPREHENSIVE FORMULA(1) | |

|---|---|---|

| MODULATOR TRANSER FUNCTION |

|

|

| Modulator DC gain (2) |

|

|

| RHP zero (2) |

|

|

| ESR zero |

|

|

| ESR pole | Not considered |

|

| Dominant load pole |

|

|

| Sampled gain inductor pole | Not considered |

|

| Quality factor | Not considered |

|

| Sub-harmonic double pole | Not considered |

or  |

| K factor | K = 1 |

|

| FEEDBACK TRANSFER FUNCTION |

|

|

| Feedback DC gain |

|

|

| Mid-band Gain |

|

|

| Low frequency zero |

|

|

| High frequency pole |

|

|

| OPEN LOOP RESPONSE |

|

|

| Crossover frequency (3)

(Open loop band width) |

|

Use graphic tool |

| Maximum cross over frequency(4) |

|

|

,

,  ,

,  , and COUT = COUT of each phase x n, where n = number of phases.

, and COUT = COUT of each phase x n, where n = number of phases.  ,

,  ,

,  ,

,  , and

, and  .

.8.1.3 Output Overvoltage Protection

Output overvoltage protection can be achieved by adding a simple external circuit. The output overvoltage protection circuit shown in Figure 33 shuts down the LM5121 when the output voltage exceeds the overvoltage threshold set by the zener diode.

Figure 33. Output Overvoltage Protection

Figure 33. Output Overvoltage Protection

8.1.4 Input Transient Suppression

Input over-voltage transient suppression can be achieved by adding a zener diode from DG to ground. The DS voltage will be clamped to the zener voltage minus the gate threshold voltage of the disconnection MOSFET switch.

Since the input clamping occurs in the active region of disconnection MOSFET switch, safe operating area and the thermal properties of the disconnection MOSFET switch should be carefully considered.

Figure 34. Input Transient Suppression

Figure 34. Input Transient Suppression

8.1.5 Inrush Current Limit Programming

Inrush current limit level can be lower than the cycle-by-cycle current limit level by adding a simple external circuit. The external inrush current limit programming circuit shown in Figure 35 and Figure 36 pull down CSN pin during inrush current limiting. Also, this configuration enables latch-off mode circuit breaker.

Figure 35. Inrush Current Limit Programming #1

Figure 35. Inrush Current Limit Programming #1

Figure 36. Inrush Current Limit Programming #2

Figure 36. Inrush Current Limit Programming #2

8.1.6 Reverse Battery Protection + Disconnect Switch Control

Figure 37. Reverse Battery Protection + Disconnection Switch

Figure 37. Reverse Battery Protection + Disconnection Switch

Figure 38. Reverse Battery Protection

Figure 38. Reverse Battery Protection

8.2 Typical Application

Figure 39. Schematic

Figure 39. Schematic

8.2.1 Design Requirements

| DESIGN PARAMETERS | VALUE |

|---|---|

| Output Voltage (VOUT) | 12 V |

| Full Load Current (IOUT) | 2 A |

| Output Power | 24 W |

| Minimum Input Voltage (VIN(MIN)) | 3 V (5.7 V for start-up) |

| Typical Input Voltage (VIN(TYP)) | 9 V |

| Maximum Input Voltage (VIN(MAX)) | 12 V |

| Switching Frequency (fSW) | 250 kHz |

| Disconnection Switch Control | Yes |

8.2.2 Detailed Design Procedure

8.2.2.1 Timing Resistor RT

Generally, higher frequency applications are smaller but have higher losses. Operation at 250 kHz is selected for this example as a reasonable compromise between small size and high-efficiency. The value of RT for 250 kHz switching frequency is calculated as follows:

A standard value of 36.5 kΩ is chosen for RT.

8.2.2.2 UVLO Divider RUV2, RUV1

The desired startup voltage and the hysteresis are set by the voltage divider RUV2, RUV1. The UVLO shutdown voltage should be high enough to fully enhance the low-side N-channel MOSFET switch. For this design, the startup voltage is set to 5.5 V which is 0.2 V below 5.7 V. VHYS is set to 3.7 V. This results 1.8 V of VIN(SHUTDOWN). The values of RUV2, RUV1 are calculated as follows:

A standard value of 365 kΩ is selected for RUV2. RUV1 is selected to be a standard value of 107 kΩ.

8.2.2.3 Input Inductor LIN

The inductor ripple current is typically set between 20% and 40% of the full load current, as a good compromise between core loss and copper loss of the inductor. Higher ripple current allows a smaller inductor size, but places more of a burden on the output capacitor to smooth the ripple voltage on the output. For this example, a ripple ratio (RR) of 0.3, 30% of the input current was chosen. Knowing the switching frequency and the typical output voltage, the inductor value can be calculated as follows:

The closest standard value of 10 μH was chosen for LIN.

The saturation current rating of the inductor should be greater than the peak inductor current, which is calculated at the minimum input voltage and full load. A 2.7 V startup voltage is used to conservatively estimate the peak inductor current.

8.2.2.4 Current Sense Resistor RS

The peak input current limit threshold should be set 20~50% higher than the required peak current at low input voltage and full load, accounting for tolerances. For this example, 20% is margin is chosen.

A closest standard value of 7 mΩ is selected for RS. The maximum power loss of RS is calculated as follows.

8.2.2.5 Current Sense Filter RCSFP, RCSFN, CCS

The current sense filter is optional. 100 pF for CCS and 100 Ω for RCSFP and RCSFN are normal recommendations. Because CSP and CSN pins are high impedance, CCS should be placed physically as close to the device.

Figure 40. Current Sense Filter

Figure 40. Current Sense Filter

8.2.2.6 Slope Compensation Resistor RSLOPE

The K value is selected to be 1 at the minimum input voltage. RSLOPE should be selected such that the sum of sensed inductor current and slope compensation is less than COMP output high voltage.

A closest standard value of 95.3 kΩ is selected for RSLOPE.

8.2.2.7 Output Capacitor COUT

The output capacitors smooth the output voltage ripple and provide a source of charge during transient loading conditions. Also the output capacitors reduce the output voltage overshoot when the load is suddenly disconnected.

The ripple current rating of the output capacitor should be carefully considered. In boost regulator, the output is supplied by discontinuous current and the ripple current requirement is usually high. In practice, the ripple current requirement can be dramatically reduced by placing high quality ceramic capacitors closer to the high side MOSFET switch than the bulk aluminum capacitors.

The output voltage ripple is dominated by the ESR of the output capacitors. Parallel output capacitors are a good choice to minimize effective ESR and split the output ripple current into multiple capacitors.

In this example, three 330 µF aluminum capacitors are used to share the output ripple current and source the required charge. The maximum output ripple current can be calculated at the minimum input voltage as follows:

Assuming 60 mΩ of ESR per output capacitor, the output voltage ripple at the minimum input voltage is calculated as follows:

In practice, four 10 µF ceramic capacitors are additionally placed before the bulk aluminum capacitors to reduce the output voltage ripple and share the output ripple current.

8.2.2.8 Input Capacitor CIN

The input capacitors smooth the input voltage ripple. Assuming high quality ceramic capacitors are used for the input capacitors, the maximum input voltage ripple which occurs when the input voltage is half of the output voltage can be calculated as follows:

The value of input capacitor is also a function of source impedance, the impedance of source power supply. More input capacitor will be required to prevent a chatter condition during power up if the impedance of source power supply is not low.

8.2.2.9 VIN Filter RVIN, CVIN

An R-C filter (RVIN, CVIN) on the VIN pin is optional. It is not required if the CIN capacitors are high quality ceramic capacitors and placed physically close to the device. The filter helps to prevent faults caused by high frequency switching noise injection into the VIN pin. A 0.47 μF ceramic capacitor is used this example. Recommended filter values are 3 Ω for RVIN and 0.47 µF for CVIN . A larger filter with 2.2 µ to 4.7 µF CVIN is recommended when the input voltage is lower than 8 V or when the required duty cycle is close to the maximum duty cycle limit.

Figure 41. VIN Filter

Figure 41. VIN Filter

8.2.2.10 Bootstrap Capacitor CBST and Boost Diode DBST

The bootstrap capacitor between the BST and SW pins supplies the gate current to charge the high-side N-channel MOSFET gate during each turn-on cycle and also supplies recovery charge for the bootstrap diode. The peak current can be several amperes. The recommended value of the bootstrap capacitor is 0.1 μF. CBST should be a good quality, low ESR, ceramic capacitor located at the pins of the device to minimize potentially damaging voltage transients caused by trace inductance. The minimum value for the bootstrap capacitor is calculated as follows:

Where QG is the high-side N-channel MOSFET gate charge and ΔVBST is the tolerable voltage droop on CBST, which is typically less than 5% of VCC or conservatively 0.15 V . In this example, the value of the BST capacitor (CBST) is 0.1 µF.

The voltage rating of DBST should be greater than the peak SW node voltage plus 16 V. A low leakage diode is mandatory for bypass operation. The leakage current of DBST should be low enough for the BST charge pump to maintain a sufficient high-side driver supply voltage at high temperature. A low leakage diode also prevents the possibility of excessive VCC voltage during shutdown, in high output voltage applications. If the diode leakage is excessive, a zener clamp or bleed resistor may be required on VCC. High-side driver supply voltage should be greater than the high-side N-channel MOSFET switch gate plateau at the minimum input voltage.

8.2.2.11 VCC Capacitor CVCC

The primary purpose of the VCC capacitor is to supply the peak transient currents of the LO driver and bootstrap diode as well as to provide stability for the VCC regulator. The peak driver currents can be several amperes. The value of CVCC should be at least 10 times greater than the value of CBST, and should be a good quality, low ESR, ceramic capacitor. CVCC should be placed close to the pins of the IC to minimize potentially damaging voltage transients caused by trace inductance. A value of 4.7 µF was selected for this design example.

8.2.2.12 Output Voltage Divider RFB1, RFB2

RFB1 and RFB2 set the output voltage level. The ratio of these resistors is calculated as follows:

The ratio between RCOMP and RFB2 determines the mid-band gain, AFB_MID. A larger value for RFB2 may require a corresponding larger value for RCOMP. RFB2 should be large enough to keep the total divider power dissipation small. A 49.9 kΩ in series with 681 Ω was chosen for high-side feedback resistors in this example, which results in a RFB1 value of 5.62 kΩ for 12 V output.

8.2.2.13 Soft-Start Capacitor CSS

The soft-start time (tSS) is the time required for the output voltage set point to reach the target voltage from the input voltage. The soft-start time is not only proportional to the soft-start capacitor, but also depends on the input voltage. With 0.1 µF for CSS, the soft-start time is calculated as follows:

8.2.2.14 Restart Capacitor CRES

The restart capacitor determines the restart delay time tRD and hiccup mode off time tRES (see Figure 27). tRD should be greater than tSS(MAX). The minimum required value of CRES can be calculated at the low input voltage as follows:

A standard value of 0.18 µF is selected for CRES.

8.2.2.15 Low-Side Power Switch QL

Breaking down the various losses is one way to compare the relative efficiencies of different N-channel MOSFET devices. Losses in the low-side N-channel MOSFET device can be separated into conduction loss and switching loss.

Low-side conduction loss is approximated calculated as follows:

Where D is the duty cycle and the factor of 1.3 accounts for the increase in the N-channel MOSFET device on-resistance due to heating. Alternatively, the factor of 1.3 can be eliminated and the high temperature on-resistance of the N-channel MOSFET device can be estimated using the RDS(ON) vs temperature curves in the N-channel MOSFET datasheet.

Switching loss occurs during the brief transition period as the low-side N-channel MOSFET device turns on and off. During the transition period both current and voltage are present in the channel of the N-channel MOSFET device. The low-side switching loss is approximated as follows:

tR and tF are the rise and fall times of the low-side N-channel MOSFET device. The rise and fall times are usually mentioned in the N-channel MOSFET datasheet or can be empirically observed with an oscilloscope.

An additional Schottky diode can be placed in parallel with the low-side N-channel MOSFET switch, with short connections to the source and drain in order to minimize negative voltage spikes at the SW node.

8.2.2.16 High-Side Power Switch QH and Additional Parallel Schottky Diode

Losses in the high-side N-channel MOSFET device can be separated into conduction loss, dead-time loss and reverse recovery loss. Switching loss is calculated only for the low-side N-channel MOSFET device. Switching loss in the high-side N-channel MOSFET device is negligible because the body diode of the high-side N-channel MOSFET device turns on before and after the high-side N-channel MOSFET switches.

High-side conduction loss is approximated as follows:

Dead-time loss is approximated as follows:

where

- VD is the forward voltage drop of the high-side N-channel MOSFET body diode.

Reverse recovery characteristics of the high-side N-channel MOSFET strongly influences efficiency, especially when the output voltage is high. Smaller reverse recovery charge helps to increase the efficiency while also minimizing switching noise.

Reverse recovery loss is approximated as follows:

where

- QRR is the reverse recovery charge of the high-side N-channel MOSFET body diode.

An additional Schottky diode can be placed in parallel with the high-side switch to improve efficiency. Usually, the power rating of this parallel Schottky diode can be less than the high-side switch ratings because the diode conducts only during dead-times. The power rating of the parallel diode should be equivalent or higher than high-side switch ratings if bypass operation is required, hiccup mode operation is required or a heavy load exists before the controller begins switching.

8.2.2.17 Snubber Components

A resistor-capacitor snubber network across the high-side N-channel MOSFET device reduces ringing and spikes at the switching node. Excessive ringing and spikes can cause erratic operation and can couple noise to the output. Selecting the values for the snubber is best accomplished through empirical methods. First, make sure the lead lengths for the snubber connections are very short. Start with a resistor value between 5 and 50 Ω. Increasing the value of the snubber capacitor results in more damping, but this also increases snubber losses. Select a minimum value for the snubber capacitor that provides adequate damping of the spikes on the switch waveform at heavy load. A snubber may not be necessary with an optimized layout.

8.2.2.18 Disconnect Switch QD Selection

The N-channel MOSFET disconnection switch (QD) should be selected based on the following criteria:

- The BVDSS rating must be greater than the maximum input voltage, plus ringing and transients.

- The safe operating area (SOA) and the thermal properties should be considered. If required, limit the rise time of the input power supply or the maximum start-up input voltage.

- Absolute maximum rating of VGS should be greater than 18 V.

- If the minimum VIN voltage is less than 6.5 V, a logic level MOSFET should be used.

- The plateau voltage during inrush current limiting is recommended to be less than VGS-DET. If the VPLATEAU is greater than VGS-DET, boost switching might start before finishing the inrush limiting.

8.2.2.19 Freewheeling Diode DF Selection

If QD turns off quickly by the circuit breaker function, the inductor current continues flowing through a freewheeling diode (DF). DF should have enough capability to handle 150 mV/RS of peak current during inductor current decay and the voltage rating must be greater than the maximum input voltage, plus ringing and transients. The inductor current decay time is calculated from Equation 42.

8.2.2.20 Loop Compensation Components CCOMP, RCOMP, CHF

RCOMP, CCOMP and CHF configure the error amplifier gain and phase characteristics to produce a stable voltage loop. For a quick start, follow the 4 steps listed below:

- Select fCROSS

- Determine required RCOMP

- Determine CCOMP to cancel load pole. Place the error amplifier zero at twice the load pole frequency. Knowing RCOMP, CCOMP is calculated as follows:

- Determine CHF to cancel the ESR zero.

Select the cross over frequency (fCROSS) at one fourth of the RHP zero or one tenth of the switching frequency whichever is lower.

A 13.4 kHz crossover frequency is selected. RHP zero at minimum input voltage should be considered if the input voltage range is wide.

Knowing fCROSS, RCOMP is calculated as follows:

A standard value of 200 kΩ is selected for RCOMP

A standard value of 8.2 nF is selected for CCOMP

Knowing RCOMP, RESR and CCOMP, CHF is calculated as follows:

A standard value of 100 pF is selected for CHF

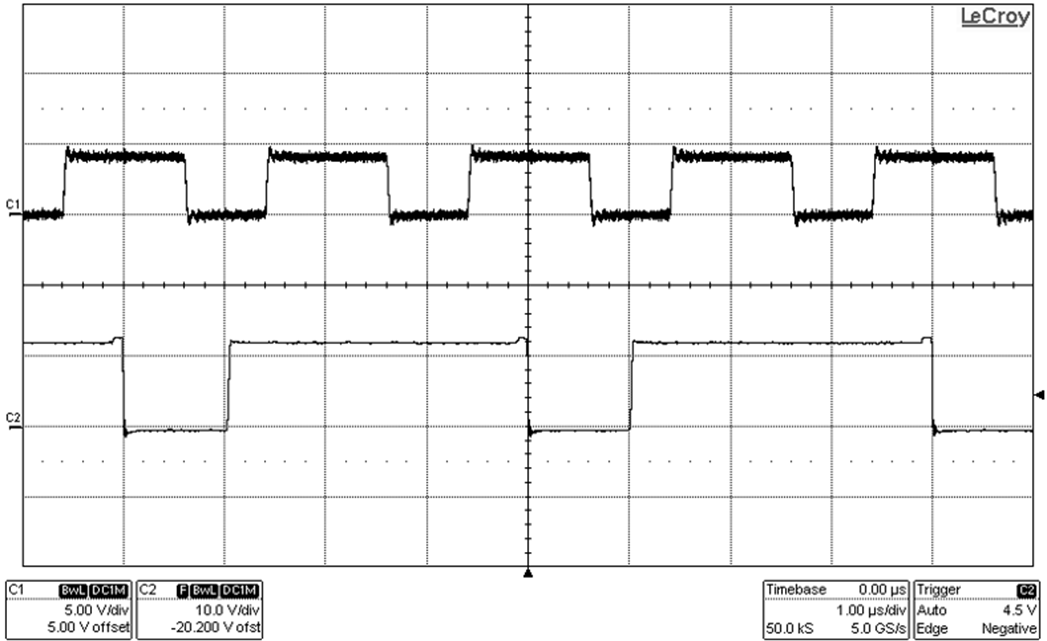

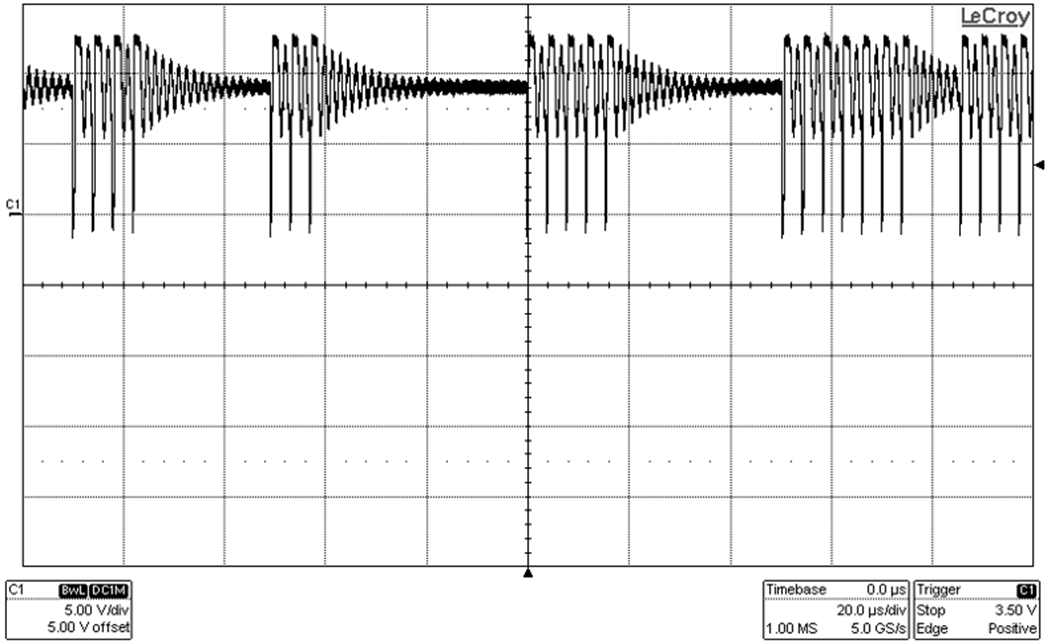

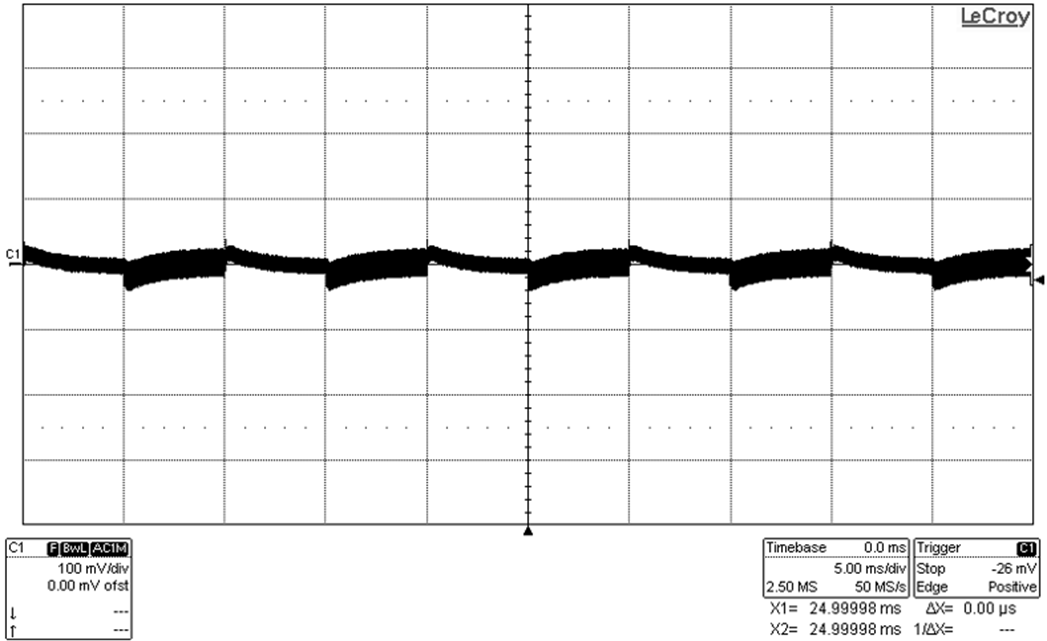

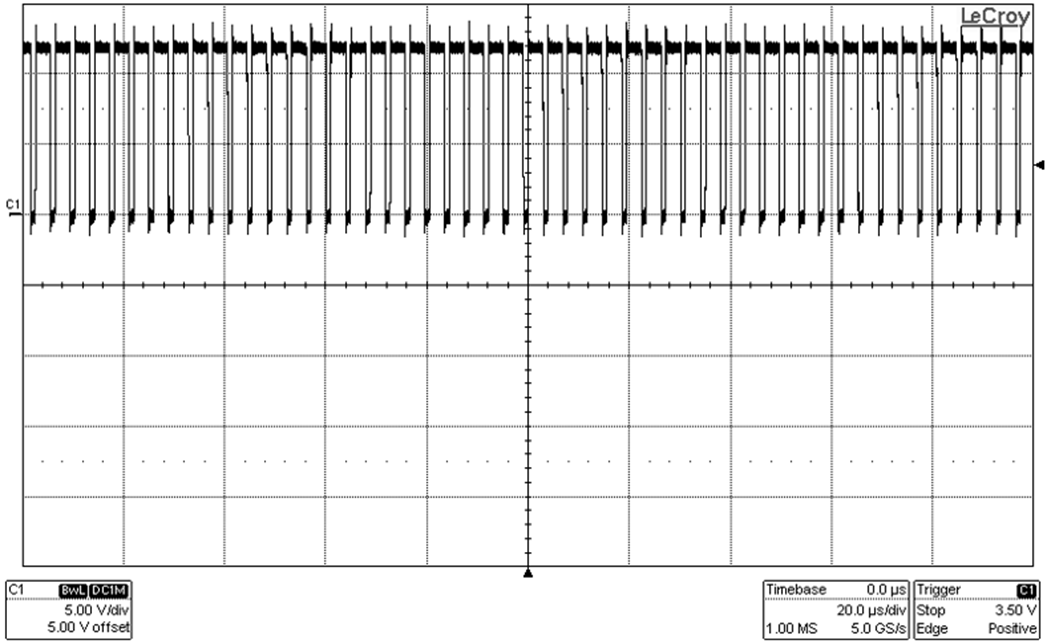

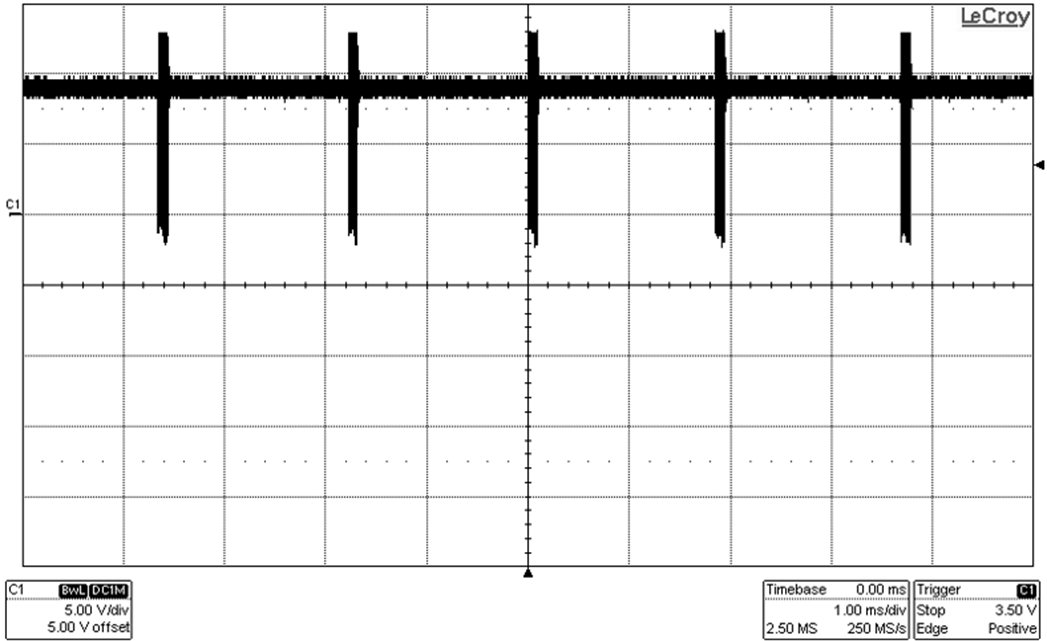

8.2.3 Application Curves

| C1:SW, VSUPPLY = 9 V, ILOAD = 0 A |