ZHCSTP1F August 2000 – February 2024 LMC6492 , LMC6494

PRODUCTION DATA

6.1.4 容性负载容差

所有轨到轨输出摆幅运算放大器在输出级中都具有电压增益。该积分器级中通常包含一个补偿电容器。主极点的频率位置受放大器上的阻性负载的影响。容性负载驱动能力可以通过使用与容性负载并联的适当阻性负载来优化(参阅典型曲线)。

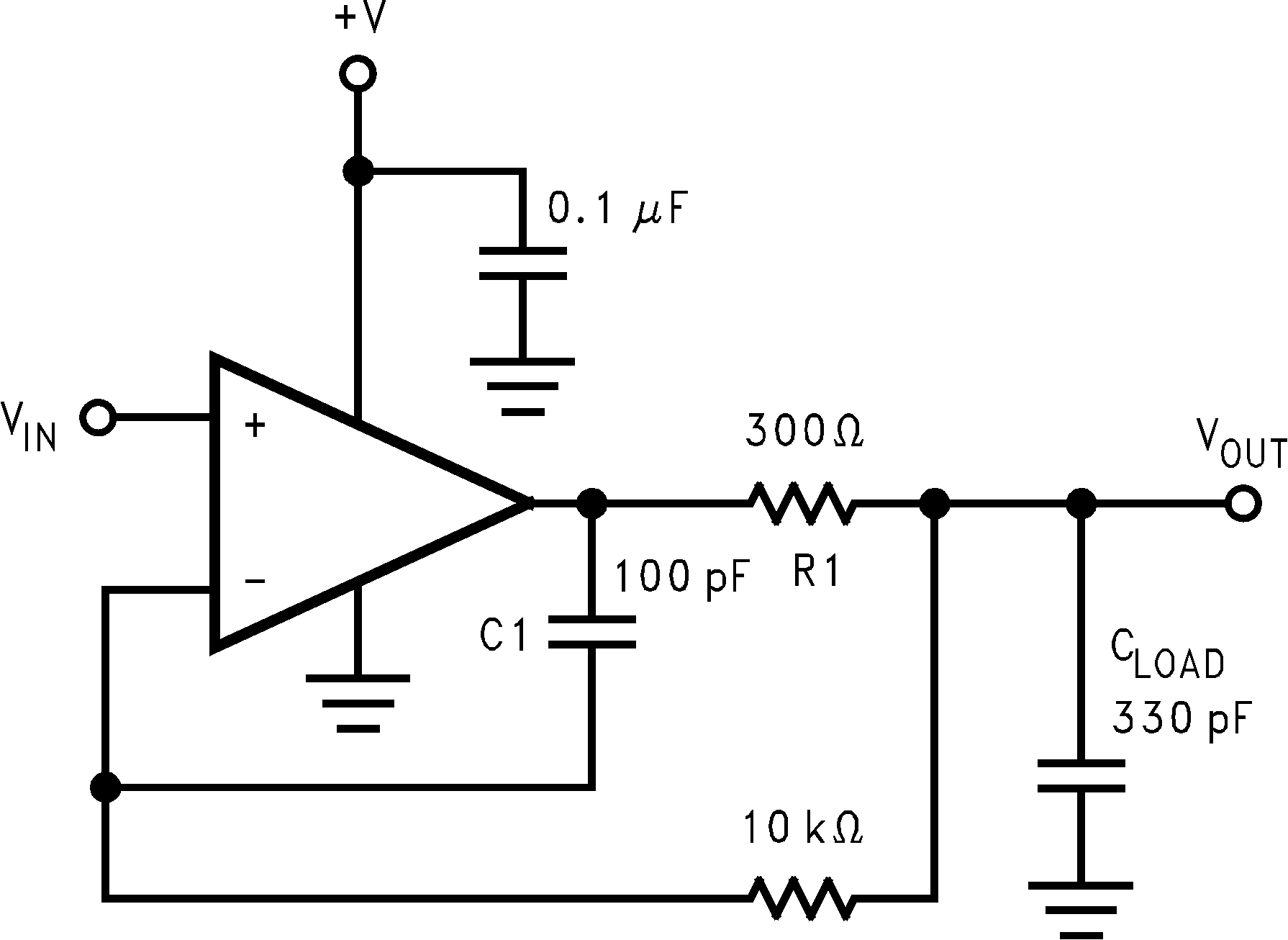

直接容性负载可减小许多运算放大器的相位裕度。运算放大器输出阻抗和容性负载的组合形成反馈环路中的一个极点。图 6-6 中展示了 LMC649x 的开环输出阻抗。该极点会在放大器的单位增益交叉频率处引起相位滞后,从而导致振荡或欠阻尼的脉冲响应。通过使用一些外部元件,运算放大器可以轻松间接驱动容性负载,如图 6-7 中所示。

图 6-6 LMC649x 开环输出阻抗

图 6-6 LMC649x 开环输出阻抗 图 6-7 LMC649x 同相放大器,在经过补偿后可处理容性负载

图 6-7 LMC649x 同相放大器,在经过补偿后可处理容性负载