ZHCSCR0A August 2014 – December 2014 LMH3401

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

-

10Application and Implementation

- 10.1 Application Information

- 10.2 Typical Application

- 10.3 Do's and Don'ts

- 11Power-Supply Recommendations

- 12Layout

- 13器件和文档支持

- 14机械封装和可订购信息

12 Layout

12.1 Layout Guidelines

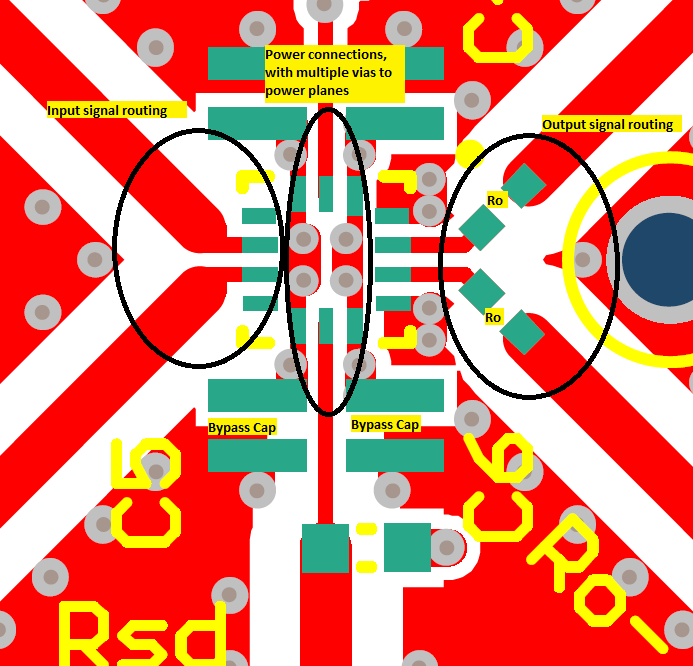

With 7 GHz of bandwidth, layout for the LMH3401 is critical and nothing can be neglected. In order to simplify board design, the LMH3401 has on-chip resistors that reduce the impact of off-chip capacitance. For this reason, TI recommends that the ground layer below the LMH3401 not be cut. The recommendation not to cut the ground plane under the amplifier input and output pins is different than many other high-speed amplifiers, but the reason is that parasitic inductance is more harmful to the LMH3401 performance than parasitic capacitance. By leaving the ground layer under the device intact, parasitic inductance of the output and power traces is minimized. The DUT portion of the evaluation board layout is illustrated in Figure 71 and Figure 72.

The EVM uses long edge capacitors for the decoupling capacitors, which reduces series resistance and increases the resonant frequency. Vias are also placed to the power planes before the bypass capacitors. Although not evident in the top layer, two vias are used at the capacitor in addition to the two vias underneath the device.

The output matching resistors are 0402 size and are placed very close to the amplifier output pins, which reduces both parasitic inductance and capacitance. The use of 0603 output matching resistors produces a measurable decrease in bandwidth.

When the signal is on a 50-Ω controlled impedance transmission line, the layout then becomes much less critical. The transition from the 50-Ω transmission line to the amplifier pins is the most critical area.

The CM pin also requires a bypass capacitor. Place this capacitor near the device. Refer to the user guide LMH3401EVM Evaluation Module (SBOU124) for more details on board layout and design.

12.2 Layout Example

Figure 71. Layout Example

Figure 71. Layout Example

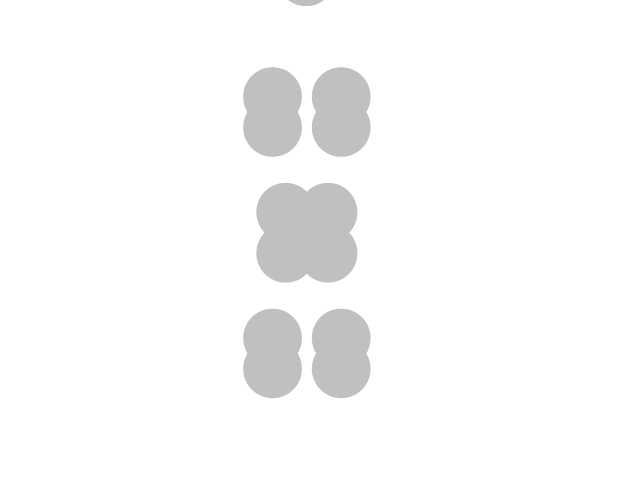

Figure 72. EVM Layout Ground Layer Showing Solid Ground Plane

Figure 72. EVM Layout Ground Layer Showing Solid Ground Plane