SNOSD58 June 2017 LMH6702-MIL

PRODUCTION DATA.

10 Layout

10.1 Layout Guidelines

Generally, a good high frequency layout will keep power supply and ground traces away from the inverting input and output pins. Parasitic capacitances on these nodes to ground will cause frequency response peaking and possible circuit oscillations. See Frequent Faux Pas in Applying Wideband Current Feedback Amplifiers, Application Note OA-15 (SNOA367). Texas Instruments suggests the following evaluation boards as a guide for high frequency layout and as an aid in device testing and characterization. See Table 1 for details.

The LMH6702-MIL evaluation board(s) is a good example of high frequency layout techniques as a reference. General high-speed, signal-path layout suggestions include:

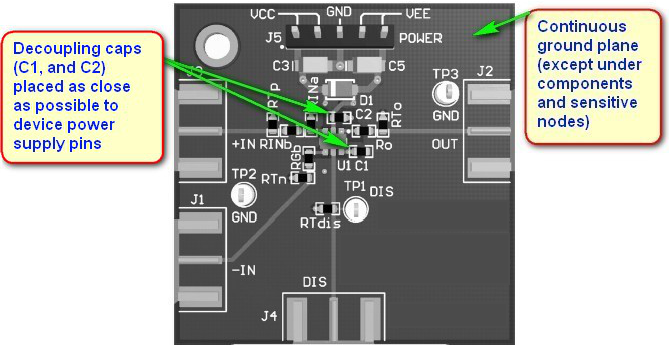

- Continuous ground planes are preferred for signal routing with matched impedance traces for longer runs. However, open up both ground and power planes around the capacitive sensitive input and output device pins as shown in Figure 28. After the signal is sent into a resistor, parasitic capacitance becomes more of a bandlimiting issue and less of a stability issue.

- Use good, high-frequency decoupling capacitors (0.1 μF) on the ground plane at the device power pins as shown in Figure 28. Higher value capacitors (2.2 μF) are required, but may be placed further from the device power pins and shared among devices. For best high-frequency decoupling, consider X2Y supply-decoupling capacitors that offer a much higher self-resonance frequency over standard capacitors.

- When using differential signal routing over any appreciable distance, use microstrip layout techniques with matched impedance traces.

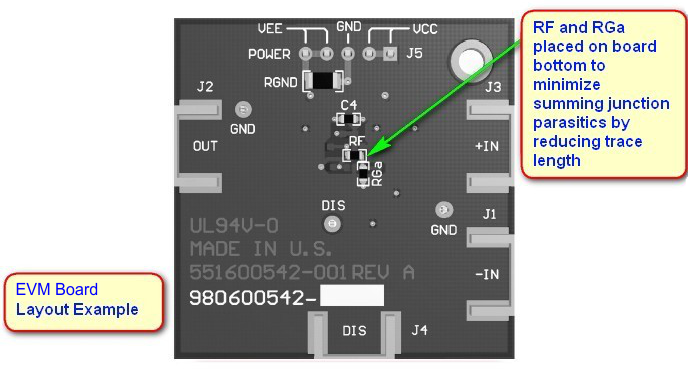

- The input summing junction is very sensitive to parasitic capacitance. Connect any Rf, and Rg elements into the summing junction with minimal trace length to the device pin side of the resistor, as shown in Figure 29. The other side of these elements can have more trace length if needed to the source or to ground.

10.2 Layout Example

Figure 28. LMH6702-MIL Evaluation Board Layer 1

Figure 28. LMH6702-MIL Evaluation Board Layer 1

Figure 29. LMH6702-MIL Evaluation Board Layer 2

Figure 29. LMH6702-MIL Evaluation Board Layer 2

Table 1. Evaluation Board Comparison

| DEVICE | PACKAGE | EVALUATION BOARD PART NUMBER |

|---|---|---|

| LMH6702-MILMF | SOT-23 | LMH730216 |

| LMH6702-MILMA | SOIC | LMH730227 |