ZHCSDM7B February 2012 – December 2014 LMP8646

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

10 Layout

10.1 Layout Guidelines

- In a 4-layer board design, the recommended layer stack order from top to bottom is: signal, power, ground, and signal

- Bypass capacitors should be placed in close proximity to the V+ pin

- The trace for pins +IN and -IN should be big enough to handle the current running through it.

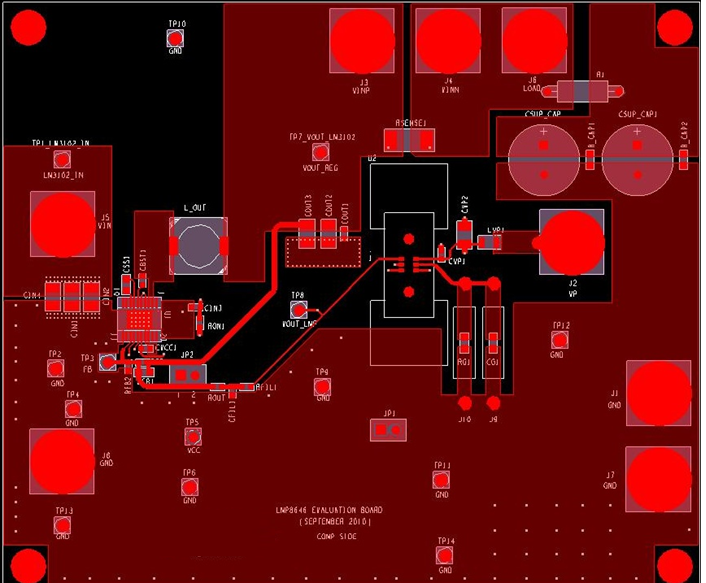

10.2 Layout Example

Figure 34. LMP8646 Evaluation Board Layout

Figure 34. LMP8646 Evaluation Board Layout