ZHCSEK3G December 2015 – August 2022 LMX2592

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

-

8 Application and Implementation

- 8.1

Application Information

- 8.1.1 Optimization of Spurs

- 8.1.2 Configuring the Input Signal Path

- 8.1.3 Input Pin Configuration

- 8.1.4 Using the OSCin Doubler

- 8.1.5 Using the Input Signal Path Components

- 8.1.6 Designing for Output Power

- 8.1.7 Current Consumption Management

- 8.1.8 Decreasing Lock Time

- 8.1.9 Modeling and Understanding PLL FOM and Flicker Noise

- 8.1.10 External Loop Filter

- 8.2 Typical Application

- 8.3 Power Supply Recommendations

- 8.4 Layout

- 8.1

Application Information

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- RHA|40

散热焊盘机械数据 (封装 | 引脚)

- RHA|40

订购信息

8.1.5.1 Moving Phase Detector Frequency

Engaging the multiplier in the reference path allows more flexibility in setting the PFD frequency. One example use case of this is if Fvco % Fpd is the dominant spur. This method can move the PFD frequency and thus the Fvco % Fpd.

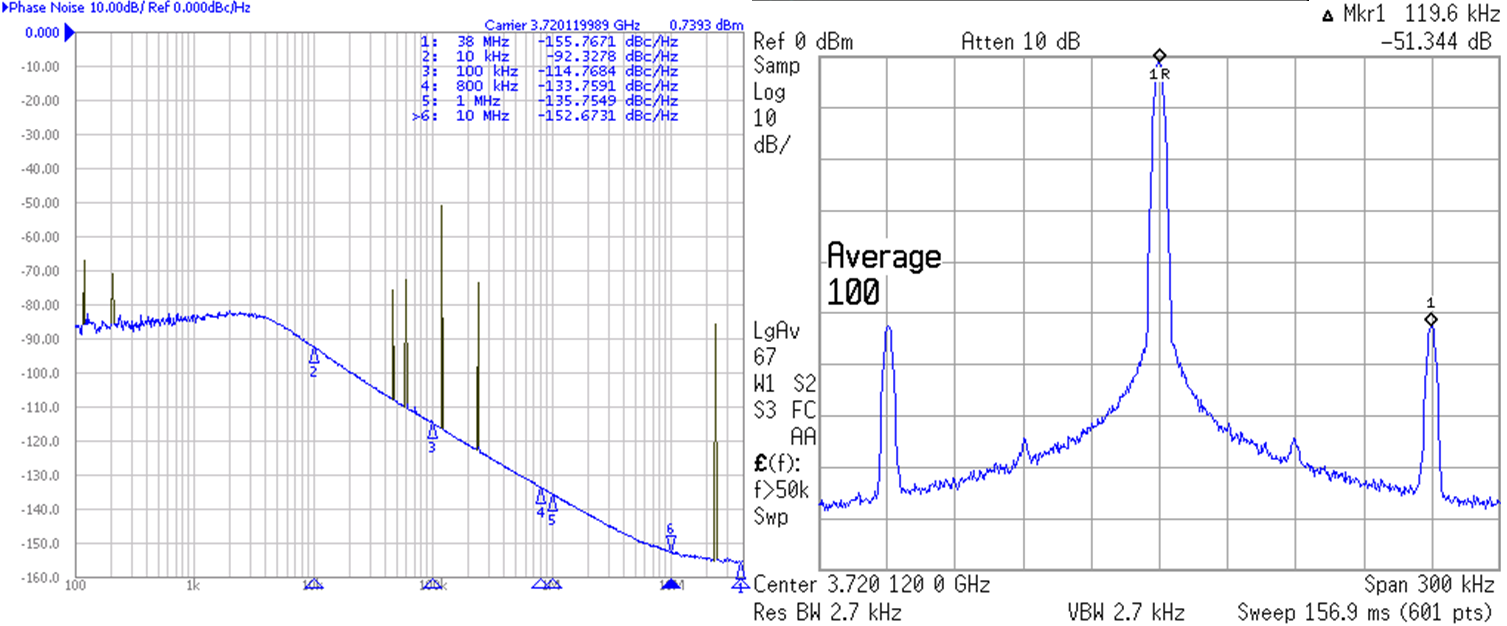

Example: Fvco = 3720.12 MHz, Fosc = 300 MHz, Pre-R divider = 5, Fpd = 60 MHz, Fvco%Fosc = 120.12 MHz (Far out), Fvco%Fpd = 120 kHz (dominant). There is a Fvco%Fpd spur at 120 kHz (refer to Figure 8-5).

Figure 8-5 Fvco % Fpd Spur

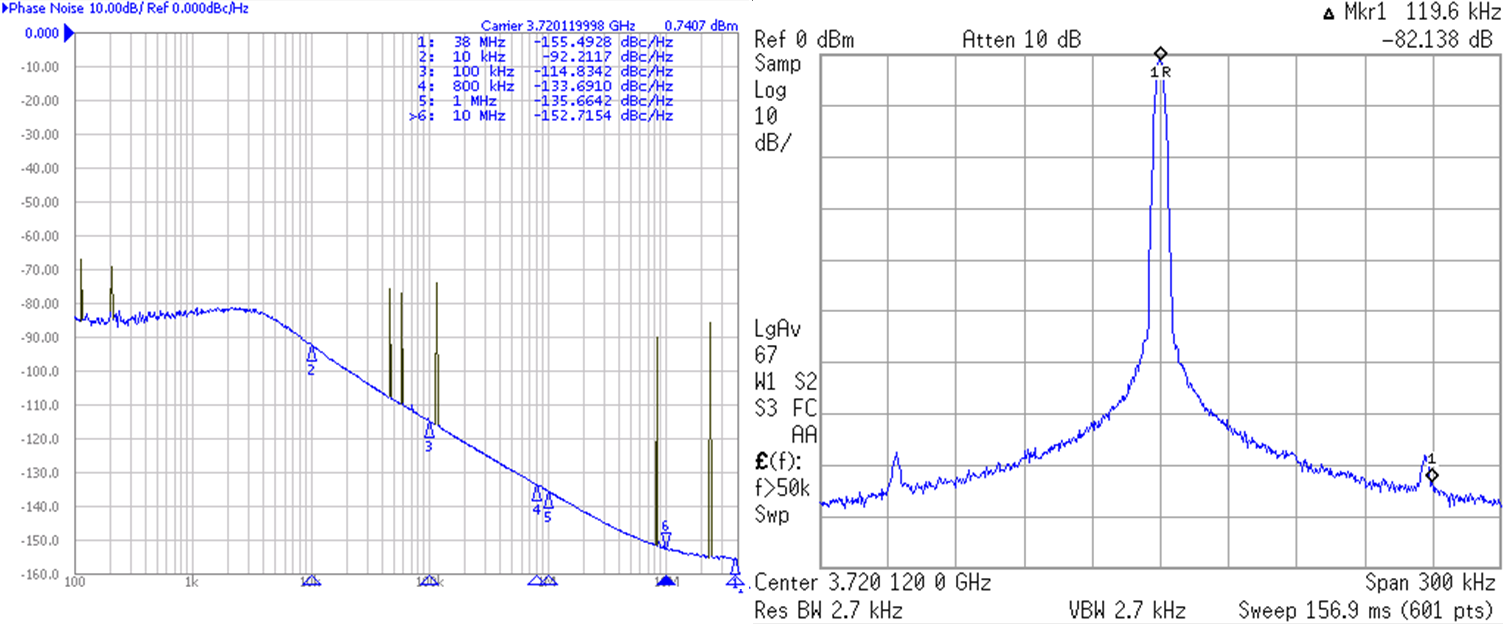

Figure 8-5 Fvco % Fpd SpurThen second case, using divider and multiplier, is Fpd = 53.57 MHz away from 120-kHz spur. Fvco = 3720.12MHz, Fosc = 300MHz, Pre-R divider = 7, Multiplier = 5, Post-R divider = 4, Fpd = 53.57 MHz, Fvco%Fosc = 120.12 MHz (Far out). Fvco % Fpd = 23.79 MHz (far out). There is a 20–dB reduction for the Fvco % Fpd spur at 120 kHz (refer to Figure 8-6).

Figure 8-6 Moving Away From Fvco % Fpd

Spur

Figure 8-6 Moving Away From Fvco % Fpd

Spur