SNOS405B November 1999 – May 2017 MAX660

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

8 Detailed Description

8.1 Overview

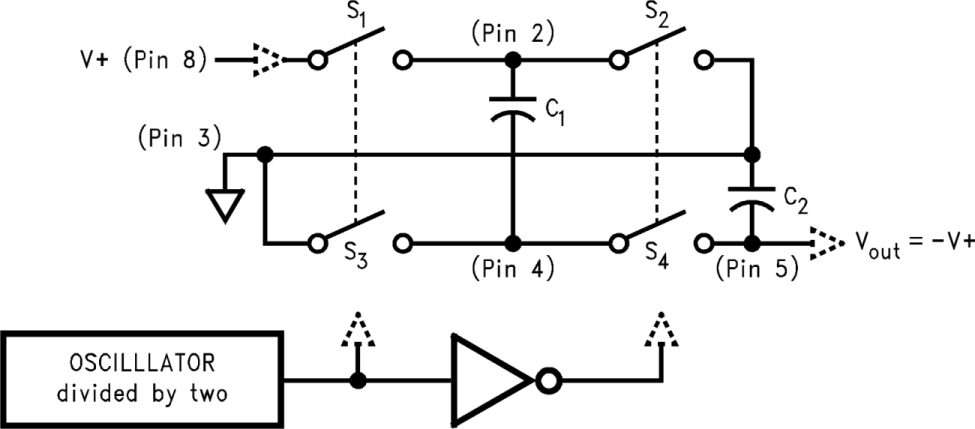

The MAX660 contains four large CMOS switches which are switched in a sequence to invert the input supply voltage. Energy transfer and storage are provided by external capacitors. Figure 13 shows the voltage conversion scheme. When S1 and S3 are closed, C1 charges to the supply voltage V+. During this time interval switches S2 and S4 are open. In the second time interval, S1 and S3 are open and S2 and S4 are closed, C1 is charging C2. After a number of cycles, the voltage across C2 is pumped to V+. Because the anode of C2 is connected to ground, the output at the cathode of C2 equals −(V+) assuming no load on C2, no loss in the switches, and no ESR in the capacitors. In reality, the charge transfer efficiency depends on the switching frequency, the on-resistance of the switches, and the ESR of the capacitors.

Figure 13. Voltage Inverting Principle

Figure 13. Voltage Inverting Principle

8.2 Functional Block Diagram

8.3 Feature Description

The internal oscillator frequency can be selected using the frequency control (FC) pin. When FC is open, the oscillator frequency is 10 kHz; when FC is connected to V+, the frequency increases to 80 kHz. A higher oscillator frequency allows use of smaller capacitors for equivalent output resistance and ripple, but increases the typical supply current from 0.12 mA to 1 mA. The oscillator frequency can be lowered by adding an external capacitor between OSC and GND. (See Typical Characteristics.) Also, in the inverter mode, an external clock that swings within 100 mV of V+ and GND can be used to drive OSC. Any CMOS logic gate is suitable for driving OSC. LV must be grounded when driving OSC. The maximum external clock frequency is limited to 150 kHz.

The switching frequency of the converter (also called the charge-pump frequency) is half of the oscillator frequency.

NOTE

OSC cannot be driven by an external clock in the voltage-doubling mode.

Table 1. MAX660 Oscillator Frequency Selection

| FC | OSC | OSCILLATOR |

|---|---|---|

| Open | Open | 10 kHz |

| V+ | Open | 80 kHz |

| Open or V+ | External capacitor | See Typical Characteristics |

| N/A | External clock (inverter mode only) | External clock frequency |

8.4 Device Functional Modes

When V+ is applied to the MAX660, the device becomes enabled and operates in whichever configuration the device is placed (inverter, doubler, etc.).