ZHCSPQ7A december 2022 – april 2023 MCT8315A

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Output Stage

- 7.3.2 Device Interface

- 7.3.3 Step-Down Mixed-Mode Buck Regulator

- 7.3.4 AVDD Linear Voltage Regulator

- 7.3.5 Charge Pump

- 7.3.6 Slew Rate Control

- 7.3.7 Cross Conduction (Dead Time)

- 7.3.8 Speed Control

- 7.3.9 Starting the Motor Under Different Initial Conditions

- 7.3.10 Motor Start Sequence (MSS)

- 7.3.11 Closed Loop Operation

- 7.3.12 Speed Loop

- 7.3.13 Input Power Regulation

- 7.3.14 Anti-Voltage Surge (AVS)

- 7.3.15 Output PWM Switching Frequency

- 7.3.16 Fast Start-up (< 50 ms)

- 7.3.17 Fast Deceleration

- 7.3.18 Active Demagnetization

- 7.3.19 Motor Stop Options

- 7.3.20 FG Configuration

- 7.3.21

Protections

- 7.3.21.1 VM Supply Undervoltage Lockout

- 7.3.21.2 AVDD Undervoltage Lockout (AVDD_UV)

- 7.3.21.3 BUCK Undervoltage Lockout (BUCK_UV)

- 7.3.21.4 VCP Charge Pump Undervoltage Lockout (CPUV)

- 7.3.21.5 Overvoltage Protection (OVP)

- 7.3.21.6 Overcurrent Protection (OCP)

- 7.3.21.7 Buck Overcurrent Protection

- 7.3.21.8

Cycle-by-Cycle (CBC) Current Limit (CBC_ILIMIT)

- 7.3.21.8.1 CBC_ILIMIT Automatic Recovery next PWM Cycle (CBC_ILIMIT_MODE = 000xb)

- 7.3.21.8.2 CBC_ILIMIT Automatic Recovery Threshold Based (CBC_ILIMIT_MODE = 001xb)

- 7.3.21.8.3 CBC_ILIMIT Automatic Recovery after 'n' PWM Cycles (CBC_ILIMIT_MODE = 010xb)

- 7.3.21.8.4 CBC_ILIMIT Report Only (CBC_ILIMIT_MODE = 0110b)

- 7.3.21.8.5 CBC_ILIMIT Disabled (CBC_ILIMIT_MODE = 0111b or 1xxxb)

- 7.3.21.9 Lock Detection Current Limit (LOCK_ILIMIT)

- 7.3.21.10 Thermal Warning (OTW)

- 7.3.21.11 Thermal Shutdown (TSD)

- 7.3.21.12 Motor Lock (MTR_LCK)

- 7.3.21.13 Motor Lock Detection

- 7.3.21.14 SW VM Undervoltage Protection

- 7.3.21.15 SW VM Overvoltage Protection

- 7.3.21.16 IPD Faults

- 7.4 Device Functional Modes

- 7.5 External Interface

- 7.6 EEPROM access and I2C interface

- 7.7 EEPROM (Non-Volatile) Register Map

- 7.8 RAM (Volatile) Register Map

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

8.2.1.4 Setting the BEMF threshold

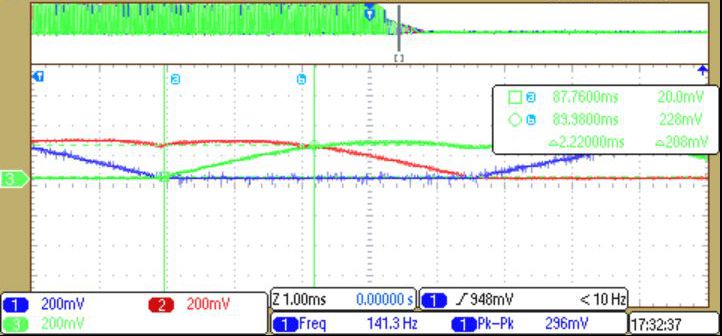

The BEMF_THRESHOLD1 and BEMF_THRESHOLD2 values used for commutation instant detection in MCT8315A can be computed from the motor phase voltage waveforms during coasting. For example, consider the three-phase voltage waveforms of a BLDC motor while coasting as in Figure 8-6. The motor phase voltage during coasting is the motor back-EMF.

Figure 8-6 Motor phase voltage during coasting

Figure 8-6 Motor phase voltage during coastingIn Figure 8-6, one floating phase voltage interval is denoted by the vertical markers on channel 3. The Vpeak (peak-peak back-EMF) on channel 3 is 208-mV and Tc (commutation interval) is 2.22-ms as denoted by the horizontal and vertical markers on channel 3. The digital equivalent counts for Vpeak and Tc are calculated as follows.

In MCT8315A, a 3-V analog input corresponds to 4095 counts(12-bit) and phase voltage is scaled down by 10x factor before ADC input; therfore, Vpeak of 208-mV corresponds to an ADC input of 20.8mV, which in turn equals 29 ADC counts. Assuming the PWM switching frequency is 25-kHz, one back-EMF sample is available every 40-μs. So, in a time interval of 2.22-ms, a total of 55 back-EMF samples are integrated. Therefore, the BEMF_THRESHOLD1 or BEMF_THRESHOLD2 value calculated as per Equation 7 is (½) * (29/2) * (55/2) = 199. Hence, in this example, BEMF_THRESHOLD1 and BEMF_THRESHOLD2 are set to 8h (corresponding to 200 which is the closest value to 199) for commutation instant detection using back-EMF integration method during fast start-up. The exact speed at which the Vpeak and Tc values are measured to calculate the BEMF_THRESHOLD1 and BEMF_THRESHOLD2 values is not critical (as long as there is sufficient resolution in digital counts) since the product (Vpeak * Tc) is, largely, a constant for a given BLDC motor.