ZHCSEE4D December 2015 – August 2021 OPA191 , OPA2191 , OPA4191

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 引脚配置和功能

- 6 规格

- 7 参数测量信息

- 8 详细说明

- 9 应用和实现

- 10电源相关建议

- 11布局

- 12器件和文档支持

- 13机械、封装和可订购信息

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

订购信息

6.9 典型特性

TA = 25°C,VS = ±18V,VCM = VS/2,RL = 10kΩ 且连接至 VS/2,且 CL = 100pF(除非另有说明)

表 6-1 图形表

| 说明 | 图表 |

|---|---|

| 失调电压产生分布 | 图 6-1,图 6-2,图 6-3,图 6-4,图 6-5,图 6-6 |

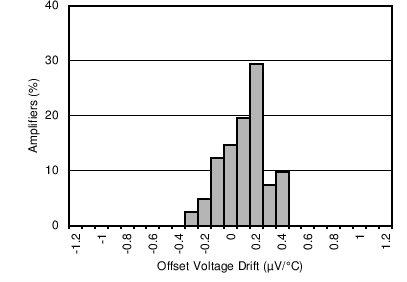

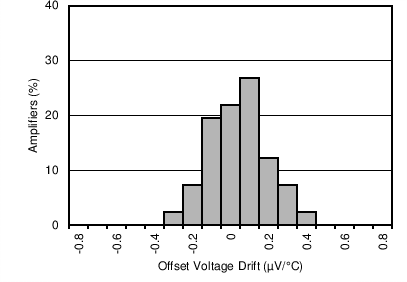

| 失调电压漂移分配 | 图 6-7、图 6-8, |

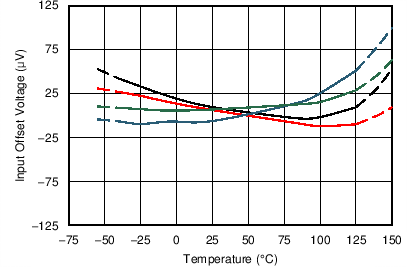

| 失调电压与温度间的关系 | 图 6-9、图 6-10 |

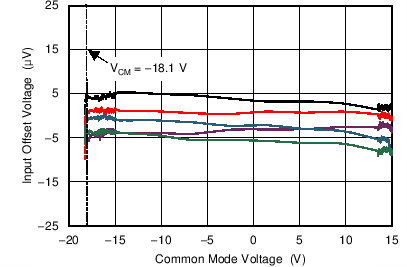

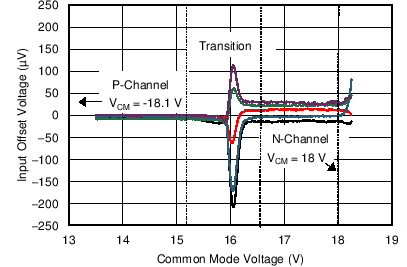

| 失调电压与共模电压间的关系 | 图 6-11、图 6-12 |

| 失调电压与电源间的关系 | 图 6-13 |

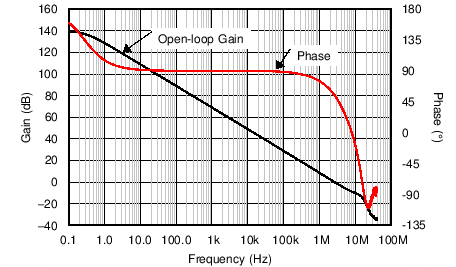

| 开环增益和相位与频率间的关系 | 图 6-14 |

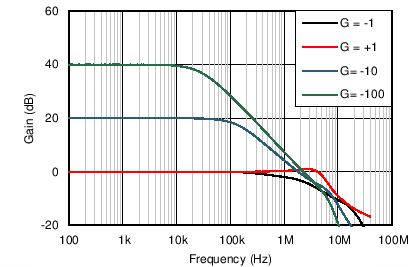

| 闭环增益和相位与频率间的关系 | 图 6-15 |

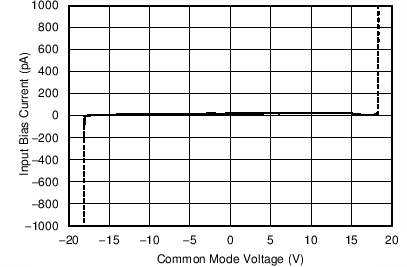

| 输入偏置电流与共模电压间的关系 | 图 6-16 |

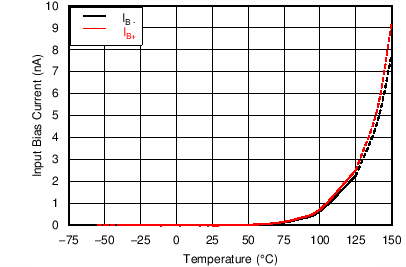

| 输入偏置电流与温度间的关系 | 图 6-17 |

| 输出电压摆幅与输出电流间的关系(最大电源电压) | 图 6-18、图 6-19 |

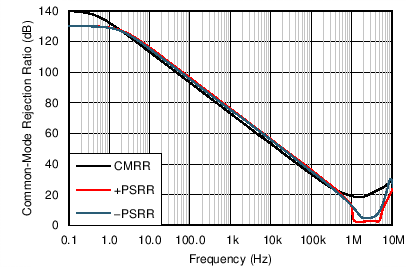

| CMRR 和 PSRR 与频率间的关系 | 图 6-20 |

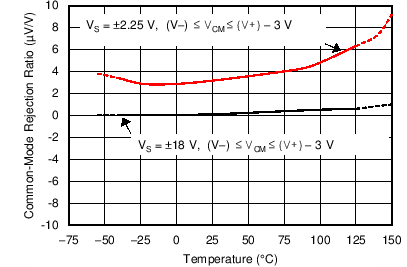

| CMRR 与温度间的关系 | 图 6-21 |

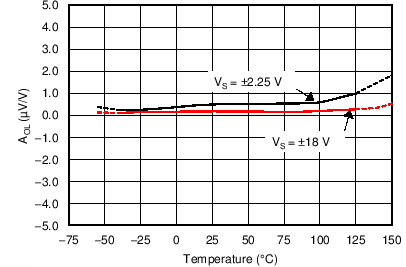

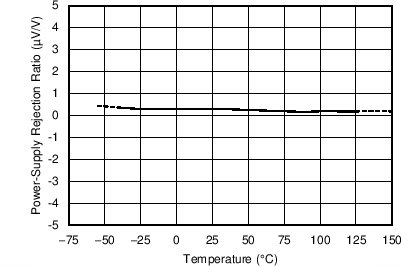

| PSRR 与温度间的关系 | 图 6-22 |

| 0.1Hz 至 10Hz 噪声 | 图 6-23 |

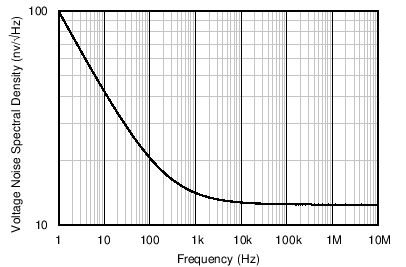

| 输入电压噪声频谱密度与频率间的关系 | 图 6-24 |

| THD+N 比与频率间的关系 | 图 6-25 |

| THD+N 与输出幅度间的关系 | 图 6-26 |

| 静态电流与电源电压间的关系 | 图 6-27 |

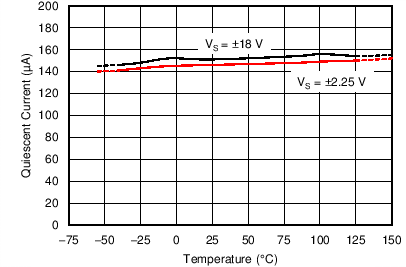

| 静态电流与温度间的关系 | 图 6-28 |

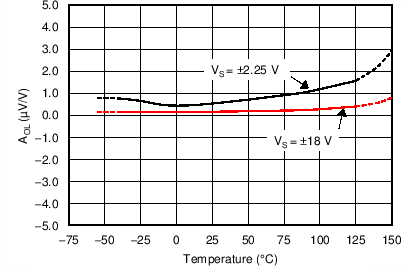

| 开环增益与温度间的关系 | 图 6-29、图 6-30 |

| 开环输出阻抗与频率间的关系 | 图 6-31 |

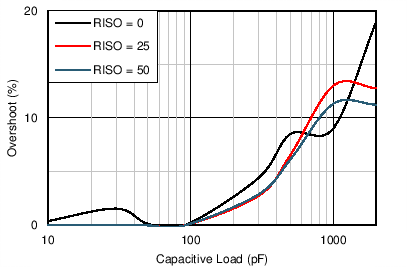

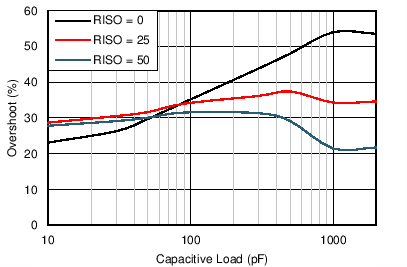

| 小信号过冲与容性负载间的关系(输出阶跃为 100mV) | 图 6-32,图 6-33 |

| 无相位反转 | 图 6-34 |

| 过载恢复 | 图 6-35 |

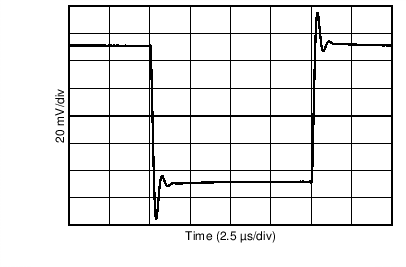

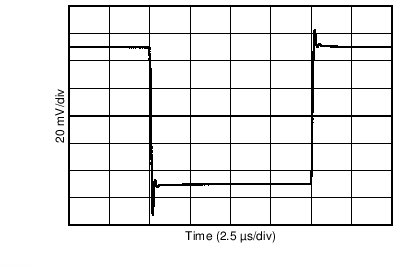

| 小信号阶跃响应 (100mV) | 图 6-36、图 6-37 |

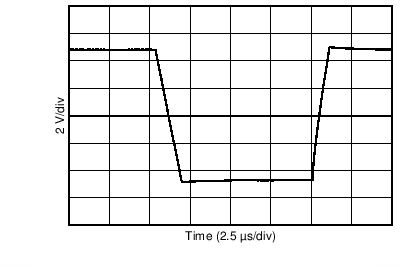

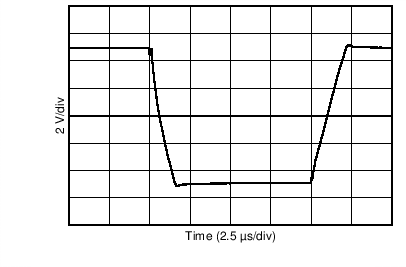

| 大信号阶跃响应 | 图 6-38, 图 6-39 |

| 建立时间 | 图 6-40、图 6-41、图 6-42、图 6-43 |

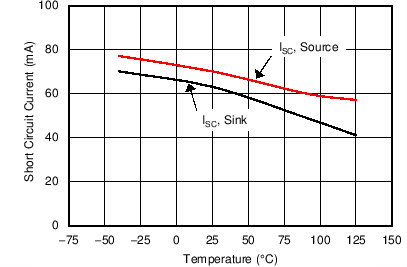

| 短路电流与温度间的关系 | 图 6-44 |

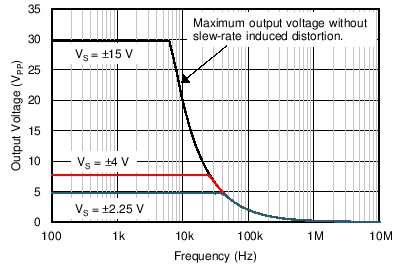

| 最大输出电压与频率间的关系 | 图 6-45 |

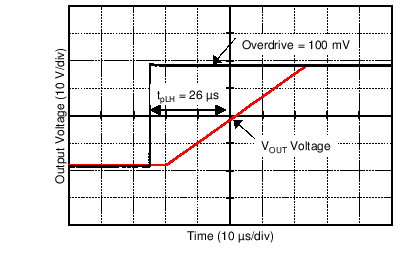

| 传播延迟上升沿 | 图 6-46 |

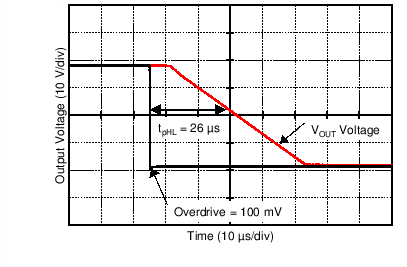

| 传播延迟下降沿 | 图 6-47 |

| TA = 25°C |

| TA = 85°C |

| TA = -25°C |

| TA = –40°C 至 +125°C,SOIC 封装 |

| 统计分布 |

| 30 个典型芯片 |

| 灌电流 |

与输出电流间的关系

| RL = 10kΩ |

与频率间的关系

| G = –1,100mV 输出阶跃 |

与容性负载间的关系

| VS = ±18V, G = –10V/V |

| G = –1,RL = 1kΩ,CL = 10pF |

| G = –1,RL = 1kΩ,CL = 10pF |

| 增益 = 1,2V 阶跃,下降,t = 0µs 时施加阶跃 |

| 增益 = 1,5V 阶跃,下降,t = 0µs 时施加阶跃 |

| TA = 125°C |

| TA = 0°C |

| TA = -40°C |

| TA = 0°C 至 85°C,SOIC 封装 |

| 4 个典型芯片 |

与频率间的关系

与共模电压间的关系

| 拉电流 |

与输出电流间的关系

| RL = 2kΩ |

| G = 1,100mV 输出阶跃 |

与容性负载间的关系(100mV 输出阶跃)

| G = 1,CL = 10pF |

| G = 1,CL = 10pF |

| 增益 = 1,2V 阶跃,上升,t = 0µs 时施加阶跃 |

| 增益 = 1,5V 阶跃,上升,t = 0µs 时施加阶跃 |