ZHCSFU2A December 2016 – January 2019 OPA4277-SP

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11器件和文档支持

- 12机械、封装和可订购信息

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

订购信息

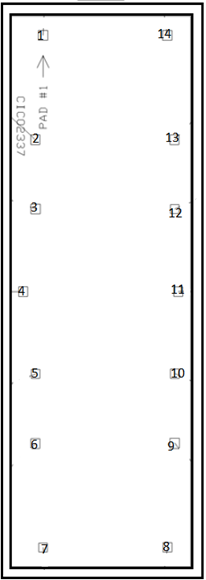

5.1 Bare Die Information

| DIE THICKNESS | BACKSIDE FINISH | BACKSIDE

POTENTIAL |

BOND PAD

METALLIZATION COMPOSITION |

BOND PAD

THICKNESS |

|---|---|---|---|---|

| 15 mils | Silicon with backgrind | Negative (lower) Power Supply | AlCu (0.5%) | 990 to 1210 nm |

Bond Pad Coordinates in Microns(1)

| PAD | I/O | DESCRIPTION | X MIN | Y MIN | X MAX | Y MAX | |

|---|---|---|---|---|---|---|---|

| NO. | NAME | ||||||

| 1 | OUT A | O | Output channel A. | 1791.042 | 7290.340 | 1901.751 | 7401.049 |

| 2 | –IN A | I | Inverting input channel A. | 1701.719 | 6111.536 | 1807.397 | 6217.213 |

| 3 | +IN A | I | Noninverting input channel A. | 1701.719 | 5326.505 | 1812.429 | 5437.215 |

| 4 | V+ | — | Positive (higher) power supply. | 1555.784 | 4390.507 | 1661.461 | 4498.700 |

| 5 | +IN B | I | Noninverting input channel B. | 1706.752 | 3462.057 | 1807.397 | 3562.702 |

| 6 | –IN B | I | Inverting input channel B. | 1701.719 | 2671.994 | 1807.397 | 2777.671 |

| 7 | OUT B | O | Output channel B. | 1796.074 | 1498.222 | 1896.719 | 1598.867 |

| 8 | OUT C | O | Output channel C. | 3278.071 | 1498.222 | 3383.748 | 1603.900 |

| 9 | –IN C | I | Inverting input channel C. | 3362.361 | 2671.994 | 3473.071 | 2782.704 |

| 10 | +IN C | I | Noninverting input channel C. | 3367.393 | 3462.057 | 3473.071 | 3567.734 |

| 11 | V– | — | Negative (lower) power supply. | 3407.651 | 4391.765 | 3513.329 | 4497.442 |

| 12 | +IN D | I | Noninverting input channel D. | 3367.393 | 5331.537 | 3468.038 | 5432.182 |

| 13 | –IN D | I | Inverting input channel D. | 3362.361 | 6111.536 | 3468.038 | 6217.213 |

| 14 | OUT D | O | Output channel D. | 3273.039 | 7290.340 | 3383.748 | 7401.049 |

(1) Substrate must be biased to V–, negative (lower) power supply.