ZHCSPU5G December 1982 – October 2022 SN54HCT74 , SN74HCT74

PRODUCTION DATA

- 1 特性

- 2 说明

- 3 Revision History

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Power Supply Recommendations

- 9 Layout

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- J|14

- FK|20

- W|14

散热焊盘机械数据 (封装 | 引脚)

订购信息

2 说明

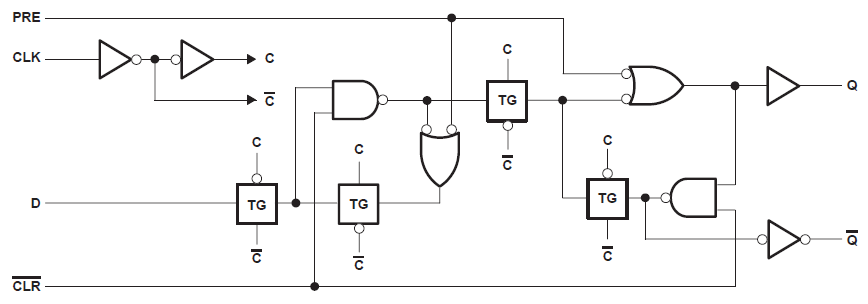

’HCT74 器件包含两个独立的 D 型正边沿触发式触发器。预设 (PRE) 或清零 (CLR) 输入端的低电平会设置或复位输出,不受其他输入端的电平的影响。当 PRE 和 CLR 处于非有效状态(高电平)时,满足设置时间要求的数据 (D) 输入端数据将在时钟 (CLK) 脉冲的正向边沿传输到输出端。时钟触发在一定电压电平下发生,与 CLK 的上升时间没有直接关系。经过保持时间间隔后,可以更改 D 输入端的数据而不影响输出端的电平。

器件信息

| 器件型号 | 封装(1) | 封装尺寸(标称值) |

|---|---|---|

| SN74HCT74D | SOIC (14) | 8.65mm × 3.90mm |

| SN74HCT74DB | SSOP (14) | 6.20mm × 5.30mm |

| SN74HCT74N | PDIP (14) | 19.31mm × 6.35mm |

| SN74HCT74NS | SO (14) | 10.20mm × 5.30mm |

| SN74HCT74PW | TSSOP (14) | 5.00mm × 4.40mm |

| SNJ54HCT74FK | LCCC (20) | 8.89mm × 8.45mm |

| SNJ54HCT74W | CFP (14) | 9.21mm × 6.29mm |

| SNJ54HCT74J | CDIP (14) | 19.55mm × 6.71mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购米6体育平台手机版_好二三四附录。

功能方框图

功能方框图