ZHCSJD7C April 2002 – February 2019 SN65LVDT14 , SN65LVDT41

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Receiver Electrical Characteristics

- 6.6 Driver Electrical Characteristics

- 6.7 Device Electrical Characteristics

- 6.8 Receiver Switching Characteristics

- 6.9 Driver Switching Characteristics

- 6.10 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

9.1.1 Extending a Serial Peripheral Interface Using LVDS Signaling Over Differential Transmission Cables

Serial Peripheral Interface (SPI) is found in numerous applications as the communication method between processor and peripheral devices using single-ended signals over short distances. However, there is increasing demand for longer range SPI communication on the same PCB or from board to board. As distance increases, external noise, and electromagnetic interference (EMI) with single-ended SPI signals becomes an issue. Furthermore, increased distance limits the data rate due to propagation delay, and affects the signal quality due to potential ground shift between boards. A long distance SPI communication is achievable with the help of LVDS. LVDS, as specified by the TIA/EIA-644-A standard, provides several benefits when compared to alternative long-distance signaling technologies: low EMI, high noise immunity, low power consumption, and inexpensive interconnect cables.

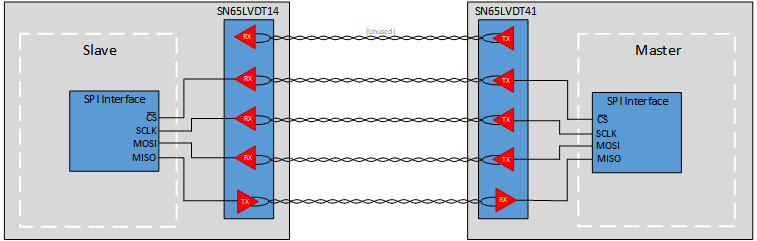

SPI operates in a master-slave architecture, with four unidirectional signal lines. The master supplies data named Master-Out-Slave-In (MOSI), a clock (SCK), and a optional Chip Select (CS) signal to control the operation of the system with multiple slave devices. The MOSI,SCLK, and CS signals are unidirectional from the master device to slave devices. The serial data from slave to master device is a unidirectional signal named Master-In-Slave-Out (MISO). The flow of data can be seen in Figure 18.

SN65LVDT14 and SN65LVDT41 provide the necessary LVDS drivers and receivers specifically targeted at implementing a long distance SPI application. It uses the unidrectional links for the MOSI, MISO, SCK, and CS signals and converts the single-ended data into a unidirectional LVDS links.SN65LVDT41 combines four LVDS line drivers with a single terminated LVDS line receiver in one package should be located at the SPI master device. SN65LVDT14 combines one LVDS line driver with four terminated LVDS line receivers in one package and should be located at the SPI device.

Figure 18. Typical SPI Application With LVDS

Figure 18. Typical SPI Application With LVDS Table 4. SPI Design Parameters

| Design Parameter | Example Value |

|---|---|

| Supply Voltage (VDD) | 3 to 3.6 V |

| Single-ended Input Voltage | 0 to VDD |

| SPI Data Rate | 0 to 10 Mbps |

| Interconnect Characteristic Impedance | 100 Ω |

| Number of LVDS Channel | 4 |

| Number of Transmitter Nodes | 3 |

| Number of Receiver Nodes | 1 |

| Ground shift between driver and receiver | ±1 V |