ZHCSS12D May 1998 – February 2024 SN74AHCT00Q-Q1

PRODUCTION DATA

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

- BQA|14

订购信息

3 说明

SN74AHCT00Q-Q1 以正逻辑执行布尔函数 Y =A • B或 Y =A+B。

封装信息

| 器件型号 | 封装(1) | 封装尺寸(2) | 封装尺寸(3) |

|---|---|---|---|

| SN74AHCT00Q-Q1 | D(SOIC,14) | 8.65mm x 6mm | 8.65mm x 3.90mm |

| PW(TSSOP,14) | 5.00mm × 6.4mm | 5.00mm × 4.40mm | |

| BQA(WQFN,14) | 3.00mm × 2.50mm | 3.00mm × 2.50mm |

(1) 更多相关信息,请参阅第 11 节。

(2) 封装尺寸(长 × 宽)为标称值,并包括引脚(如适用)。

(3) 封装尺寸(长 × 宽)为标称值,不包括引脚。

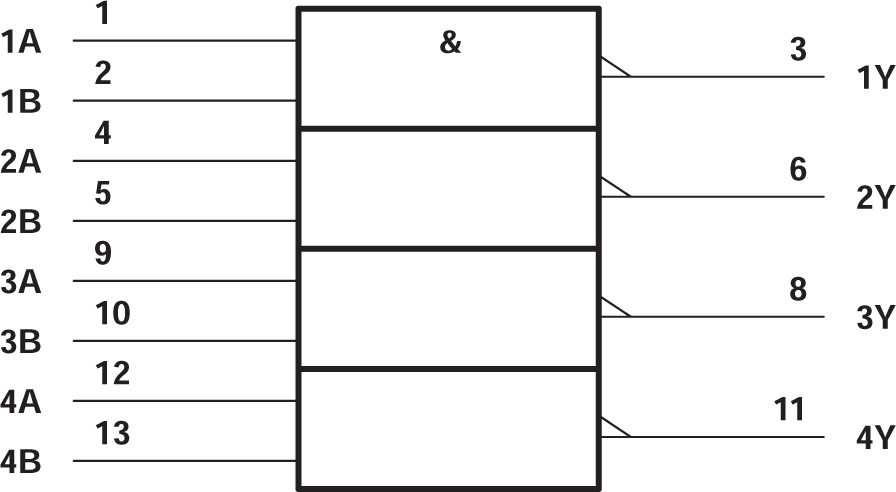

逻辑符号(1)

逻辑符号(1) 逻辑图(正逻辑)

逻辑图(正逻辑)†. 此符号符合 ANSI/IEEE 标准 91-1984 和 IEC 出版物 617-12。