ZHCSX54 October 2024 SN74LV4040B-EP

PRODUCTION DATA

3 说明

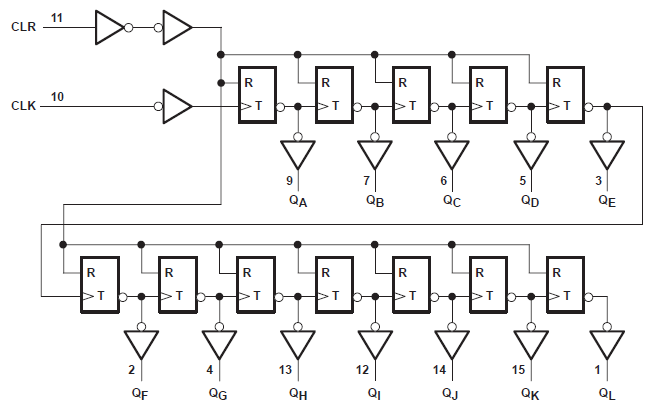

SN74LV4040B-EP 是 12 位异步二进制计数器,可从外部获得所有级的输出。将清零 (CLR) 输入设为高电平,以对计数器进行异步清零并将所有输出重置为低电平。在时钟 (CLK) 输入从高电平转换到低电平时,计数提前。应用包括延时电路、计数器控制和分频电路。

SN74LV4040B-EP 完全符合使用 Ioff 的部分断电应用的规范要求。Ioff 电路禁用输出,从而可防止其断电时破坏性电流从该器件回流。

- 有关更多信息,请参阅节 12

- 封装尺寸(长 × 宽)为标称值,并包括引脚(如适用)。

- 本体尺寸(长 × 宽)为标称值,不包括引脚。

图 3-1 简化逻辑图(正逻辑)

图 3-1 简化逻辑图(正逻辑)